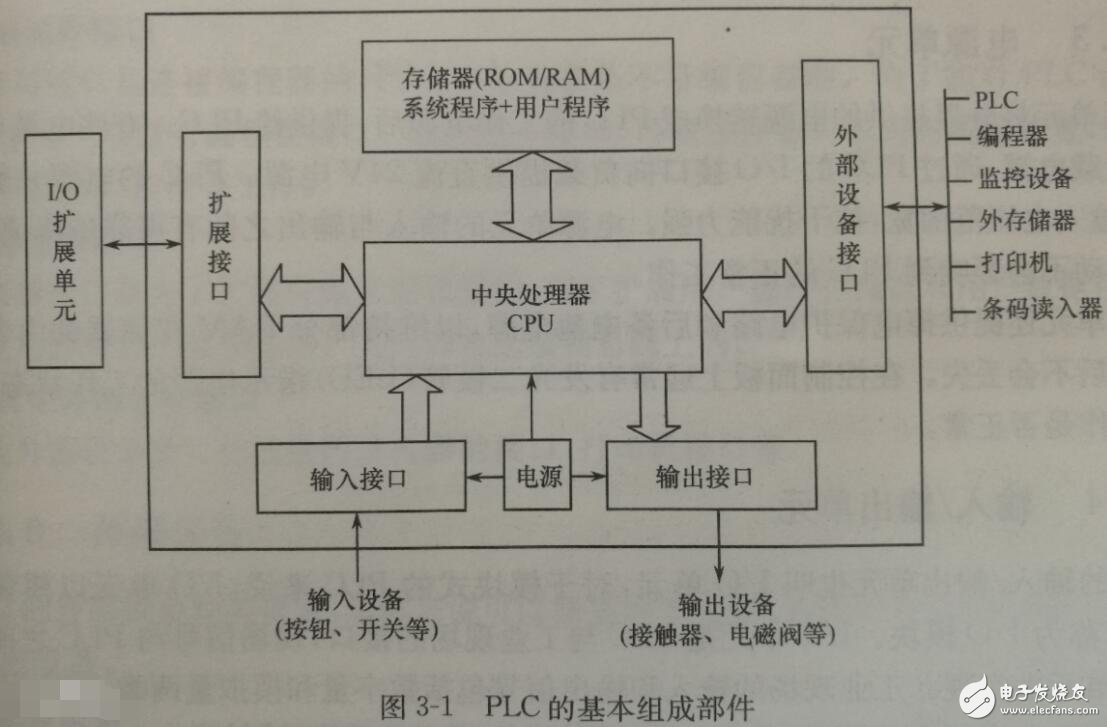

有時,微控制器本身可以完全滿足設計的所有功能要求。對于大多數嵌入式系統設計,編程良好、高度集成的嵌入式處理器是工程師可用的最具成本效益、最節能、??最快的解決方案。

當原始性能至關重要時,專用硬件中捕獲的邏輯可以實現最高水平的性能。例如,定序器可以比在軟件中實現的相同邏輯快一個數量級。

由于分立邏輯器件占用大量空間和功率,添加 FPGA 可能是一種可行的替代方案;在許多情況下,FPGA 和微控制器的組合是一個很好的解決方案。當微在 FPGA 的邏輯中實現時,更密集的解決方案是可能的。作為硬編碼宏,或在每個新設計中被替換和路由的軟宏,將整個微控制器吸收到 FPGA 內部不僅可以產生最高的密度,而且可以產生最大的靈活性,特別是如果你有足夠的勇氣去實際修改核心以提高性能。

本文著眼于在現成的 FPGA 中愉快地運行的微內核。這些可從各種來源獲得,包括開放式和封閉式、免費和 IP 許可的。

比原來的更好

遺留和專有架構都可以使用,并且各有優勢。舊版內核與舊版 micros 兼容,并提供熟悉的架構。然后,您公司生產的產品可以使用已經過測試和驗證的代碼。當需要下一代產品甚至新的改進模型時,組織良好且可靠的代碼庫的可重用性可以節省大量時間。

幾個流行的內核已經以原始邏輯形式用于各種 FPGA 系列,包括處理器,例如Microchip PIC、英特爾 8051、Atmel AVR、摩托羅拉 6502、英特爾 8080 和Zilog Z80 微控制器,僅舉幾例。

一個不那么明顯的優點是能夠改進初始架構。如果時間和資源允許,可以克服缺點,因為您可以修改設計。例如,非常流行的 8051 架構最初是采用順序架構引入的,每條指令需要 12 個時鐘周期。精確的遺留實現可以反映初始功能,或者可以實現更現代的風格,減少每條指令的時鐘周期數。

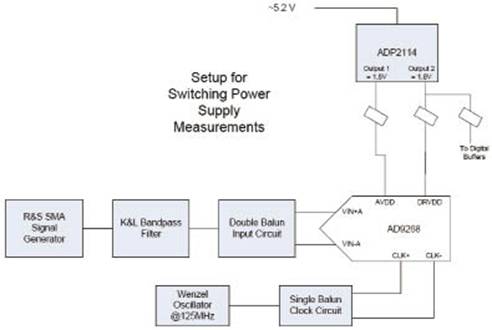

8051 的改進 IP 內核也可用于跨平臺開發。R8051XC2-BF 內核1可用于 ASIC 或Xilinx和Altera FPGA;它通過添加第二個數據指針(初始設計的一個缺點)和 JTAG 調試接口(圖 1)對初始設計進行了改進。

圖 1:傳統內核的商用實現通常會改進最初的分立設計。這個 8051 內核每條指令運行一個時鐘,并添加了 JTAG 和第二個數據指針。

ARM 內核

雖然許多設計可以使用 8 位內核,但現代功能可能需要更高的總線寬度來簡化處理。如果您正在處理 24 位寬的圖形數據,則單個 32 位傳輸比三個 8 位傳輸更有效。

也許最流行的 32 位架構是 ARM? Cortex?,毫無疑問,它已成為流行且得到良好支持的 FPGA 實現架構。從面積和功耗的角度來看,ARM Cortex 非常高效。眾多工具和開發套件以及用于外圍設備、內存管理、數學和 DSP 功能的開源代碼都很好地支持可擴展架構。

ARM 內核的一個很好的特性是它們不是某個 FPGA 制造商專有的,并且可以在不同制造商的設備上實現。這意味著隨著設計的發展或需求的變化,您不會被鎖定在一個供應商中。

另一個好處是架構從更簡單、功能更弱的Cortex M0擴展而來高達非常高端的多核A8和A9口味。這還帶來了經過軌道驗證的驅動程序和堆棧的好處,這些驅動程序和堆棧適用于 USB、以太網、Wi-Fi、ZigBee、藍牙等高端外圍設備。

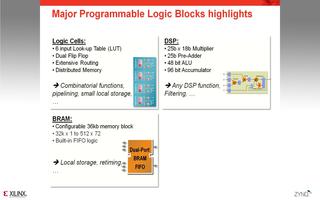

Xilinx 系列器件是嵌入式微核的大力支持者,ARM 架構也不例外。XC5VLX50-1FFG676C等部件是流行的 Xilinx Virtex? 5的一部分系列,并且是可以在芯片上容納快速和密集系統的非常大、密集和高端 FPGA 的示例。550 MHz 部件具有 440 個 I/O 和超過 46,000 個邏輯塊,不僅支持 ARM 內核功能,還支持高達 72 位寬的存儲器寬度、流水線操作、FIFO、具有高達 16.4 Mb 內部塊存儲器的雙端口存儲器和 DSP 功能。

Microsemi是另一家提供 ARM 內核支持的 FPGA 制造商,ProASIC3系列是一個很好的目標技術,具有令人印象深刻的低端到高端邏輯、I/O、RAM 和 15,000 到 3,000,000 門數。一個很好的例子是具有 341 I/O 和 516 Kb 內部 RAM 的A3PE3000-FGG484 。

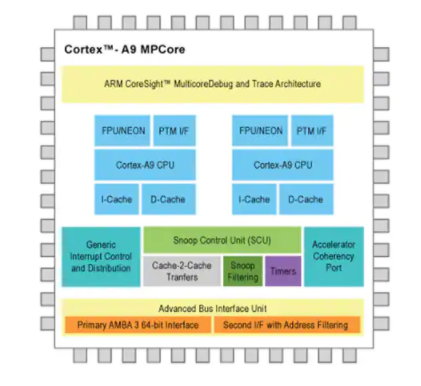

Altera 有類似的部件,如EP3SL50F780C4N,它同樣支持 ARM 核心處理器,還為 DDR、DDR2、DDR3、SDRAM 等提供內存支持,最多可在 24 個模塊化 I/O bank 上使用 448 個 I/O(該系列中最多 744 個)。作為Stratix? III系列的一員,Altera 提供對 Altera Mega-Function Partner Program (AMPP) 的訪問,以獲得可用的外設、內核和支持。Altera 還通過其 Altera MegaCore 功能支持多種知識產權(圖 2)。

圖 2:高端 32 位 ARM 架構是許多 FPGA 的流行內核。這個 Altera 版本增加了多核調試和跟蹤功能,簡化了單個 FPGA 內多個實例化處理器內核的設計。

專有內核

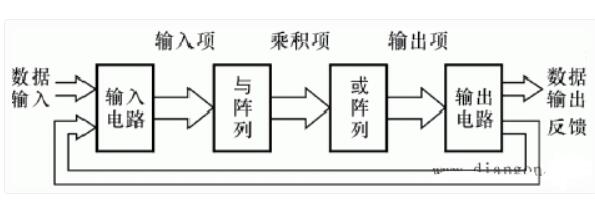

除了行業標準的微控制器內核之外,FPGA 制造商還提供專有內核,這些內核邏輯效率非常高,可擴展至 8 至 32 位性能級別。這些供應商的關鍵是不要在不需要的功能和外圍設備上浪費邏輯;如此經常縮減,實現了準系統處理單元,以提供基本的可編程性和與 FPGA 內部大型邏輯池的接口。這不僅可以讓內核快速運行,還可以讓它們足夠小,以便在您的 SoC 內創建您自己的雙核、四核甚至八核處理器。

Xilinx 將此類內核指定為 Blaze,提供 PicoBlaze 和 MicroBlaze 兩種風格。PicoBlaze 是一種 8 位 RISC 架構,具有高達 240 MHz 的性能。它主要設計用于 VHDL 設計流程,并作為 VHDL 源文件提供。一旦在 13 個不同的 Xilinx 系列之一中實現,它就不需要外部組件,并且完全在主機部分內運行。

支持的系列包括Kinetex-7、Artix-7、Virtex(4、5、6、7、II-Pro)和Spartan?(3 和 6)。

從資源和復雜性的角度來看,PicoBlaze 相當斯巴達(雙關語)。它具有一個 16 x 字節寬的通用數據寄存器、1K 的可編程片上程序存儲(在 FPGA 配置期間自動加載)、一個字節寬的算術邏輯單元 (ALU),帶有 CARRY 和 ZERO 指示標志,64 字節內部暫存器 RAM,以及 256 個輸入和 256 個輸出端口,便于擴展和增強。

另一方面,它具有可預測的性能,每條指令總是兩個時鐘周期,最高可達 240 MHz(或在 Virtex-4 FPGA 中為 100 MIPS)和 88 MHz(或在 Spartan-3 FPGA 中為 44 MIPS)。PicoBlaze 對 Xilinx 用戶免費,并附帶一個匯編程序和 VHDL 源代碼。

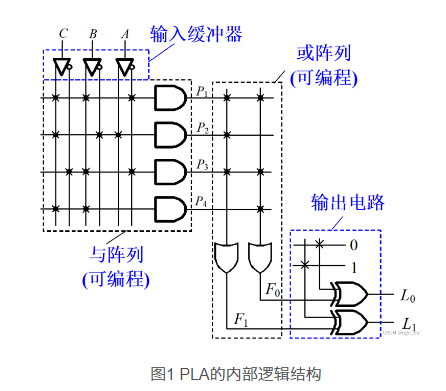

高端的是 Xilinx MicroBlaze。這是一個 32 位 RISC 哈佛架構軟處理器內核,具有 32 個通用 32 位寄存器、ALU、針對嵌入式應用程序優化的豐富指令集、三級 MMU/MPU 支持等。

該內核的靈活性(圖 3)允許您選擇性能優化的五級流水線,通過 Kinetix-7 系列(如XC7K70T-1FBG676C)或 3 級流水線區域可實現高達 317 DMIPS在 Kintex-7 或 Virtex-6 和 7 系列部件(如XC6VLX130T-1FFG784C)上仍可實現可觀的 264 DMIPS 的優化版本。

圖 3:Xilinx FPGA 的專有 32 位 MicroBlaze 內核具有條件編譯指令,允許您添加所需的模塊并刪除不需要的模塊,以節省邏輯并提高密度。

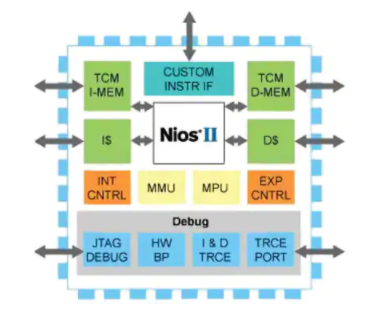

Altera 還提供了一個稱為 NIOS 的專有內核,現在是第二代NIOS II版本(圖 4)。它被譽為業內使用最廣泛的軟處理器,具有實時性能、功率靈敏度和安全關鍵 (DO-254) 合規性。

圖 4:Altera 的第二代 NIOS II 內核被吹捧為 FPGA 使用和支持最廣泛的 IP 內核,并帶來了許多開發和調試功能。

六級流水線 NIOS 內核可以用少至 600 個邏輯元件和特征向量中斷控制、緊密的內存和 DSP 耦合以及添加自定義指令(最多 256 個)的能力來實現。它可以使用內存管理單元 (MMU),并支持開源和商業支持版本的嵌入式 Linux。

可行的替代方案

您的設計細節將決定您應該選擇硬宏還是軟宏。硬宏占用 FPGA 內部的特定位置和資源,但硬編碼宏具有更好的特性,可以實現更好的性能。

軟宏也可以實現良好的性能,特別是如果您有足夠的勇氣修改、改進或并行它們。與往常一樣,良好的設計實踐將產生最佳結果。

總之,當需要盡可能高的密度和/或性能時,選擇 FPGA 內部的軟處理器而不是傳統的微控制器及其所有支持電路在靈活性、效率、性能、功率、和空間。

有關本文中提到的部件的更多信息,請使用提供的鏈接訪問 Digi-Key 網站上的產品信息頁面。

參考

R8051XC2 (Cast Inc.),高性能、可配置、8051 兼容、8 位微控制器內核

電子發燒友App

電子發燒友App

評論