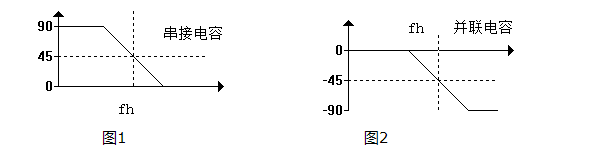

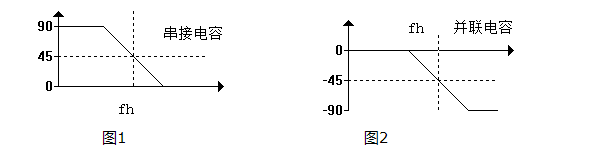

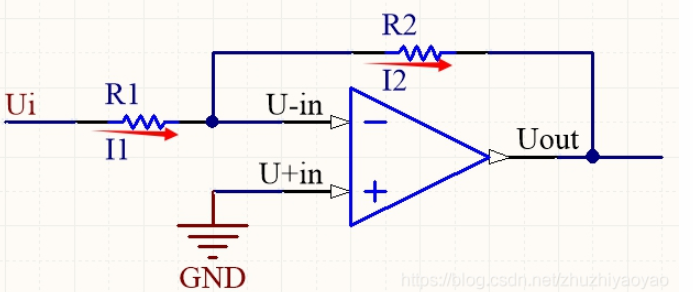

簡單滯后補償:在中間級的輸出并聯一個小電容,讓高端截止頻率變小,從而使180°反饋點自激增益不滿足。

2020-08-14 17:43:33 4660

4660

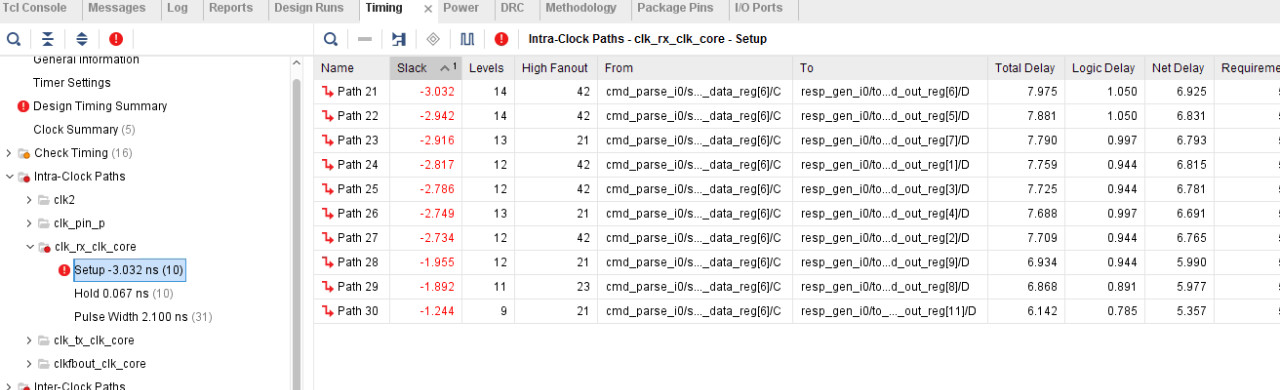

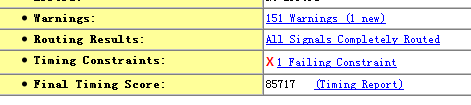

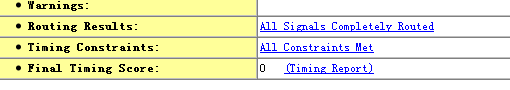

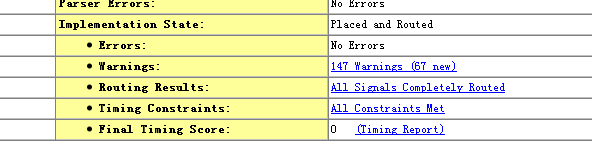

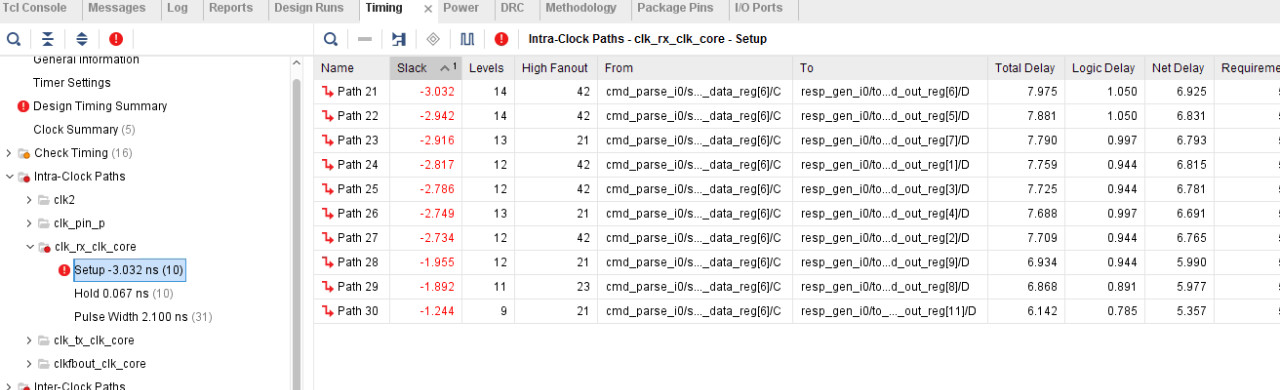

首先來看帶有使能的數據,在本工程中的Tming Report中,也提示了同一個時鐘域之間的幾個路徑建立時間不滿足要求

2020-11-14 11:13:12 4986

4986

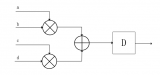

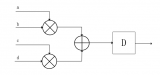

時序路徑 典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。 對于所有的時序路徑,我們都要明確其起點和終點,這4類時序路徑的起點和終點分別如下

2020-11-17 16:41:52 2768

2768

時序不滿足約束,會導致以下問題: 編譯時間長的令人絕望 運行結果靠運氣時對時錯 導致時序問題的成因及其發生的概率如下表: 由上表可見,造成時序問題的主要原因除了約束不完整,就是路徑問題,本文就時序

2020-11-29 10:34:00 7410

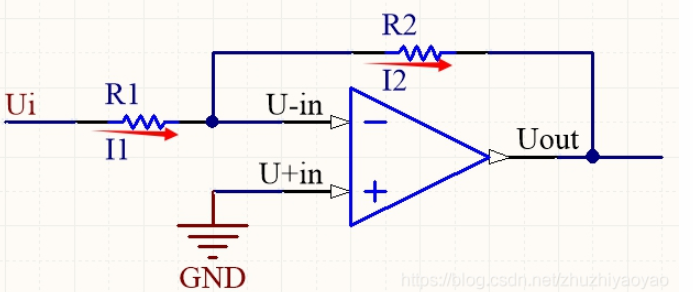

7410 若運放不工作在放大區時,不滿足虛斷和虛短條件 . 比如 , 比較器等 .

2022-07-25 18:10:19 3429

3429

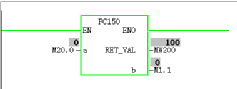

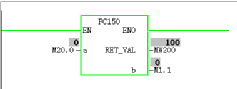

程序有輸出,而PLC的接口沒有輸出,則為接口電路故障。PLC系統的硬件故障多于軟件故障,大多是外部信號不滿足或執行元件故障引起,而不是PLC系統的問題。

2022-09-05 09:54:23 7195

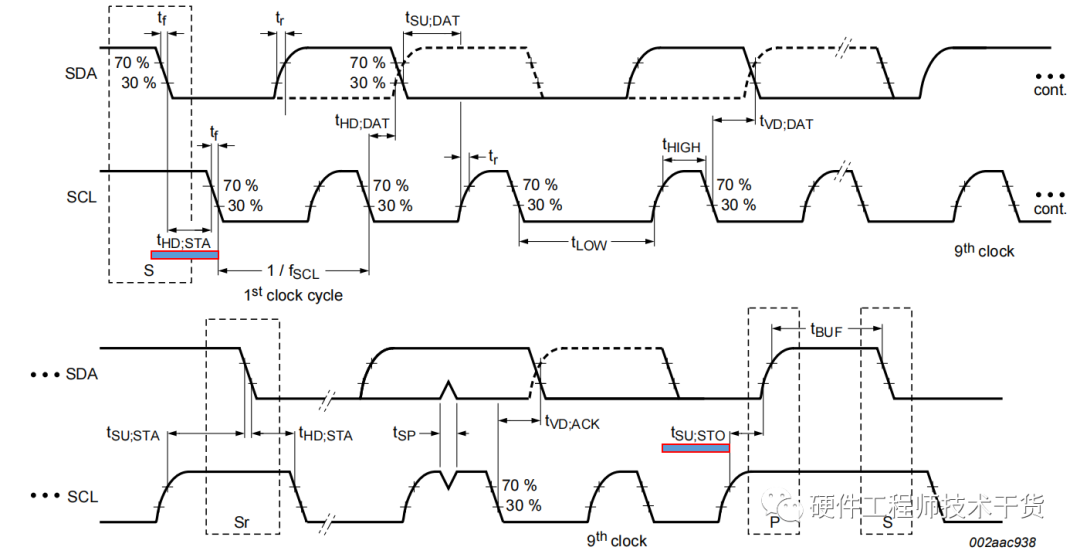

7195 1。時序分析就是分析前級的數據是否在后一個時鐘沿的數據有效窗口里面,就是說在整個窗口內部,數據都應該保持有效,如果不滿足時間窗的前端,就是setup違例,如果不滿足時間窗的后端,那么就是hold違例

2014-12-29 14:53:00

不滿足時序約束。換做8bits*12bits后就不會再有報錯。 請問,時序約束會對乘法器的位寬影響這么大嗎?(芯片是virtex2p)求高手支招

2013-09-11 12:11:18

工作時鐘卻只有100MHz,查資料這款FPGA最快可跑四五百M,時序約束也沒有不滿足建立時間和保持時間的報錯,本身整個系統就用了一個時鐘,同步設計請教一下,為什么只能跑100MHz?是什么原因限制了呢

2017-08-14 15:07:05

某些特定的情況下,比如異步時鐘域時,我們清楚地知道某些寄存器會發生建立時間或者保持時間不滿足的情況,但這是不可避免的,設計者也已經對其進行了處理。在這種情況下,設計者最好告訴EDA軟件忽略這些路徑,否則EDA軟件會努力嘗試解決這些路徑的時序沖突,既費時又沒有效果。

2020-08-16 07:25:02

各位大神,本人在使用AD9681芯片時遇到一個奇怪的問題,一共使用了12片AD9681,其中有幾片AD9681輸出電平(LVDS接口)不滿足要求。

具體情況如下:AD轉換以后的數據通過FPGA進行

2023-12-06 06:13:19

在使用ADS1232雙通道測量的時候,需要實時切換通道,在切換通道的過程中就需要復位ADS1232,復位后再次等待ADS1232準備就緒時,需要的時間過長,不滿足系統實時測量的要求了,不復位讀出的數據錯誤,請問有什么好的解決方法嗎?

2019-05-28 14:43:51

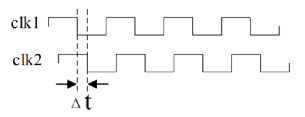

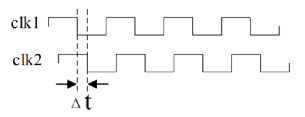

的邏輯是同步邏輯。在一個模塊中不具有相同相位和時間關系的時鐘被視為不同的時鐘域,其所驅動的邏輯是異步邏輯。亞穩態:如果數據傳輸中不滿足觸發器的建立時間和保持時間,或者復位過程中復位信號的釋放相對于有效

2021-07-26 07:03:57

使用的是CCS3.3,在F2812的內部RAM中打斷點調試程序時,發現這條語句(Freq_U_I >60.0)不滿足的情況下,還會停在下面的語句Stop_flag = 1處,

但是,接著

2018-08-28 09:06:32

有時序問題而在Implementation階段反而沒問題,這是因為Vivado在Implementation階段對時序不滿足的地方傾斜了更多的資源保證時序收斂。但是忽略Synthesis的時序問題會在

2020-12-23 17:42:10

:概念:當信號在無關或異步時鐘域中的電路之間傳輸時,亞穩態是一種可能導致數字設備(包括FPGA)中的系統故障的現象。產生:在FPGA系統中,如果數據傳輸中不滿足觸發器的Tsu和Th,或者復位過程中復位信號的釋放相對于有效時鐘沿的恢復時間(recovery time)不滿足,解決:多級寄存器...

2021-07-26 06:01:47

的slack表示數據需求時間小于數據到達時間,不滿足時序(時序的欠缺量)。3.1.7 時鐘最小周期 時鐘最小周期:系統時鐘能運行的最高頻率。 1. 當數據需求時間大于數據到達時間時,時鐘具有余量; 2.

2012-01-11 11:43:06

RT,大家討論討論,可以說說設計中遇見的時序問題及最終的解決方法。

2013-07-24 17:05:25

MDK錯誤:error in include chain (cmsis_armcc.h):expected identifier or '('解決方法:MDK安裝目錄/UV4/UVCC.ini文件中,添加如下代碼cmsis_armcc.h= *官網解決方法

2022-01-25 06:59:47

用OPA656做了一個跟隨器同向輸入接地,反向輸入和輸出直接連接在使用的時候發現輸出電壓和反向輸入電壓相對與輸入電壓低了210mV

2015-12-23 15:12:54

的與NRF24L01及FLASH通訊,但是SPI2的配置并沒有變,如果NRF24L01后初始化 那么時序應該是不滿足FLASH的,同樣如果后初始化FLASH那么時序應該是不滿足NRF24L01。請原子哥及各位朋友解惑了。本人表達能力有限,有點抱歉。謝謝各位了

2020-04-10 04:35:52

STM32VBAT外圍電路接法詳解給大家看幾塊開發板的VBAT外圍電路的設計圖:(1)不滿足(2)符合要求,但不是最佳(3)不滿足(4)不滿足(5)最好的設計stm32芯片手冊要求:(大體上就這兩個

2021-08-05 06:26:20

stm32單片機串口3可以完整接收到數據,但不滿足if(((*(vu32*)(USART3_RX_BUF+4))&0xFF000000)==0x08000000)這個條件,導致不能更新代碼

2019-05-21 01:19:43

依賴關系不滿足。求大神指點

2016-01-20 10:36:47

能自動一次顯示出數字 0、1、2、3、4、5、6、7、8、9(自然數列),1、3、5、7、9(奇數列), 0、2、4、6、8(偶數列),0、1、2、3、4、5、6、7、0、1(音樂符號序列);然后再從頭循環;2.打開電源自動復位,從自然數列開始顯示。我設計的程序好像沒有進入狀態一樣,這是怎么回事?謝謝大神啊

2012-12-25 21:34:32

申請理由:原老儀器使用的單片機為CS8051F060,現在已不滿足用戶以及研發需求,決定更換單片機。現已購買arduino單片機,這些開發套件可以作為外設使用。項目描述:本人負責的開發部分包括:集成

2015-07-29 09:02:59

三極管放大條件,npn管,uc>ub>ue,那直流偏置用一個電源來提供,是不是就不滿足三極管放大條件了啊,求解答!

2019-03-12 16:04:41

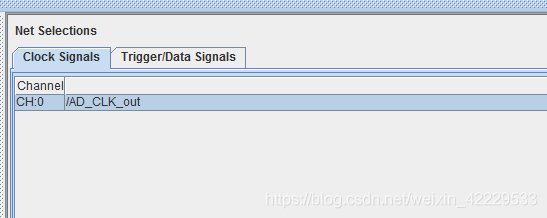

大家好我的設計效果不佳,所以我想用chipcope來檢測信號。但是,在設置“keep hierarchy = yes”之后,不能滿足時序約束。有什么辦法可以解決這個問謝謝!最好的祝福YHM以上

2019-03-28 13:38:35

沒有問題2:用if(((key_press==1)&&(KEY2==0))||(hand!=0))就出現問題了,即使條件不滿足,照樣進入if循環,為什么呀,不解,求救各位大俠有沒有遇到過這種經歷,求解

2019-11-11 04:35:51

。。。P3=0xFE;delay(10); //消抖temp=P3; //假如這里temp就等于0xFEif(0xFE!=temp){ key=temp; }return key; 。。。調試時,temp就等于0xFE,奇跡發生了!if語句被執行了。匯編中為何會多了圈起來的幾行,有何用意?這是誰導致的問題?windows的問題?? keil的問題?? C語言的問題?? 編譯器的問題?? 還是我的問題???大俠救我!!!!

2019-08-15 01:49:15

數據才能夠通過這個十字路口,否則hold時間就不滿足。 同時,紅綠燈默認都是周期性的(clk也是周期性的),車輛不允許在兩個相鄰的紅綠燈之間通過的時間超過一個clk的周期(組合邏輯時延不能過大

2022-11-15 15:19:27

寫verilog代碼時,將編寫好的代碼先做功能仿真,驗證代碼的正確性。代碼時序符合要求后,將代碼下載到FPGA當中,直接分析其時序關系,若是時序不滿足在修改verilog代碼。

2016-08-23 16:57:06

是建立時間不滿足,該怎么辦,人知道嗎,謝謝大家!!

2015-01-26 13:40:13

如圖所示,在TC397的ASCLIN SPI Master Timing表格中,控制器所需要的最小setup time大于最小clock period,這是不滿足時序要求的,請問datasheet是否有誤?

2024-01-29 08:00:24

你好我有一個使用2個塊的概念證明DUT。我正在合成這個forxcvu095-ffvd1924-3-e-es1 FPGA。2個塊獨立地滿足時間要求在具有相同時鐘的組合頂層中。時機不滿足。而且我在1.4

2020-03-31 09:01:20

、帶插值為400ms/s的有效采樣率。滿足這樣要求的FPGA芯片和DA,現在不懂怎么選型,想買塊開發板來學習一下。這個采樣率是DA的采樣率不? 但是找了好久都沒有這樣的芯片,不是采樣率不滿足,就是幅值不滿足。

2019-03-07 06:35:13

一個完整的工程結構這是一個完整的工程目錄,當然需要注意的幾點1.頭文件找不到:解決方法-------------在編譯設置------c/c++----includepath里面加入你的頭文件的路徑

2021-08-23 06:08:27

嗨,我正在使用Virtex II Pro和ISE 8.2.03i。我的設計不符合時序限制,我嘗試在ISE中多次使用PAR選項,但沒辦法。拜托,你能告訴我怎樣才能滿足時間限制嗎?感謝幫助。最好的祝福

2018-09-28 16:56:30

《cc2460 BLE Software Develop’s Guide》中說RTOS clock tick都來源于RTC,而且默認配置為10us,但是RTC模塊中的時鐘來源都是32KHz時鐘,Tick為1/32768=0.000030517578125s約為30.5us,這樣時間豈不是不滿足了嗎?

2019-10-14 06:19:21

光以太網通信不正常。經過分析得到是FPGA通MII接口和PHY的時序不滿足。如圖 9所示為MII接口的時序圖,時序不滿足分為TX_CLK和RX_CLK。其一是PHY輸出的TX_CLK和FPGA依據

2018-04-03 11:19:08

如果DFF的hold時間不滿足,通常可以通過降低時鐘運行速度來解決( )A 是B 不是解析:建立時間:即時鐘有效沿來臨之前數據需要保持穩定的最小周期,以便數據在隨時鐘信號采樣時是準確的。保持時間

2021-07-29 06:10:52

飽和導通就是發射結和集電結都正偏,當基級是高電平的時候,確實上面那個三極管發射結正偏,但集電結的電壓應該不滿足正偏吧,同樣的當基級電壓為低電平,由于上面那個三極管是截止的,電壓就傳不過來了,那e級

2019-08-12 04:36:04

eta3=0.215, Diffn都是數值,其中n=2,3,4,5,6,7。現在,只要不滿足Diff2

2014-06-03 20:37:06

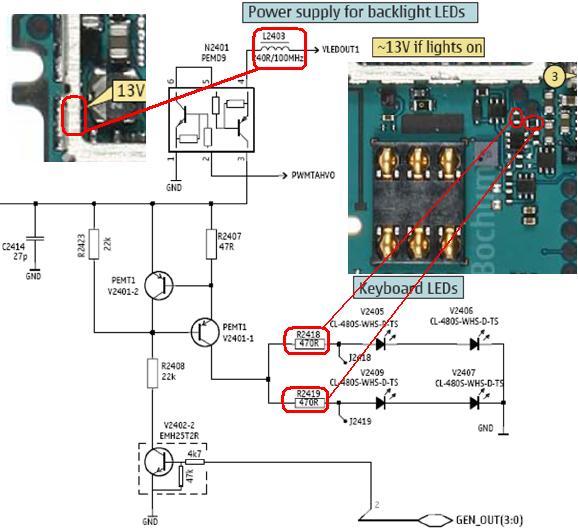

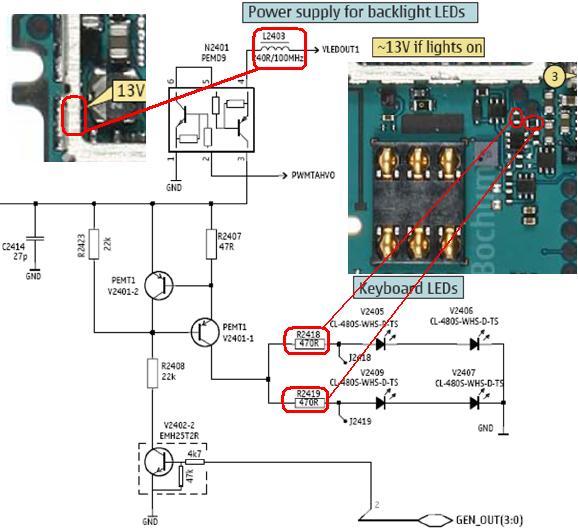

手機TFT顯示驅動的解決方法和應用方法是什么

2021-06-07 06:07:37

這個電路運放明顯不滿足虛短要求啊,而且負向輸入端電壓大于了電源電壓,有人能解釋下嗎?謝謝!!

2015-12-02 20:33:43

條件結構中當滿足條件時,數據可進入條件并輸出,當不滿足條件時,不想讓數據進入,怎么實現?求大神指教。。。

2016-03-22 11:50:08

`求解決方法`

2020-08-02 17:48:16

類似與上圖的仿真,上圖仿真結果不滿足負載端電壓要求!!!很急!!!!!!很急!!!!!!!!!!!!!很急!!!!!!!!!!!!!!!!!!!!!

2016-12-13 21:55:36

采用UC3844的雙管正激式拓撲電源,開關變壓器產生嘯叫的解決方法。

2011-09-17 21:53:48

導讀:蘋果公司發布了他們的智能音箱,標志著他們已經不滿足做手機等系列產品了,他們要開始布局自己在智能模塊的新局勢。

[img][/img]

全球自動駕駛汽車領域的競爭異常激烈,傳統汽車廠

2017-06-17 09:31:43

試分析方向阻抗繼電器消除各種類型故障的死區的方法?數字濾波與模擬濾波相比有何優點?電流互感器10%誤差不滿足要求時,可采取哪些措施?試說明數字濾波器的優點有哪些?

2021-09-01 06:56:20

針對某微型客車進行了耐撞性分析, 找出其不滿足我國正面碰撞乘員被動安全性法規要求

的原因, 并對提高其車身結構被動安全性的方法進行了研究。通過建立相應的力學

2009-07-25 15:07:51 7

7 黃菲林的使用及常見問題的解決方法一,前言:黃菲林是指在透明的聚脂類片材上

2006-04-16 20:57:17 1242

1242

諾基亞6300無背景燈解決方法

2008-09-01 17:52:45 1889

1889

ThinkPad-鼠標問題的一般解決方法

鼠標問題的一般解決方法: 1. 確認鼠標設備的狀態已被設置為 Automatic(自動) 或 AutoDisable注意

2010-01-26 13:41:54 1728

1728 介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 短波通信盲區現象解決方法介紹短波通信盲區現象解決方法介紹短波通信盲區現象解決方法介紹

2015-11-10 17:13:15 5

5 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 電子專業單片機相關知識學習教材資料——電感嘯叫的成因與解決方法

2016-10-10 14:17:59 0

0 如果要說誰是現在最好的手機VR產品,大多數人想到的應該是三星Gear VR,但三星的野心顯然不滿足于此。在明年2月推出Galaxy S8和新款Gear VR頭戴設備之后,三星的AR眼鏡可能也不會太遙遠。

2016-12-21 11:06:41 817

817 DXP2004 warning報警及解決方法

2016-12-26 15:58:52 0

0 首先人比機器更聰明,更了解自己設計的需求和結構。其次在關鍵路徑上的手工布局能提高時序性能,使不滿足要求變成滿足要求。

2017-02-11 10:53:33 2878

2878 本文檔內容介紹了C盤占用空間太大的解決方法,供參考。

2017-09-20 14:39:46 0

0 POP噪音及其常用解決方法

2017-11-27 14:56:10 14

14 開關電源的電磁干擾解決方法

2017-11-29 17:57:10 13

13 基于非開挖技術的水平定向鉆方法,無線導向技術和傳統直入直出的施工方式已不滿足地下管線復雜、空間狹小的主城區復雜環境施工作業的需求。

2019-07-22 14:58:38 3281

3281 在使用加濕器的過程中發現不噴霧或噴霧小了是什么原因呢?有什么解決方法。

2020-04-04 16:09:00 25494

25494 AMD已經不滿足于CPU市場的成功,而希望更多在異構市場進行布局。 北京時間11月16日晚10點,AMD正式發布了首款基于全新CDNA架構的Instinct MI100加速顯卡,以及配套的ROCm

2020-11-17 15:00:31 1359

1359 Retiming就是重新調整時序,例如電路中遇到復雜的組合邏輯,延遲過大,電路時序不滿足,這個時候采用流水線技術,在組合邏輯中插入寄存器加流水線,進行操作,面積換速度思想。

2020-12-11 14:30:12 1178

1178

<指令> -在滿足條件時,要執行的指令。如果不滿足條件,則執行 ELSE 后編寫的指令。如果不滿足程序循環內的任何條件,則執行這些指令。

2021-03-02 14:52:56 1138

1138

數字電源市場中存在的問題及解決方法

2021-07-01 14:23:56 12

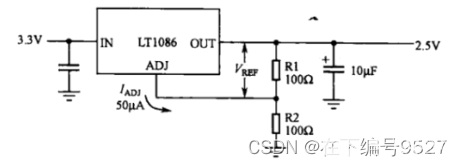

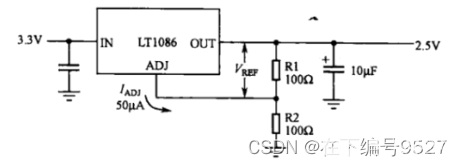

12 目錄 工程問題 1 LDO 輸出電源電平低于設置值 2 電源芯片欠壓保護電路導致上電時序不滿足設計的要求? ?原理/layout圖 優點 缺點 原理 ?選型 熱計算 計算 LDO 工作

2022-06-29 14:53:15 3197

3197

通常在使用浮球液位開關時,經常會遇到一些小問題,但是又不知道如何解決。下面一起來看下浮球液位開關的一些常見問題及解決方法。 1.浮球不滑動,導致開關無信號輸出。 解決方法:檢查下液位開關上面是否結了

2022-08-24 14:40:51 2309

2309

近幾年點云 slam 領域有一類文章不滿足于僅估計 pose graph。嘗試類似視覺 slam 中的 ba 方法,其致力于同時估計 feature 和 pose。

2022-11-21 10:53:08 464

464 在工作中碰到太陽能板的串并聯接線,因為項目使用的輸出電壓比太陽能板大,太陽能板單塊的電壓不滿足設計要求。

2023-03-13 09:38:23 26756

26756 當觸發器輸入端的數據和觸發器的時鐘不相關時,很容易導致電路時序約束不滿足。本章主要解決模塊間可導致時序 violation 的異步問題。

2023-03-28 13:46:46 6733

6733

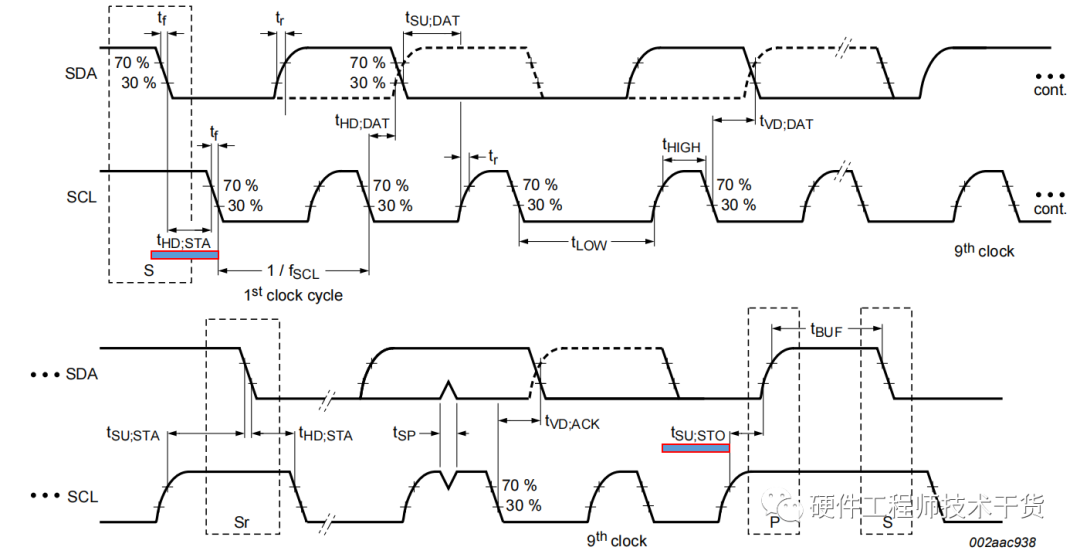

最近硬件測試工程師反饋一個BUG,和IIC的時序有關,這個BUG目前沒有帶來使用方面的影響,但是不符合規范,要求整改。我們使用的單片機是cortex-m3內核的芯片,美信公司生產,使用此芯片讀取電容

2023-06-14 17:52:31 1573

1573

使用“滿足條件時執行”指令可以重復執行程序循環,直至不滿足執行條件為止。該條件是結果為布爾值(TRUE 或 FALSE)的表達式。可以將邏輯表達式或比較表達式作為條件。

2023-06-27 16:42:20 1453

1453 使用“不滿足條件時執行”指令可以重復執行程序循環,直至不滿足執行條件為止。該條件是結果為布爾值(TRUE 或 FALSE)的表達式。可以將邏輯表達式或比較表達式作為條件。

2023-07-12 09:50:28 481

481 保護死區的概念和解決方法

2023-07-15 11:02:10 753

753

時 , 將輸入 D 端的數據給到輸出 Q, 當使能條件不滿足時 , 輸入數據 D 會暫存在觸發器當中 , 直到觸發條件滿足才給到輸出 Q。 (2):D 觸發器工作時序 時鐘 clk: 周期性變化信號 。 時鐘極性 (CPOL): 時鐘初始值是 0, 時鐘極性為 0; 時鐘初始值是 1, 時鐘極性為 1。

2023-11-02 12:00:01 308

308

PCB壓合問題解決方法

2024-01-05 10:32:26 248

248 EMI電磁干擾:原理、影響及解決方法詳解?|深圳比創達電子

2024-03-21 10:02:12 73

73

電子發燒友App

電子發燒友App

評論