在給FPGA做邏輯綜合和布局布線時,需要在工具中設(shè)定時序的約束。通常,在FPGA設(shè)計(jì)工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯

2023-10-12 12:00:02 866

866

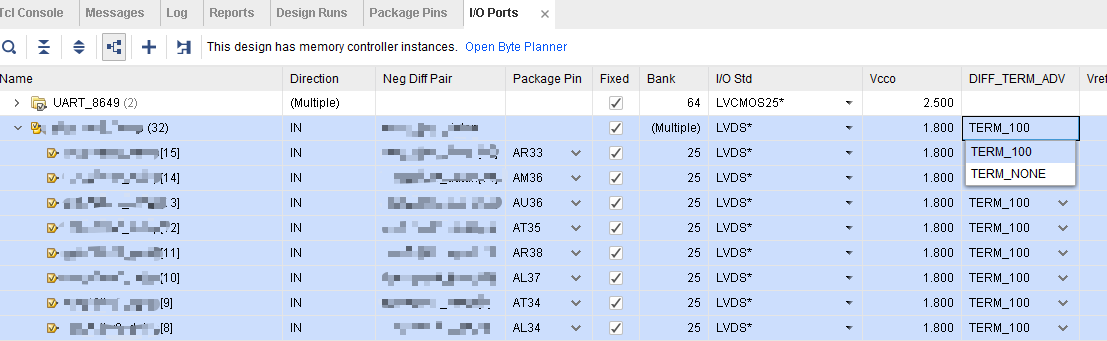

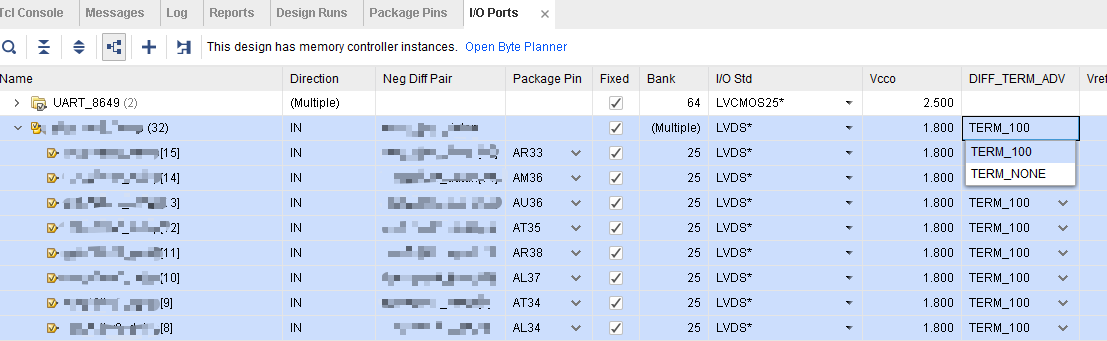

I/O約束 I/O約束是必須要用的約束,又包括管腳約束和延遲約束。 管腳約束 管腳約束就是指管腳分配,我們要指定管腳的PACKAGE_PIN和IOSTANDARD兩個屬性的值,前者指定了管腳的位置

2020-10-30 16:08:13 13112

13112

約束流程 說到FPGA時序約束的流程,不同的公司可能有些不一樣。反正條條大路通羅馬,找到一種適合自己的就行了。從系統(tǒng)上來看,同步時序約束可以分為系統(tǒng)同步與源同步兩大類。簡單點(diǎn)來說,系統(tǒng)同步

2020-11-20 14:44:52 6859

6859

在 Flow Navigator 中點(diǎn)擊設(shè)置, 然后選擇Synthesis,或者 selectFlow Settings Synthesis Settings。 如圖1所示: 1、綜合約束 在設(shè)置

2020-11-23 14:16:36 4238

4238

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2022-07-25 10:13:44 4067

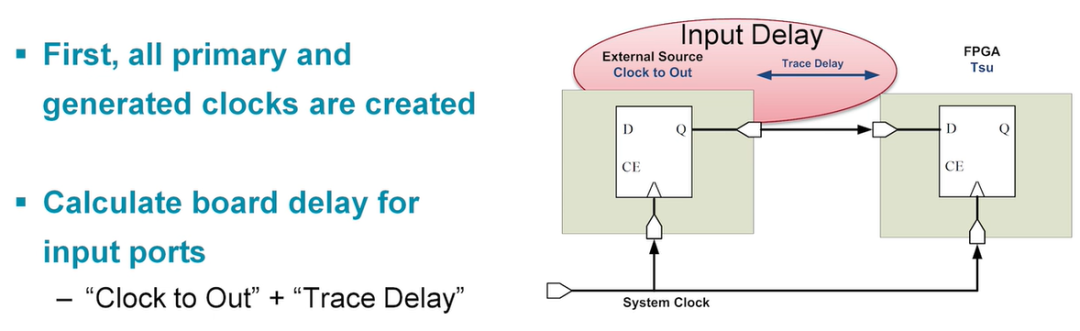

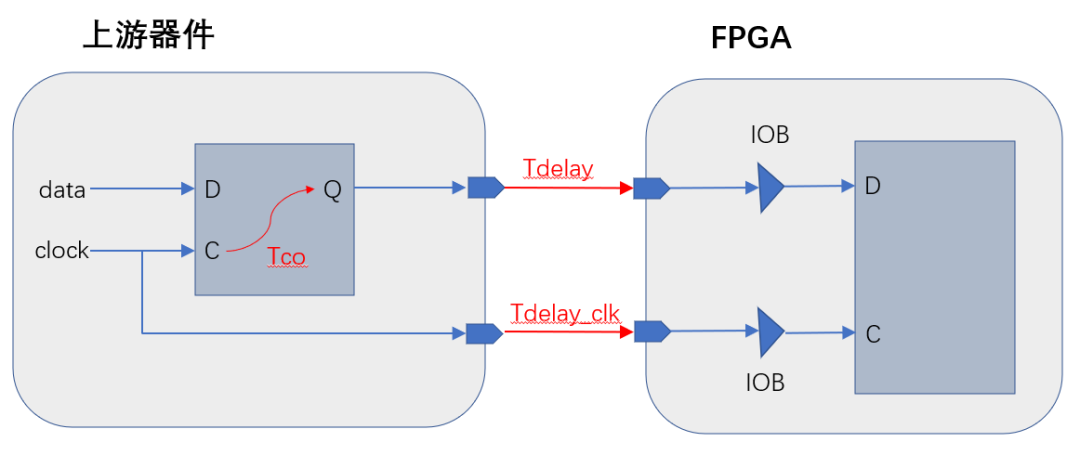

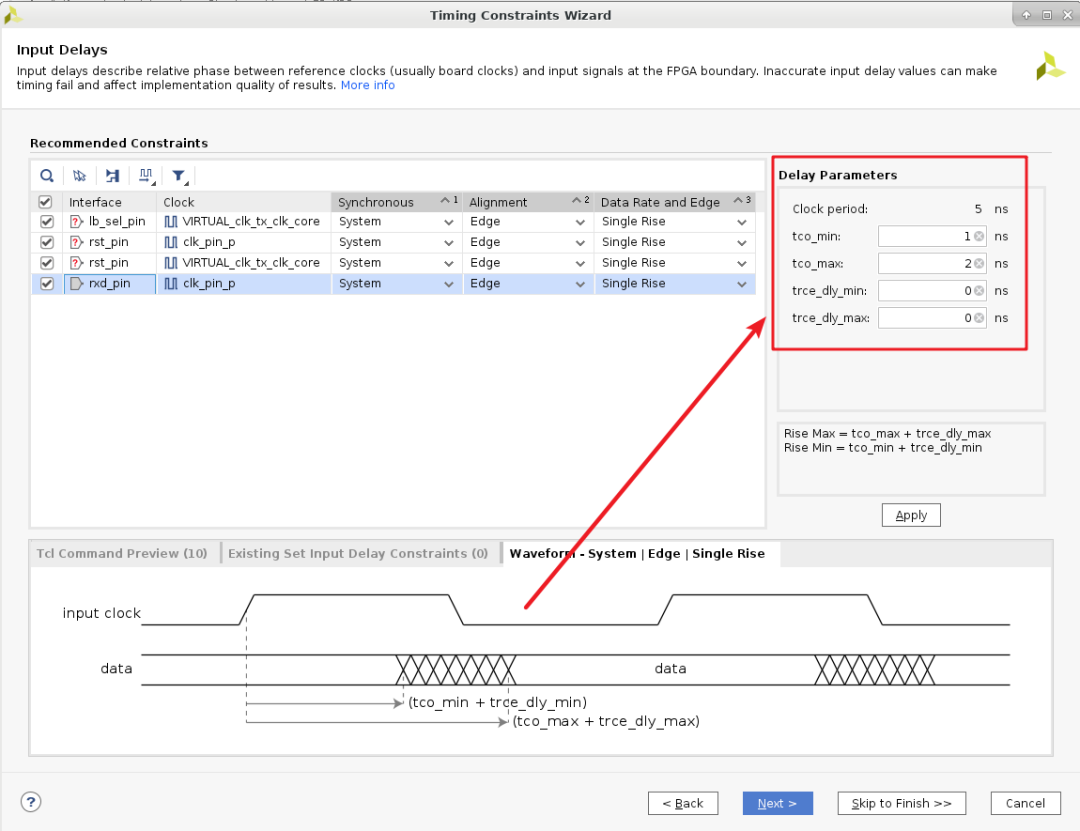

4067 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束和時序例外約束才能實(shí)現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 最近準(zhǔn)備采用Xilinx FPGA進(jìn)行多機(jī)通信,即主FPGA芯片將采集到的不同層的圖像數(shù)據(jù)流分別輸出給對應(yīng)的4塊從FPGA芯片中,主從FPGA之間的連接機(jī)制采用星形拓?fù)浣Y(jié)構(gòu)。經(jīng)計(jì)算,圖像數(shù)據(jù)流接口速率需要數(shù)百兆比特/秒,因此需要調(diào)研FPGA支持的常見IO接口標(biāo)準(zhǔn),及每種接口的應(yīng)用場合。

2022-10-17 09:14:18 1626

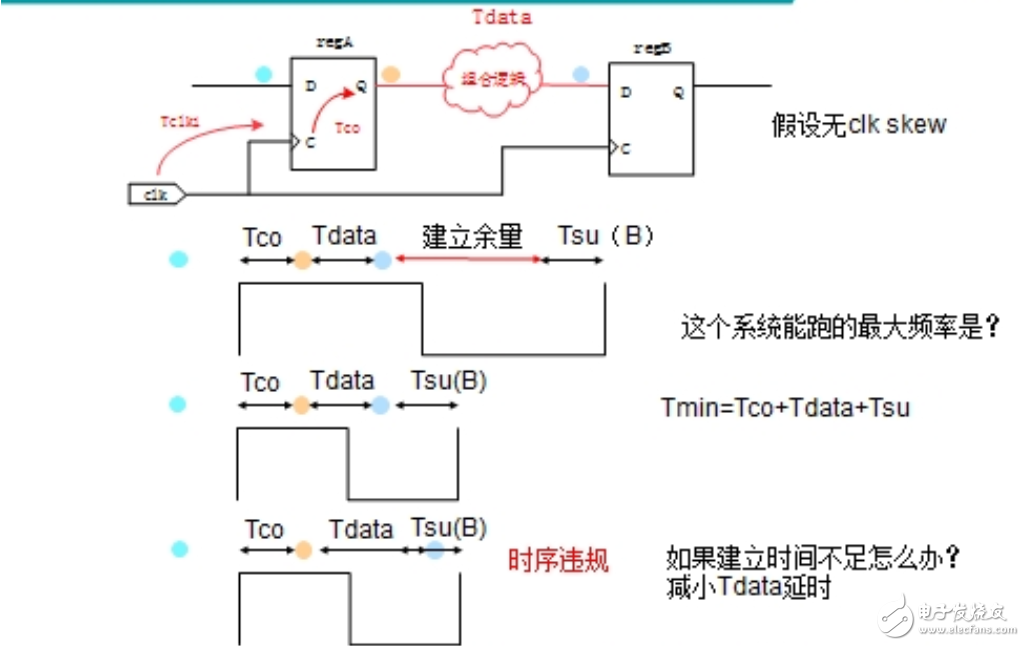

1626 FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

在FPGA設(shè)計(jì)中,時序約束的設(shè)置對于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時序約束的基礎(chǔ)知識。

2023-06-06 18:27:13 6213

6213

在FPGA設(shè)計(jì)中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

1230 前面幾篇FPGA時序約束進(jìn)階篇,介紹了常用主時鐘約束、衍生時鐘約束、時鐘分組約束的設(shè)置,接下來介紹一下常用的另外兩個時序約束語法“偽路徑”和“多周期路徑”。

2023-06-12 17:33:53 868

868 在FPGA設(shè)計(jì)中,時序約束的設(shè)置對于電路性能和可靠性都至關(guān)重要。

2023-06-26 14:47:16 923

923

FPGA中時序約束是設(shè)計(jì)的關(guān)鍵點(diǎn)之一,準(zhǔn)確的時鐘約束有利于代碼功能的完整呈現(xiàn)。進(jìn)行時序約束,讓軟件布局布線后的電路能夠滿足使用的要求。

2023-08-14 17:49:55 712

712

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實(shí)際使用。

2023-08-14 18:22:14 842

842

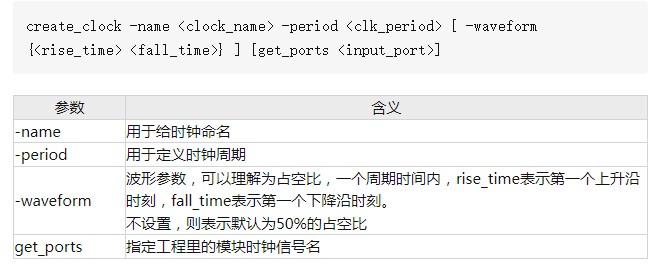

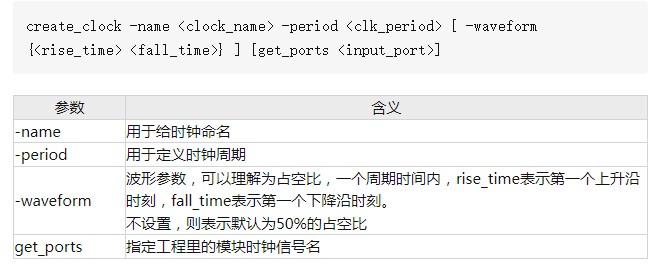

時鐘周期約束是用于對時鐘周期的約束,屬于時序約束中最重要的約束之一。

2023-08-14 18:25:51 472

472 在進(jìn)行布局約束前,通常會對現(xiàn)有設(shè)計(jì)進(jìn)行設(shè)計(jì)實(shí)現(xiàn)(Implementation)編譯。在完成第一次設(shè)計(jì)實(shí)現(xiàn)編譯后,工程設(shè)計(jì)通常會不斷更新迭代,此時對于設(shè)計(jì)中一些固定不變的邏輯,設(shè)計(jì)者希望它們的編譯結(jié)果

2024-01-02 14:13:53 434

434

關(guān)于FPGA的IO設(shè)計(jì),我有以下幾個疑問,希望大家多多指教1. 在FPGA設(shè)計(jì)中(Altera cyclone IV),對于一個三態(tài)口來說,設(shè)置成輸入,是不是懸空的啊?(這種問題是不是找相應(yīng)的手冊

2015-10-31 20:13:49

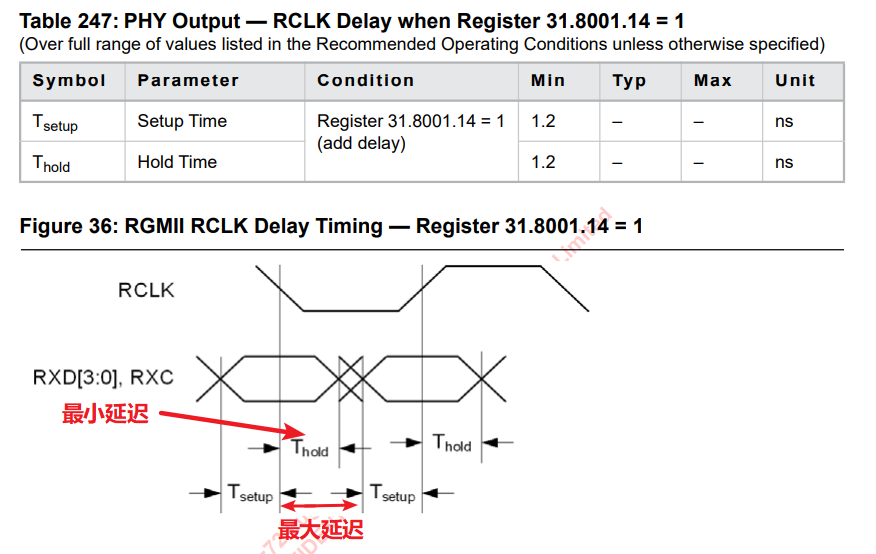

在設(shè)計(jì)以太網(wǎng)中繼器時,因?yàn)闆]有配置時鐘約束,導(dǎo)致中繼器工作不正常。后面根據(jù)手冊配置時鐘約束解決了此問題。

2016-10-07 18:51:24

嗨,我是初學(xué)者,在FPGA上設(shè)計(jì)系統(tǒng)。我檢查了我的輸出沒有生成,所以我想要。我有5個子模塊,它們具有來自相同輸入的時鐘。據(jù)我所知,考慮到不同金屬與時鐘輸入的不同延遲,應(yīng)對每個子模塊進(jìn)行時鐘緩沖。但在

2020-05-22 09:22:23

,FPGA上的全局時鐘管腳用完了就出現(xiàn)不夠用的情況。FPGA全局時鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

設(shè)計(jì)、引腳分配產(chǎn)生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態(tài)進(jìn)行分析。 從時間階段可以分為兩部分,第一階段是從FPGA上電開始直到配置

2021-01-08 17:29:15

右鍵然后點(diǎn)擊 show IO banks,這個時候就會看到FPGA的管腳被幾種顏色劃分開了。一種顏色下的IO口代表一組bank。你在吧管腳的locaTIon約束完成以后。IO Bank會自動填充完畢

2019-06-17 08:55:43

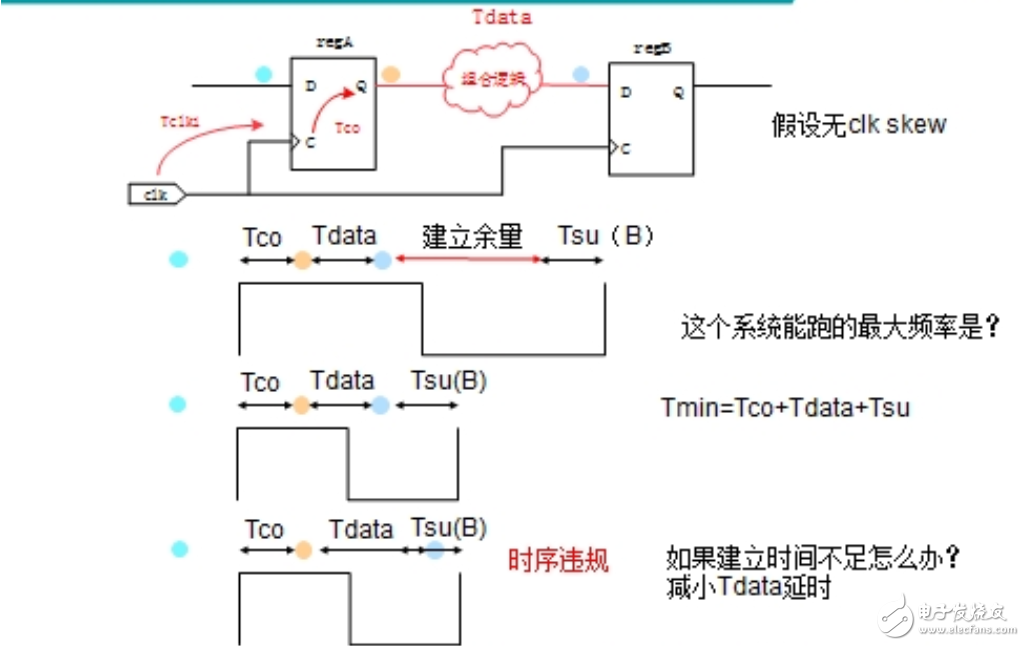

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時間

2023-11-15 17:41:10

FPGA時序約束,總體來分可以分為3類,輸入時序約束,輸出時序約束,和寄存器到寄存器路徑的約束。其中輸入時序約束主要指的是從FPGA引腳輸入的時鐘和輸入的數(shù)據(jù)直接的約束。共分為兩大類:1、源同步系統(tǒng)

2015-09-05 21:13:07

FalsePath、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設(shè)計(jì)者的思路還局限在FPGA芯片內(nèi)部。 2. 核心頻率約束

2016-06-02 15:54:04

不是最完整的時序約束。如果僅有這些約束的話,說明設(shè)計(jì)者的思路還局限在FPGA芯片內(nèi)部。 2. 核心頻率約束+時序例外約束+I/O約束 I/O約束包括引腳分配位置、空閑引腳驅(qū)動方式、外部走線延時

2017-12-27 09:15:17

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數(shù)據(jù)和時鐘傳輸路徑是由相應(yīng)的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

你好: 現(xiàn)在我使用xilinx FPGA進(jìn)行設(shè)計(jì)。遇到問題。我不知道FPGA設(shè)計(jì)是否符合時序要求。我在設(shè)計(jì)中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應(yīng)該被禁止。我

2019-03-18 13:37:27

FPGA的DCM模塊,40MHz時鐘輸入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。對40MHz時鐘添加了約束,系統(tǒng)不是會自動對三個輸出時鐘進(jìn)行約束

2017-05-25 15:06:47

關(guān)鍵內(nèi)容提要:

(1)FPGA IO命名方式;

(2)FPGA的上電時序

今天想和大家一起聊聊FPGA的IO。

先說說我當(dāng)年入門的經(jīng)歷吧。國內(nèi)的大學(xué)有FPGA開發(fā)條件的實(shí)驗(yàn)室并不太多,當(dāng)年大學(xué)的那幫

2023-11-03 11:08:33

多種不同的電壓標(biāo)準(zhǔn),也有豐富的IO。首先,FPGA的IO物理命名規(guī)則,也就是我們做管腳約束時候的命名,芯片通常是長方體或者正方體,所以命名通常采用字母+數(shù)字組合的方式,從上到下是字母(A,B,C,D

2019-07-18 14:26:01

在進(jìn)行FPGA的設(shè)計(jì)時,經(jīng)常會需要在綜合、實(shí)現(xiàn)的階段添加約束,以便能夠控制綜合、實(shí)現(xiàn)過程,使設(shè)計(jì)滿足我們需要的運(yùn)行速度、引腳位置等要求。通常的做法是設(shè)計(jì)編寫約束文件并導(dǎo)入到綜合實(shí)現(xiàn)工具,在進(jìn)行

2023-09-21 07:45:57

FPGA的reset信號需要加什么SDC約束呢?

2023-04-23 11:38:24

,因此,為了避免這種情況,必須對fpga資源布局布線進(jìn)行時序約束以滿足設(shè)計(jì)要求。因?yàn)闀r鐘周期是預(yù)先知道的,而觸發(fā)器之間的延時是未知的(兩個觸發(fā)器之間的延時等于一個時鐘周期),所以得通過約束來控制觸發(fā)器之間的延時。當(dāng)延時小于一個時鐘周期的時候,設(shè)計(jì)的邏輯才能穩(wěn)定工作,反之,代碼會跑飛。

2018-08-29 09:34:47

`為保證設(shè)計(jì)的成功,設(shè)計(jì)人員必須確保設(shè)計(jì)能在特定時限內(nèi)完成指定任務(wù)。要實(shí)現(xiàn)這個目的,我們可將時序約束應(yīng)用于連線中——從某 FPGA 元件到 FPGA 內(nèi)部或 FPGA 所在 PCB 上后續(xù)元件輸入

2012-03-01 15:08:40

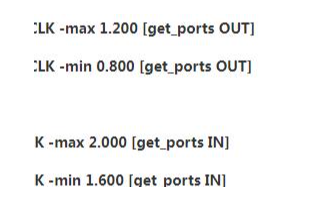

FPGA靜態(tài)時序分析——IO口時序(Input Delay /output Delay)1.1概述 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束和時序例外約束才能

2012-04-25 15:42:03

(rxdata)發(fā)送回vlx75T。有連接器在FPGA之間連接它們。我想知道 -1)為進(jìn)入vlx760t FPGA的txdata和clk線的約束添加偏移是“強(qiáng)制性的”嗎?甚至沒有約束的偏移,設(shè)計(jì)仍然可以工作?2

2019-04-08 10:27:05

Xilinx_fpga_設(shè)計(jì):全局時序約束及試驗(yàn)總結(jié)

2012-08-05 21:17:05

在給 FPGA 做邏輯綜合和布局布線時,需要在工具中設(shè)定時序的約束。通常,在 FPGA 中都包含有4 種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入 到輸出的純組合邏輯

2012-03-05 15:02:22

完成頂層模塊的實(shí)現(xiàn)并且仿真正確后,還需要編寫用戶約束文件,其中引腳約束文件是必不可少的,它將模塊的端口和 FPGA 的管腳對應(yīng)起來。具體步驟如下。(1)創(chuàng)建約束文件。新建一個源文件,在代碼類型中選

2018-09-29 09:18:05

本視頻是MiniStar FPGA開發(fā)板的配套視頻課程,主要通過工程實(shí)例介紹Gowin的物理約束和時序約束,課程內(nèi)容包括gowin的管腳約束及其他物理約束和時序優(yōu)化,以及常用的幾種時序約束。 本

2021-05-06 15:40:44

、MulticyclePath、MaxDelay、MinDelay。但這還不是最完整的時序約束。如果僅有這些約束的話,說明設(shè)計(jì)者的思路還局限在FPGA芯片內(nèi)部。2. 核心頻率約束+時序例外約束+I/O約束 I/O

2017-10-20 13:26:35

SDRAM數(shù)據(jù)手冊有如張時序要求圖。如何使SDRAM滿足時序要求?方法1:添加時序約束。由于Tpcb和時鐘頻率是固定的,我們可以添加時序約束,讓FPGA增加寄存器延時、寄存器到管腳的延時,從而使上述

2016-09-13 21:58:50

①蜂鳥FPGA約束文件是適用于MCU200T板子嗎?

②如果適用,那么在FPGA約束文件中的引腳約束是怎么對應(yīng)到MCU 200T板子中?

eg:

比如這幾條約束是怎么對應(yīng)到MCU 200T板子中的引腳呢?

2023-08-16 06:58:04

FPGA input delay約束的方法該視頻拋棄復(fù)雜的理論,按照工程實(shí)際情況,分析各種情況,只要選擇正確情況然后約束即可。mdy-edu.com/article_cat/video?id

2017-03-04 14:55:43

,BANK12····MIO0,EMIO···。但這確實(shí)是FPGA的特點(diǎn),FPGA可以兼容多種不同的電壓標(biāo)準(zhǔn),也有豐富的IO。 首先,FPGA的IO物理命名規(guī)則,也就是我們做管腳約束時候的命名,芯片通常是

2020-12-23 17:44:23

在給FPGA做邏輯綜合和布局布線時,需要在工具中設(shè)定時序的約束。通常,在FPGA設(shè)計(jì)工具中都FPGA中包含有4種路徑:從輸入端口到寄存器,從寄存器到寄存器,從寄存器到輸出,從輸入到輸出的純組合邏輯。

2019-11-08 07:27:54

我們在實(shí)現(xiàn)FPGA邏輯電路時,時常會在Verilog代碼里添加一些約束原語。前言我們在描述FPGA電路時,我們經(jīng)常會在電路里添加一些像這樣的約束原語:通過這種方式,我們可以指導(dǎo)FPGA在綜合及布局

2022-07-22 14:28:10

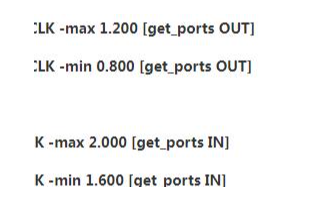

create_clock -name sysclk -period 10 [get_ports clkin]1. 輸入延遲約束set_input_delay-clock sysclk -max 4

2018-09-21 12:50:15

[get_ports {data_out[0]}]set_propertyIOSTANDARD LVCMOS33 [get_ports {data_out[0]}]也可在綜合之后,打開右上角小窗口,選擇I/O Planning進(jìn)行約束。

2018-09-21 13:17:37

DCMl輸出: clkfx = 100MHz和clkfx_180=100MHz不過相位差180度.FPGA輸出到DAC中,DAC需要FPGA提供data[11:0]和寫入時鐘. 我用clkfx作為

2012-03-29 09:51:36

我是一個FPGA初學(xué)者,關(guān)于時序約束一直不是很明白,時序約束有什么用呢?我只會全局時鐘的時序約束,如何進(jìn)行其他時序約束呢?時序約束分為哪幾類呢?不同時序約束的目的?

2012-07-04 09:45:37

EF2的MIPI_IO如何在ADC文件中約束?

2023-08-11 06:10:29

大家好我正在使用Virtex5 FPGA,我在設(shè)計(jì)中添加了一個OFFSET IN約束,如下所示。NET“Sysclk”TNM_NET =“Sysclk”;TIMESPEC“TS_Sysclk

2020-06-13 19:23:05

該文提出一種基于時間約束的FPGA數(shù)字水印技術(shù),其基本思想是將準(zhǔn)備好的水印標(biāo)記嵌人非關(guān)鍵路徑上的時間約束來定制最終的下載比特流文件,同時并不改變設(shè)計(jì)的原始性能.這一方

2010-06-09 07:45:49 7

7 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 賽靈思FPGA設(shè)計(jì)時序約束指南,下來看看

2016-05-11 11:30:19 48

48 引腳和區(qū)域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應(yīng)關(guān)系。 那么我們應(yīng)該怎么寫呢?

2018-07-14 02:49:00 10273

10273 時序約束可以使得布線的成功率的提高,減少ISE布局布線時間。這時候用到的全局約束就有周期約束和偏移約束。周期約束就是根據(jù)時鐘頻率的不同劃分為不同的時鐘域,添加各自周期約束。對于模塊的輸入輸出端口添加

2017-02-09 02:56:06 605

605 Xilinx FPGA編程技巧常用時序約束介紹,具體的跟隨小編一起來了解一下。

2018-07-14 07:18:00 4129

4129

FPGA設(shè)計(jì)中的約束文件有3類:用戶設(shè)計(jì)文件(.UCF文件)、網(wǎng)表約束文件(.NCF文件)以及物理約束文件(.PCF文件),可以完成時序約束、管腳約束以及區(qū)域約束。

2017-02-11 06:33:11 1426

1426 作時序和布局約束是實(shí)現(xiàn)設(shè)計(jì)要求的關(guān)鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設(shè)計(jì)只是 FPGA 設(shè)計(jì)量產(chǎn)準(zhǔn)備工作中的一部分。接下來的挑戰(zhàn)是確保設(shè)計(jì)滿足芯片內(nèi)的時序和性能要求。為此

2017-11-17 05:23:01 2417

2417

一個好的FPGA設(shè)計(jì)一定是包含兩個層面:良好的代碼風(fēng)格和合理的約束。時序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實(shí)現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

針對八通道采樣器AD9252的高速串行數(shù)據(jù)接口的特點(diǎn),提出了一種基于FPGA時序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數(shù)據(jù),利用FPGA內(nèi)部的時鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 6488

6488

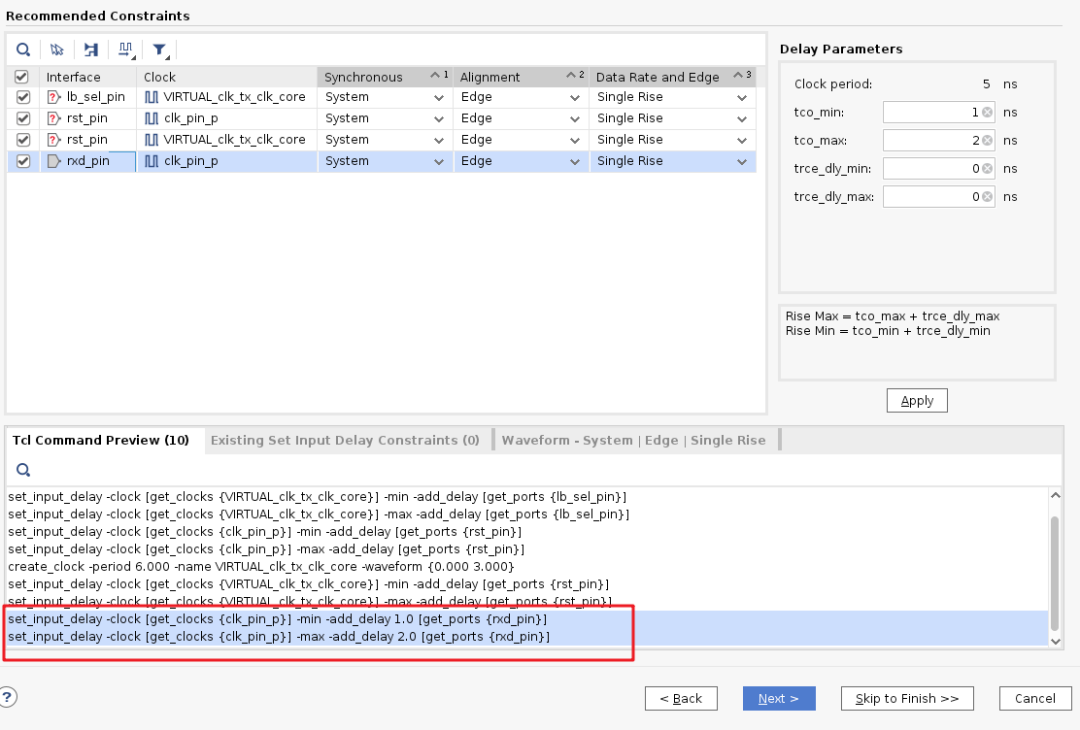

從UCF到XDC的轉(zhuǎn)換過程中,最具挑戰(zhàn)的可以說便是本文將要討論的I/O約束了。 I/O 約束的語法 XDC 中可以用于 I/O 約束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。

2017-11-17 18:54:01 11853

11853

XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應(yīng)用特性決定了其在接口上有多種構(gòu)建和實(shí)現(xiàn)方式,所以從UCF到XDC的轉(zhuǎn)換過程中,最具挑戰(zhàn)的可以說便是本文將要

2017-11-17 19:01:00 6665

6665

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達(dá)到時序收斂感到困惑。為幫助 FPGA設(shè)計(jì)新手實(shí)現(xiàn)時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實(shí)現(xiàn)

2017-11-24 19:37:55 4903

4903

本文主要通過一個實(shí)例具體介紹ISE中通過編輯UCF文件來對FPGA設(shè)計(jì)進(jìn)行約束,主要涉及到的約束包括時鐘約束、群組約束、邏輯管腳約束以及物理屬性約束。 Xilinx定義了如下幾種約束類型

2017-11-24 19:59:29 2671

2671

在進(jìn)行FPGA硬件設(shè)計(jì)時,引腳分配是非常重要的一個環(huán)節(jié),特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態(tài),會對硬件設(shè)計(jì)、引腳分配產(chǎn)生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態(tài)進(jìn)行分析。

2017-11-28 14:41:06 14538

14538

本文檔內(nèi)容介紹了MagicSOPC主板FPGA-IO引腳分配表,供參閱

2018-03-15 15:50:59 6

6 在簡單電路中,當(dāng)頻率較低時,數(shù)字信號的邊沿時間可以忽略時,無需考慮時序約束。但在復(fù)雜電路中,為了減少系統(tǒng)中各部分延時,使系統(tǒng)協(xié)同工作,提高運(yùn)行頻率,需要進(jìn)行時序約束。通常當(dāng)頻率高于50MHz時,需要考慮時序約束。

2018-03-30 13:42:59 14208

14208

介紹FPGA約束原理,理解約束的目的為設(shè)計(jì)服務(wù),是為了保證設(shè)計(jì)滿足時序要求,指導(dǎo)FPGA工具進(jìn)行綜合和實(shí)現(xiàn),約束是Vivado等工具努力實(shí)現(xiàn)的目標(biāo)。所以首先要設(shè)計(jì)合理,才可能滿足約束,約束反過來檢查

2018-06-25 09:14:00 6374

6374 UFDM建議正確的HDL coding風(fēng)格來滿足目標(biāo)器件,討論時序約束和時序收斂。正確的IO約束,IO管腳分配和布局,物理約束,并提供了滿足時序收斂的技巧和讓FPGA工作快速穩(wěn)定的方法。

2018-06-27 09:50:00 1774

1774

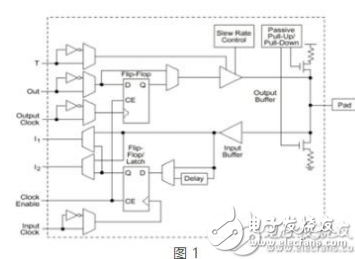

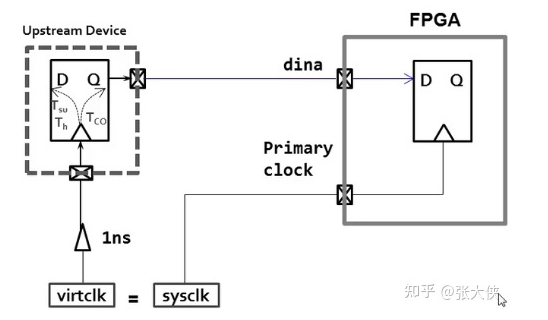

FPGA在與外部器件打交道時,端口如果為輸入則與input delay約束相關(guān),如果最為輸出則output delay,這兩種約束的值究竟是什么涵義,在下文中我也會重點(diǎn)刨析,但是前提是需要理解圖1和圖2建立余量和保持余量。

2019-11-10 10:06:23 3618

3618

偽路徑約束 在本章節(jié)的2 約束主時鐘一節(jié)中,我們看到在不加時序約束時,Timing Report會提示很多的error,其中就有跨時鐘域的error,我們可以直接在上面右鍵,然后設(shè)置兩個時鐘的偽路徑

2020-11-14 11:28:10 2636

2636

今天想和大家一起聊聊 FPGA 的 IO。先說說我當(dāng)年入門的經(jīng)歷吧。國內(nèi)的大學(xué)有 FPGA 開發(fā)條件的實(shí)驗(yàn)室并不太多,當(dāng)年大學(xué)的那幫同學(xué)有的做 ARM,有的做 linux,很少有人做 FPGA,當(dāng)時學(xué) FPGA 僅僅是由于非常渴望的好奇心。所以,在淘寶買了一塊開發(fā)板,就開始了自己的 FPGA 之路。

2020-12-22 13:08:00 10

10 在FPGA 設(shè)計(jì)中,很少進(jìn)行細(xì)致全面的時序約束和分析,F(xiàn)max是最常見也往往是一個設(shè)計(jì)唯一的約束。這一方面是由FPGA的特殊結(jié)構(gòu)決定的,另一方面也是由于缺乏好用的工具造成的。好的時序約束可以指導(dǎo)布局布線工具進(jìn)行權(quán)衡,獲得最優(yōu)的器件性能,使設(shè)計(jì)代碼最大可能的反映設(shè)計(jì)者的設(shè)計(jì)意圖。

2021-01-12 17:31:00 8

8 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應(yīng)包括完整的IO時序約束利序例外約束才能實(shí)現(xiàn)PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點(diǎn)。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 介紹IO口與FPGA管腳對應(yīng)關(guān)系表。

2021-03-18 10:02:26 12

12 有人希望能談?wù)勗谧?b class="flag-6" style="color: red">FPGA設(shè)計(jì)的時候,如何理解和使用過約束。我就以個人的經(jīng)驗(yàn)談?wù)劊?什么是過約束; 為什么會使用過約束; 過約束的優(yōu)點(diǎn)和缺點(diǎn)是什么; 如何使用過約束使自己的設(shè)計(jì)更為健壯

2021-03-29 11:56:24 4379

4379

引言:本文我們簡單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2021-04-27 10:36:59 3126

3126

A 時序約束的概念和基本策略 時序約束主要包括周期約束(FFS到FFS,即觸發(fā)器到觸發(fā)器)和偏移約束(IPAD到FFS、FFS到OPAD)以及靜態(tài)路徑約束(IPAD到OPAD)等3種。通過附加

2021-09-30 15:17:46 4401

4401 本文章探討一下FPGA的時序約束步驟,本文章內(nèi)容,來源于配置的明德?lián)P時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

本文章探討一下FPGA的時序input delay約束,本文章內(nèi)容,來源于配置的明德?lián)P時序約束專題課視頻。

2022-05-11 10:07:56 3462

3462

FPGA端掛載DDR時,對FPGA引腳的約束和選擇并不是隨意的,有一定的約束規(guī)則,一般可以通過利用vivado工具中的pin assignment去選擇合適的位置輔助原理圖設(shè)計(jì)。

2022-07-03 17:20:44 3186

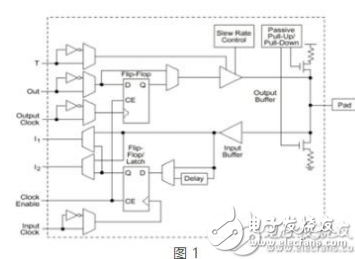

3186 明德?lián)P有完整的時序約束課程與理論,接下來我們會一章一章以圖文結(jié)合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發(fā)器以及FPGA運(yùn)行原理是必備的前提。今天第一章,我們就從D觸發(fā)器開始講起。

2022-07-11 11:33:10 2922

2922

本文章探討一下FPGA的時序input delay約束,本文章內(nèi)容,來源于明德?lián)P時序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

關(guān)于 FPGA 的 IO資源分析共分為三個系列進(jìn)行具體闡述,分別為: IO資源:分析FPGA IO資源的電氣特性; IO邏輯資源:分析FPGA的輸入輸出數(shù)據(jù)寄存器、DDR工作方式、可編程輸入延時

2022-12-13 13:20:06 1099

1099 和set_output_delay命令來設(shè)置FPGA范圍外的延遲值。兩者在含義、約束命令等方面有很多地方是相似的,只不過一個是輸入,一個是輸出,本文還是分開對兩者進(jìn)行講述; 輸入延遲 ?set_input_delay命令設(shè)定FPGA的輸入端口上相對于上游芯片接口時鐘邊沿的輸入路徑延遲(不包括FPGA輸入端口到第一個觸發(fā)器數(shù)據(jù)輸

2023-01-01 11:50:07 1747

1747 Pad-to-Setup:也被稱為OFFSET IN BEFORE約束,是用來保證外部輸入時鐘和外部輸入數(shù)據(jù)的時序滿足FPGA內(nèi)部觸發(fā)器的建立時間要求的。如下圖TIN_BEFORE約束使得FPGA

2023-02-15 11:52:33 1216

1216 《XDC 約束技巧之時鐘篇》中曾對 I/O 約束做過簡要概括,相比較而言,XDC 中的 I/O 約束雖然形式簡單,但整體思路和約束方法卻與 UCF 大相徑庭。加之 FPGA 的應(yīng)用特性決定了其在接口

2023-04-06 09:53:30 729

729 在進(jìn)行FPGA的設(shè)計(jì)時,經(jīng)常會需要在綜合、實(shí)現(xiàn)的階段添加約束,以便能夠控制綜合、實(shí)現(xiàn)過程,使設(shè)計(jì)滿足我們需要的運(yùn)行速度、引腳位置等要求。通常的做法是設(shè)計(jì)編寫約束文件并導(dǎo)入到綜合實(shí)現(xiàn)工具,在進(jìn)行

2023-04-27 10:08:22 768

768 前面幾篇文章已經(jīng)詳細(xì)介紹了FPGA時序約束基礎(chǔ)知識以及常用的時序約束命令,相信大家已經(jīng)基本掌握了時序約束的方法。

2023-06-23 17:44:00 1260

1260

FPGA開發(fā)過程中,離不開時序約束,那么時序約束是什么?簡單點(diǎn)說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設(shè)定的時鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

FPGA設(shè)計(jì)中,時序約束對于電路性能和可靠性非常重要。

2023-06-26 14:53:53 820

820

電子發(fā)燒友網(wǎng)站提供《7系列FPGA Select IO資源用戶指南.pdf》資料免費(fèi)下載

2023-09-15 10:26:12 1

1

image-20220820220754710

image-20220820220754710 image-20220821194158470

image-20220821194158470 image-20220904205339367

image-20220904205339367 image-20220904205430995

image-20220904205430995 image-20220904211616829

image-20220904211616829 image-20220904232921974

image-20220904232921974 電子發(fā)燒友App

電子發(fā)燒友App

評論