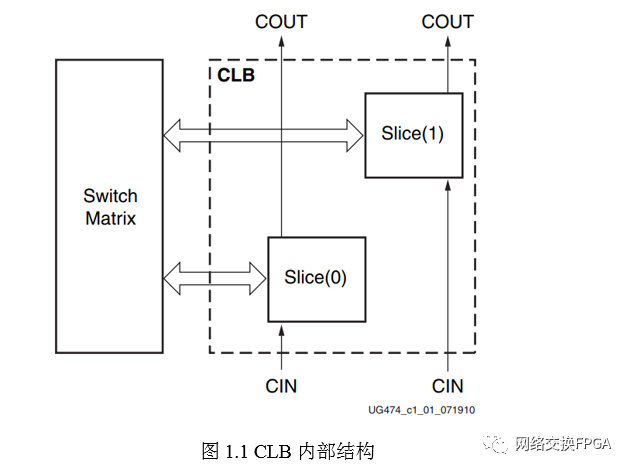

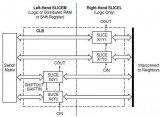

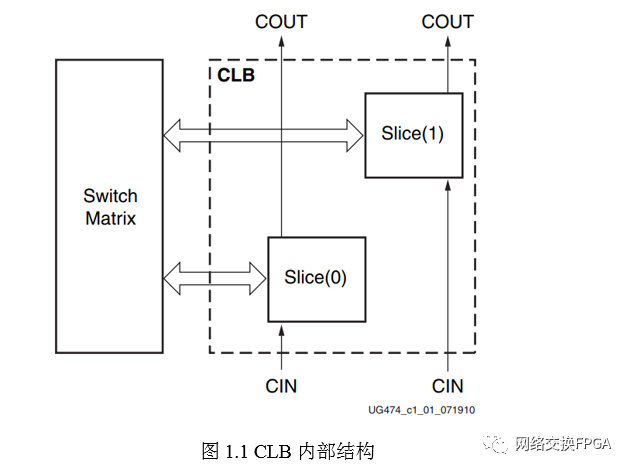

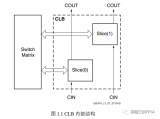

的不同而不同,但是每個CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2個 相同的SliceL或則一個SliceL和一個SliceM構成。每個Slice不僅可以用于實現組合邏輯、時序邏輯。其中

2020-11-02 17:18:05 5016

5016

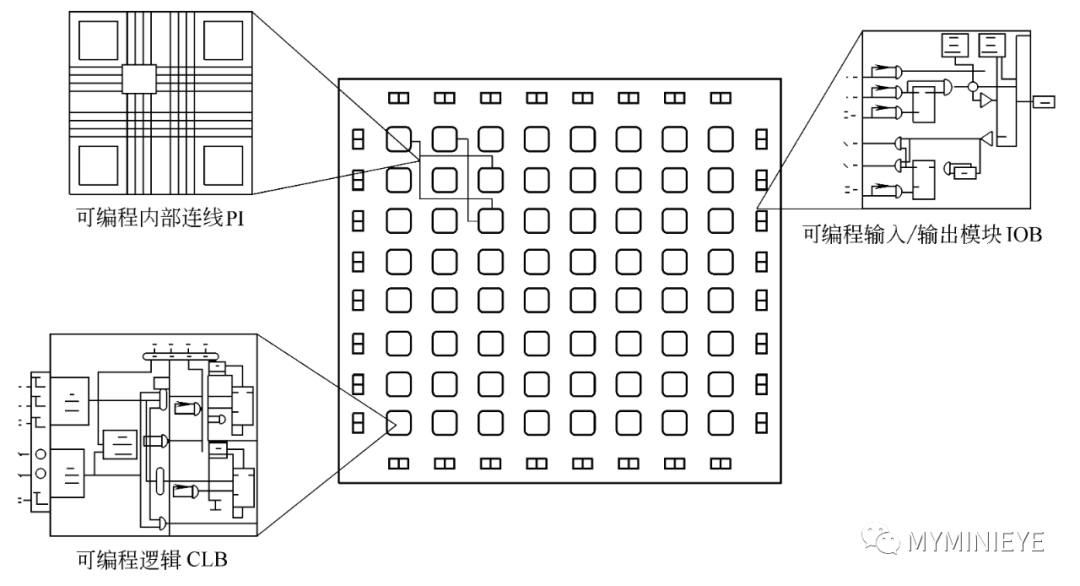

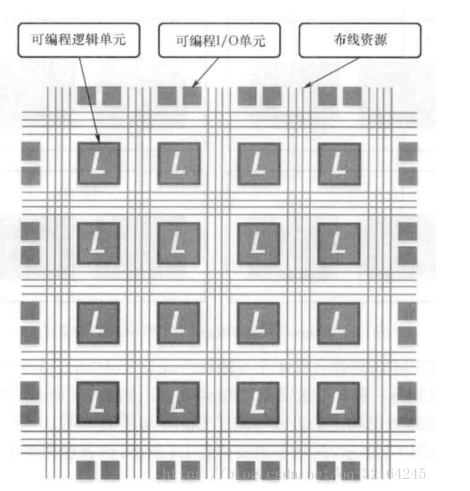

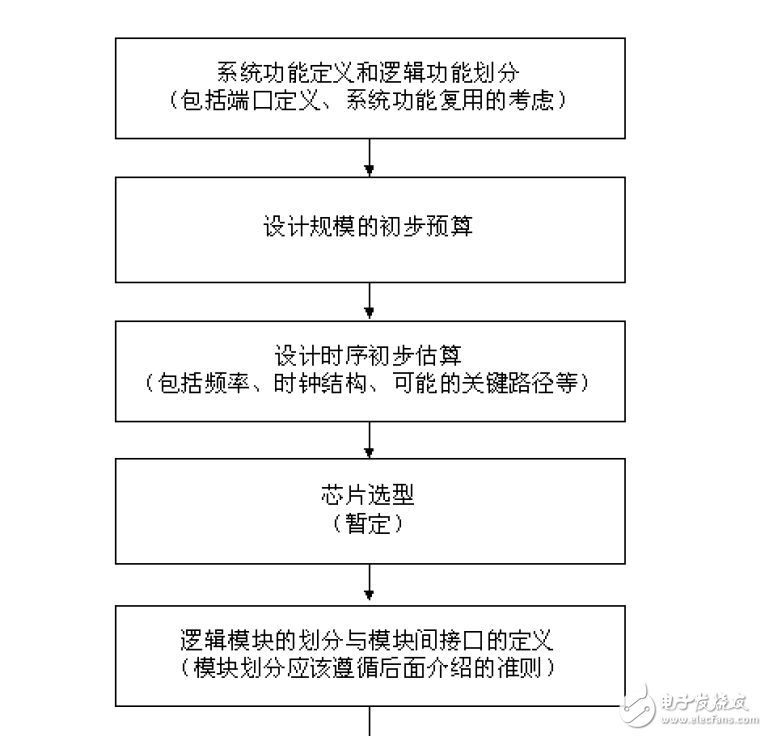

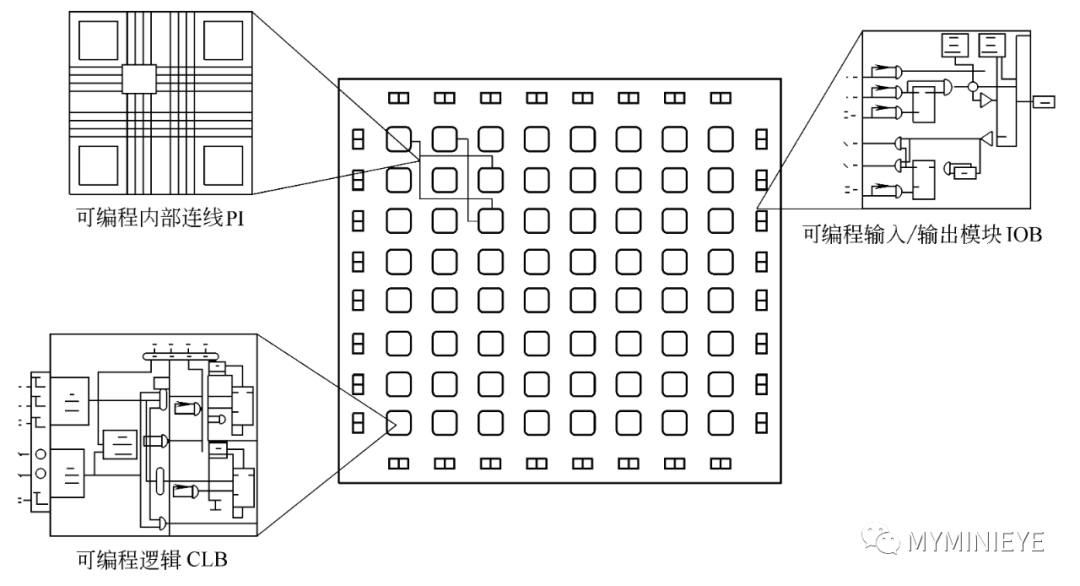

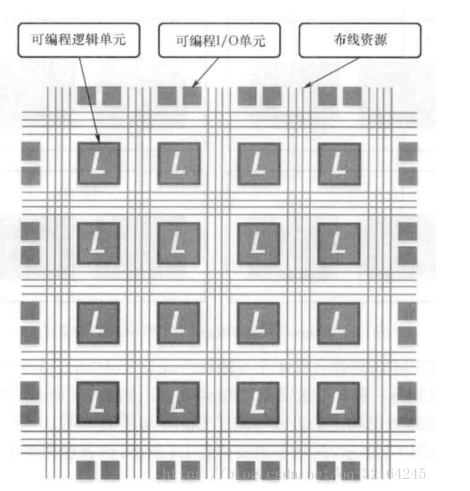

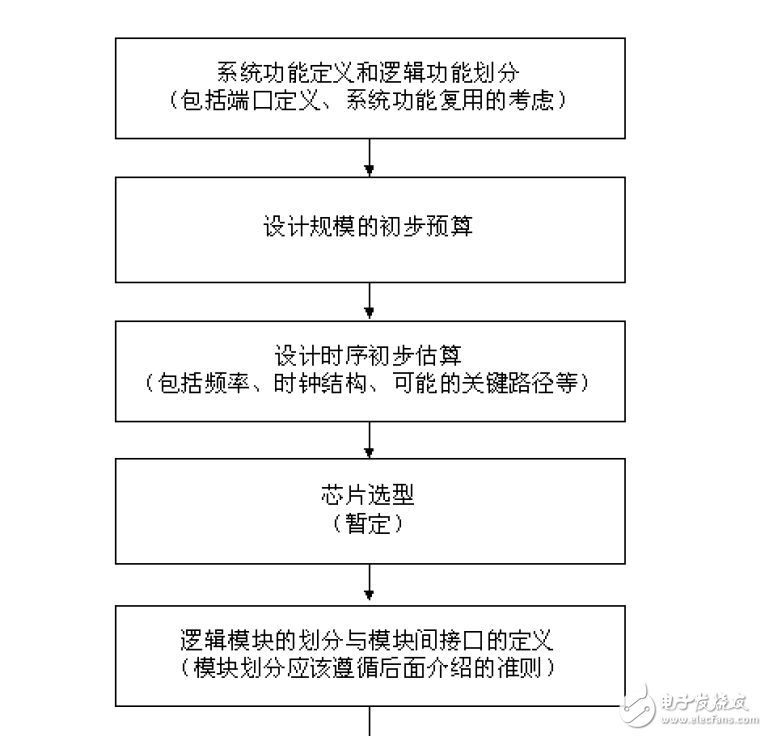

研究背景及基礎知識 FPGA是實現高性能計算與網絡的重要工具,得益于其高度的并行性與用戶可編程的特性,FPGA得到了越來越廣泛的應用。FPGA由CLB(Configurable Logic

2020-11-23 13:14:20 8757

8757

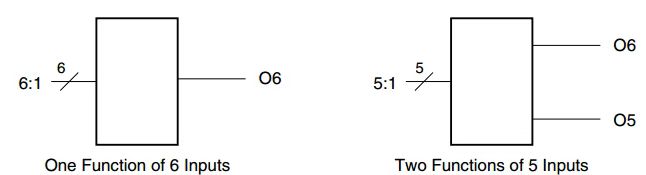

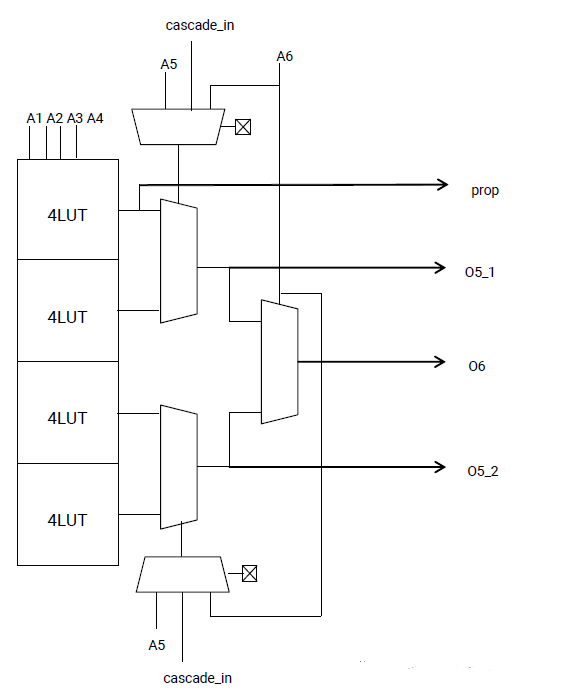

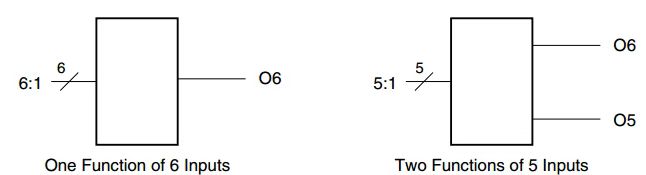

。利用xilinx器件中LUT的結構特征,設計出的乘法器不但能靈活適應數據位寬,而且能最大限度降低LUT資源使用。 Xilinx ultrascale器件LUT結構 在這里簡要介紹一下

2020-11-30 11:45:21 2385

2385

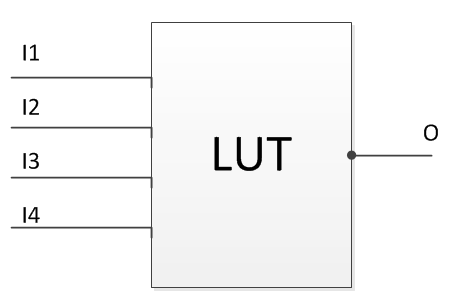

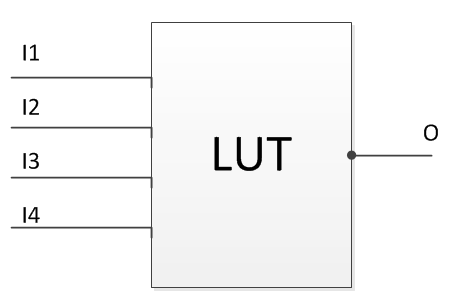

LUT中文名字叫查找表。以7系列的FPGA為例,每一個Slice里面有四個LUT。FPGA就是通過LUT實現大量的組合邏輯,以及SLICEM里面的LUT還可以構成RAM,Shift Register,以及Multiplexers。這篇文章我們一起來學習LUT如何構成組合邏輯。

2023-03-13 10:28:06 2053

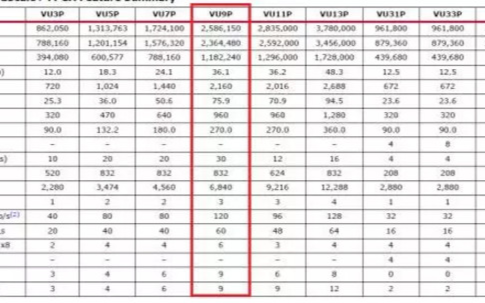

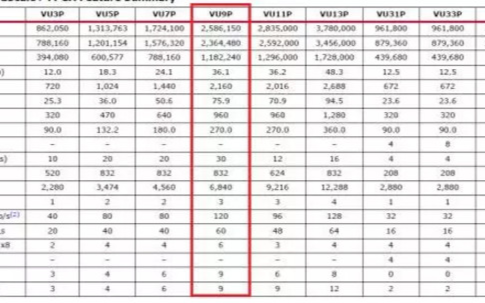

2053 在選擇FPGA時,關注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因為它們是FPGA架構中的兩個核心資源,對于設計的性能和資源利用至關重要。

2023-11-21 15:03:06 548

548

FPGA 如何估算程序所需的資源?是不是要把輸出接到FPGA的PIN上后build,才算是程序所需的資源?因為我有個比較復雜的程序,沒有output到FPGA上,LUT使用為8000+一旦output到FPGA上,LUT使用為8W+.是不是此時的LUT使用量才是程序真正所需的?

2017-01-19 09:09:19

下面給大家介紹FPGA LUT的結構

2018-07-09 04:57:10

用于xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA如何將xilinx LUT作為移位寄存器?什么是xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA的CLB結構。這個FPGA上有哪些額外的原語?

2020-06-16 16:48:59

`在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。4輸入查找表可以看成是具有4位地址1位數據的存儲器

2018-07-30 18:11:19

所示的內容。Design Summary--------------Logic Utilization:1. FPGA資源利用率Number of Slice Flip Flops: 11,555

2018-08-17 09:44:25

、ROM和FIFO等結構。在實際應用中,芯片內部塊RAM的數量也是選擇芯片的一個重要因素。5. 豐富的布線資源布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度

2014-08-16 10:32:45

資料來源:http://wenku.baidu.com/link?url= ... ImZCXVVkKhd9oFsSmHC第一部分: 查找表LUT FPGA是在PAL、GAL、EPLD、CPLD等

2017-05-09 15:04:46

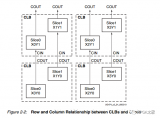

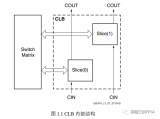

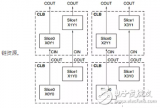

是高度靈活的,可以對其進行配置以便處理組合邏輯、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個) 相同的Slice和附加邏輯構成,如圖1-3所示。每個CLB模塊

2017-05-09 15:10:02

、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成,如圖1-3所示。每個CLB模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式

2023-05-30 20:53:24

II、Vivado等)、仿真軟件(ModelSim等)的使用5、熟悉FPGA設計流程(仿真,綜合,布局布線,時序分析)。6、熟練掌握資源估算(特別是slice,lut,ram等資源的估算)。7、同步

2020-10-22 17:08:15

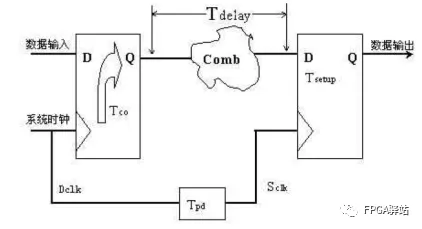

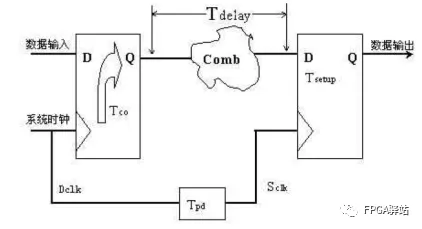

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2021-07-25 11:09:06

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2021-07-26 14:47:48

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2021-11-22 10:04:03

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2021-07-09 14:34:18

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2021-08-10 14:51:33

1. 面積與速度的平衡與互換這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數

2020-08-02 10:45:07

設計技巧..............................................................353.8.2 解剖Block SelectRAM內部結構....................................343.8.1 LUT如何配置成組合邏輯電路 揭開門數增加邏輯級數未變 但資源

2012-08-11 11:43:17

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35343.8.1 LUT如何配置成組合邏輯電路 揭開 門數增加 邏輯級數未變 但資源占用減少

2017-12-08 14:33:54

嗨,是否有全局實現指令(屬性)會強制實現工具將LUT和FF放在單獨的片中(對FF或LUT使用單個片)?這是非理想的,也是我所知道的資源浪費......但我正在開發耐輻射設計,并且希望將FPGA的所有

2018-10-29 11:48:56

你好。我正在寫一篇技術論文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的資源。資源可以是晶體管數量,柵極數,芯片面積大小等等。我在一個網站上聽說LUT需要2.5倍的“FPGA門”,但

2019-02-27 13:49:58

你好,當我在原理圖視圖中單擊LUT時,它會按預期顯示逆變器。但我想知道它是通過逆變器在Xilinx FPGA上實現還是實際上原理圖不等同于FPGA的真相?謝謝,?以上來自于谷歌翻譯以下為原文Hi

2019-01-29 09:22:50

PAR報告中的“占用切片數量”與完全使用的LUT-FF對之間是否存在任何關系。例如,有兩種設計使用相同數量的LUT和FF(以及其他資源) ),是否具有較大的完全使用LUT-FF比率較小的“占用切片數量

2018-11-01 16:11:30

Slice包含4個LUT,因此Slices可用于最多4個功能塊。但是為什么64位Init值設置Slice的所有4個LUT的功能(在下面的例子中標記為紅色)總是在切片的每個LUT實例中完全改變,而

2019-03-08 12:03:30

大家好,如果我想使用spartan 6 FPGA實現簡單的“和”門,請說。我理解“和”門將被模擬到查找表中。有人可以對此有所了解嗎?和門真值表是否被移植到LUT?LUT中是否有pmos和nmos

2019-08-09 09:16:35

用于Virtex 6設計的可重配置LUT(CFGLUT)可能被封裝到FPGA的輸出邏輯OLOGICE1而不是SLICEM上的LUT。我的設計涉及使用存在于與CFGLUT相同的片中的FF(用于流水線

2018-10-22 11:04:46

前言FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元(IOB)基本可編程邏輯單元(configurable logic block,CLB) 完整的時鐘管理嵌入塊式RAM豐富的布線資源內嵌

2021-07-26 06:54:01

或2 個)相同的Slice 和附加邏輯構成,每個CLB 模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式RAM 和分布式ROM。3. 數字時鐘管理模塊(DCM)業內大多數 FPGA 均提供

2012-03-08 11:03:49

`FPGA的邏輯單元_CLB_項目代碼文件`

2021-03-31 11:18:02

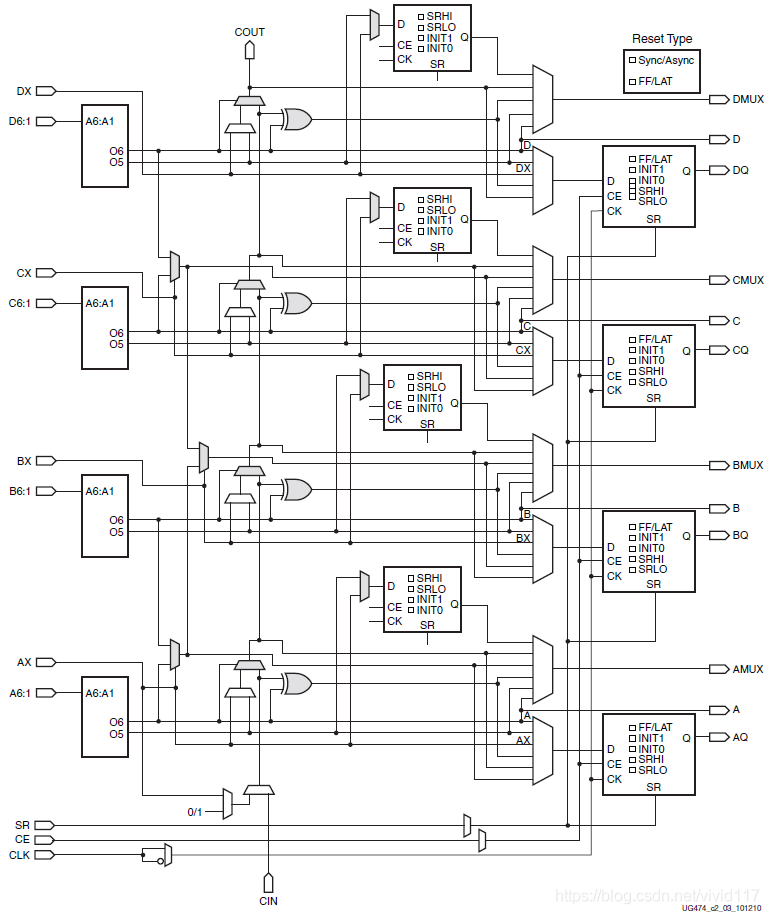

LUT:(look up table) 查找表今天我要講的與FPGA CLB相關的第一節LUT。根據上一節課的課程大綱,講CLB應該是講SLICEL(SLICEM)。不過當我打開用戶手冊,看了一下

2021-07-29 08:13:55

... the LUT5_L specifies that the only connections from the LUT5 is within a slice or CLB". I'm

2018-10-17 14:26:28

嗨朋友我是Xilinx FPGA的新手,我在Altera FPGA上工作了很長時間。我正在使用Spartan 6,目前正在閱讀有關Spartan 6 CLB架構詳細信息的CLB配置u384手冊。我

2019-08-08 07:13:38

+ 2FF? Or does this mean each slice have 4 pairs of LUT Flip Flop?Thanks,

2018-10-23 10:21:12

關于FPGA芯片資源介紹不看肯定后悔

2021-09-18 08:53:05

嗨,我可以在Virtex-5的任何片中實現CFGLUT5原語,還是僅限于SLICE_M中的LUT?謝謝,Hooman

2020-05-28 06:32:38

一、查找表LUT就是查找表,對于4輸入的LUT而言,實際上就是4位地址位,一位數據位的存儲器,能夠存儲16位數據,所以我們在FPGA設計中可以用LUT組建分布式的RAM。這樣也可以解釋我們在設計中

2021-07-28 08:42:17

在PlanAhead中的一個Slice中發現了LUT6實例的BEL位置的差異FPGA編輯器(由于沒有放置FF,因此額外路由的成本會再次進入Slice適當)。一個簡單的例子:我定義 LUT1 BEL

2020-06-11 15:18:53

是兩片,都在同一個CLB中。彈跳的紅線跨越是失敗的道路。正如你可以看到從下面的4條路線切片都有一個3的扇出,一個用于上部切片中的每個LUT它路由到。所以你在截圖中看到的是12條彩色路徑總數,其中只有1個

2018-10-09 15:31:53

資源組成的可編程邏輯,用于實現高密度邏輯,被稱為現場可編程門陣列(FPGA)。FPGA也稱為可編程ASIC,由可配置邏輯塊(CLB)、IO塊(IOB)和可編程互連組成。現代FPGA甚至包括乘法器

2022-10-27 16:43:59

我正在使用vertex fpga來實現我的設計。我可以寫一個約束文件來為我的設計選擇特定的CLB / CLB。謝謝以上來自于谷歌翻譯以下為原文i am using vertex fpga

2019-07-18 07:51:49

喜據我所知,有些xilinx FPGA具有DSP Slice(DSP48E)。在fpga設計摘要中,我看到切片寄存器,切片LUT,占用切片等以及DSP48E的單獨行。我的問題是 - 1)DSP48E

2019-04-04 06:36:56

(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。 本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析

2019-06-17 09:03:28

組成。切片成對分組,并按列排列。設備中 clb 的數量根據供應商和設備家族的不同而不同。例如,Xilinx make Spartan 3E FPGA 包含四個切片。每個片由兩個 lut 和兩個存儲元素

2022-04-03 11:20:18

fpga:Spartan-6 xc6slx150-3fgg484我在資源密集型處理系統中使用了幾百個8位加法器,因此資源使用很重要。用于加法器減法器的核心生成器為具有2個8位輸入和8位輸出,0延遲

2019-04-03 15:55:35

嘿,為了在Zynq設備上對一種算法的不同實現進行簡單比較,我想為每種實現的資源使用創建一個指示符,例如CLB的使用。因此,獲得基本元素CLB,DSP48E1和BRAM36K的面積指標會很好。在

2020-07-25 11:04:42

Xilinx 公司的 FPGA 器件中,CLB 由多個(一般為 4 個或 2 個) 相同的 Slice 和附加邏輯構成,如圖 1-3 所示。每個 CLB 模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為

2020-05-01 07:30:00

`Xilinx片子一般從65nm工藝以上就使用6輸入LUT,新器件的Slice包含4個6輸入LUT和8個寄存器等。Cyclone V的片子是6輸入LUT嗎?如果是的話,每個Cyclone的基本邏輯

2016-10-26 10:58:05

在使用ISE進行實現過程中,占用slice的資源較多,如圖中所示,想用unrelated logic部分,期望能夠將slice資源均衡使用,而折騰了好久,改了好多綜合、map等的設置,可都

2015-02-28 14:55:25

嗨,我正在使用Kintex-7 XC7K160T-2FFG676C設備和Vivado 2013.4。由于我無法通過資源利用來實現我的設計,因此我附加了合成后生成的資源利用率報告。根據綜合利用率報告

2020-08-05 12:48:02

此課程將教會你:1)描述Spartan-6 和Virtex-6 FPGA的6輸入LUT和CLB建設的所有功能;2)指定Spartan-6 和Virtex-6的CLB資源和可用的Slice配置;3)定義可用的RAM和DSP資源塊;4)正確設計I/O塊和S

2010-12-14 15:09:48 0

0 FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達芯片內部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 在基于FPGA的商用設計中,設計師通常會將查找表(LUT)的資源占用率上限設置為80%左右,以便為未來升級和功能改進留有資源,并可讓時序收斂更容易。余下約20%的空閒LUT留下了空余的佈

2011-08-21 18:01:51 2562

2562

一個寫寫代碼,調調時序的小工程師的級別。我想,這應該不是我們所有年輕人的一個追求。 1.1 CLB的初探 首先CLB的最基本資源分為兩種,一種是實現組合邏輯資源功能的,一般稱為LUT。XILINX的LUT是6輸入查找表。一種是Flip-flop,也就是經常聽課大家聽說的FF,我就

2017-02-08 10:10:34 214

214

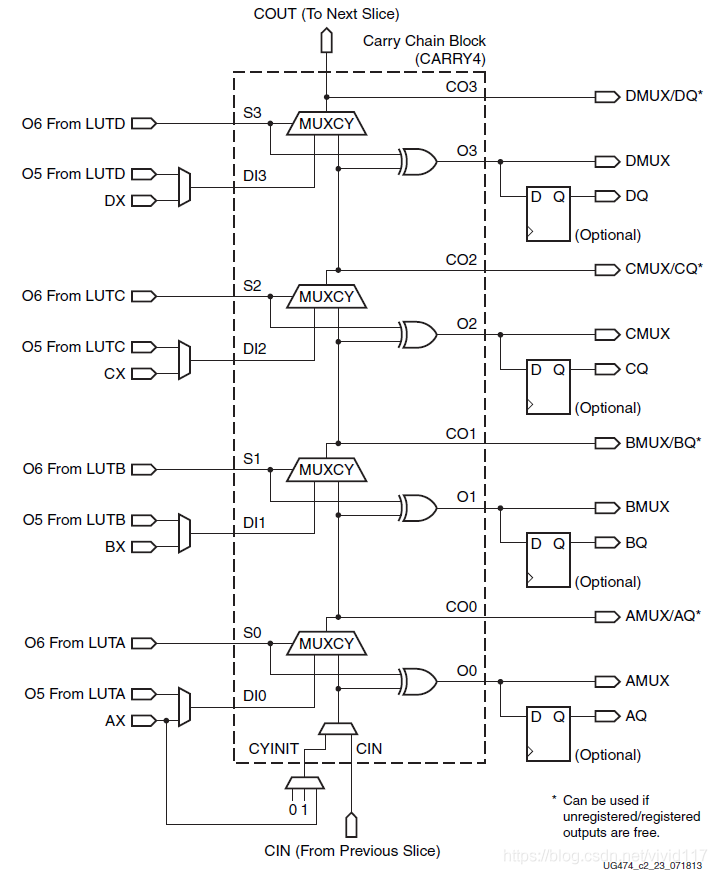

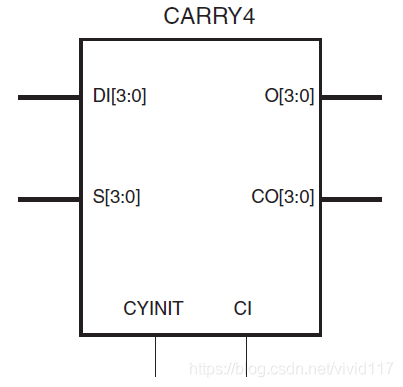

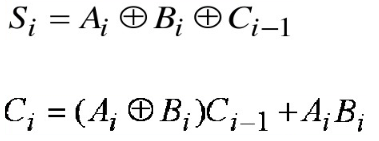

7系列FPGA是Xilinx新推出的基于28nm工藝的FPGA,其中包含三個系列:Artix、Kintex和Virtex。因項目要使用kintex7為平臺做設計,需要對其內部結構做了研究,首先從CLB(Configurable Logic Block)開始

2017-02-10 16:13:38 5090

5090

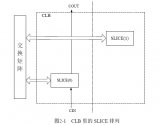

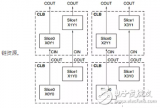

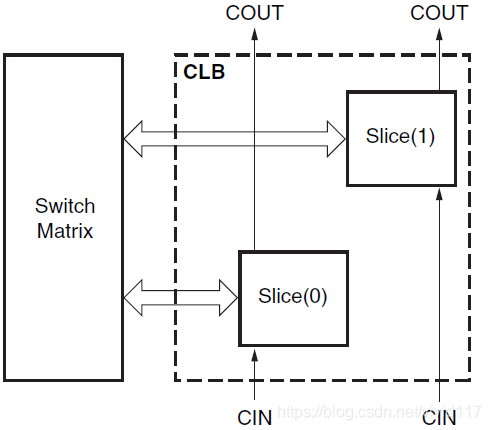

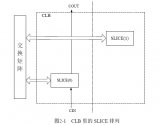

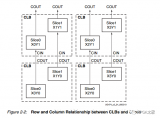

Spartan-6每個CLB模塊里包含兩個SLICE。CLB通過交換矩陣和外部通用邏輯陣列相連,如圖2-1和圖2-2所示。底部的SLICE標號為SLICE0,頂部的SLICE標號為SLICE1。兩個SLICE沒有直接連接。

2017-02-11 09:53:11 741

741

在賽靈思Spartan-3、3E等系列的FPGA中,其邏輯單元CLB中一般含有不同數量的單端口RAM(SRAM)或者雙端口RAM(DRAM),這里的“單”或者“雙”是由我們開發人員定義的。

2017-02-11 13:56:11 6348

6348

插,以模擬更大容量的LUT。這樣,您就可以實現比1000 字 LUT更高的數值分辨率。此外,通過這種方法,僅需 1 個 BRAM、1個嵌入式乘法器(或DSP48),以及少數幾個CLB芯片便可實施控制邏輯,因此LUT的使用成本變得更加合理化。而且,從信噪比的角度來看,其數值精度也是非常讓人滿意。

2017-11-25 12:05:01 2993

2993

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成。

2018-05-10 11:43:00 25053

25053

FPGA中的基本邏輯單元是CLB模塊,一個CLB模塊一般包含若干個基本的查找表、寄存器和多路選擇器資源,因此FPGA中的邏輯表達式基于LUT的。

2018-07-28 09:58:01 64941

64941

第二種Slice叫SLICEM,電路結構如下。除了LUTS與SLICEL的LUTS不同之外,其余結構都一樣。這就是SLICEM與SLICEL之間的區別,利用SLICEM的LUTS還可以構成RAM,ROM,以及Shift Registers(移位寄存器)。

2018-10-18 17:04:41 10485

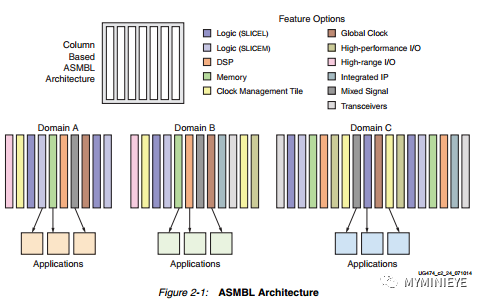

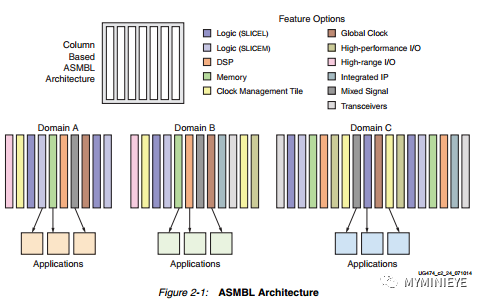

10485 現在的FPGA里面有很多存儲資源,DSP(數字信號處理)資源,布線通道,I/O資源,當然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構。

2018-10-22 11:00:43 5270

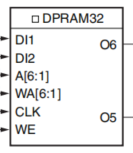

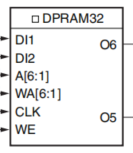

5270 一個SLICEM里面有4個LUT,他們可以組合得到多種大小的RAM。首先就是四端口的32x2bits的RAM,支持一次性讀寫2bits,原理如下圖。四個LUT的寫數據端口DI1,DI2,寫使能WE,寫地址WA共用,稱為寫控制信號共用。讀地址A分別控制。

2018-10-30 10:28:40 10404

10404

本視頻介紹了7系列CLB架構,包括:LUT,觸發器,專用多路復用器,進位鏈和其他資源。

2018-11-27 06:39:00 3290

3290 本視頻介紹了7系列FPGA的DSP Slice功能。

此外,還討論了Pre-Adder和Dynamic Pipeline控制資源。

2018-11-26 06:02:00 6700

6700 Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

一個CLB包含兩個Slice,兩個Slice分別位于獨立的列,有各自的進位鏈,他們相互不連接。每個CLB連接到一個Switch matrix上已完成布線。CLB中底部的Slice為Slice0,上部的為Slice1。

2019-06-18 08:00:00 0

0 管腳是FPGA重要的資源之一,FPGA的管腳分別包括,電源管腳,普通I/O,配置管腳,時鐘專用輸入管腳GCLK等。

2019-06-28 14:34:07 3703

3703 CLB(Configurable Logic Block):FPGA最基本的組成單元,可以實現基本的組合邏輯和時序電路。其中,LUT(Lookup Tables)是實現組合邏輯的部分,可以實現n個輸入的任意組合邏輯運算(不同型號的FPGA有所不同,下圖的例子中為6個輸入)。

2019-09-27 15:18:06 7663

7663

這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數。

2019-11-02 10:56:01 1588

1588

結構配置到FPGA具體的哪個位置。需要說明的是,FPGA里任何硬件結構都是按照橫縱坐標進行標定的,圖中選中的是一個SLICE,SLICE里面存放著表和其他結構,它的位置在X50Y112上。不同的資源的坐標不一樣,但是坐標的零點是公用的。 在FPGA里布局需要考慮的問題是,如何將這些

2020-10-25 10:25:31 7659

7659

在使用 FPGA 過程中,通常需要對資源做出評估,下面簡單談談如何評估 FPGA 的資源。 FF 和 LUT 的數目:這個在寫出具體代碼之前,初學者通常沒法估算,但資深 FPGA 工程師會估算

2020-12-28 07:59:00 8

8 在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。

2020-12-29 17:27:22 14

14 SRL(移位寄存器)資源,在FPGA中都有,不過是叫不同的名字。Xilinx FPGA內部的LUT有個特殊功能,就是可以配置成可變長度SRL。

2020-12-31 16:45:35 8

8 DDR3。 2.FPGA架構設計問題 我們知道,FPGA片上分布著各種資源,如時鐘,serdes,RAM,LUT,IO等。在進行FPGA規劃時候,應當需要知道項目設計需求,以及需求各模塊之間的數據交織情況,這樣可以避免

2021-01-07 10:15:31 4645

4645

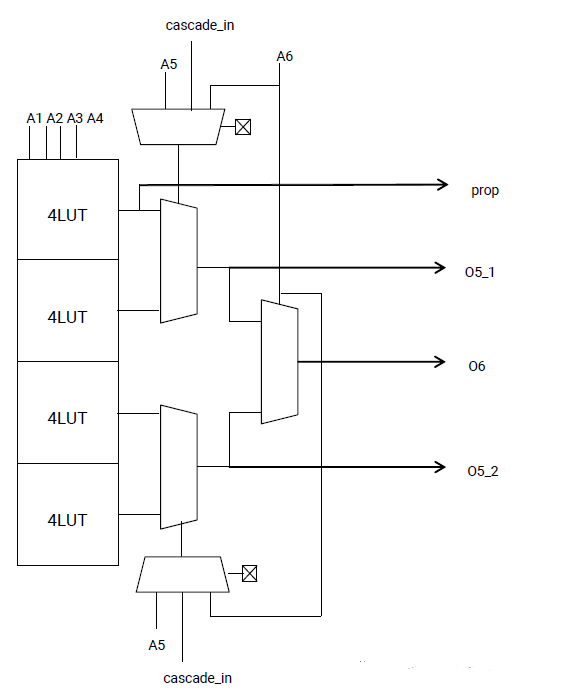

在Versal ACAP中,同一個CLB內同一列的LUT是可以級聯的,這是與前一代FPGA UltraScale+系列的一個顯著不同點。這里我們先看看Versal中LUT的結構,如下圖所示(圖片來源

2021-03-27 09:52:08 2711

2711

面積通常指一個設計消耗FPGA/CPLD的邏輯資源的數量,通常用可消耗的FF(觸發器)和LUT(查找表)來衡量。速度指設計在芯片上穩定運行所能達到的最高頻率,這個頻率由設計的時序狀況來決定,以及設計滿足的時鐘要求

2022-02-16 16:21:28 855

855

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成。

2022-04-24 14:48:55 3407

3407 這里的面積指一個設計消耗FPGA/CPLD的邏輯資源的數量,對于FPGA可以用消耗的FF(觸發器)和LUT(查找表)來衡量,更一般的衡量方式可以用設計所占的等價邏輯門數。

2022-10-17 17:50:17 637

637 FPGA是一種數字集成電路芯片,名稱為“現場可編程邏輯門陣列”FPGA的一項重要特點是其可編程特性,即用戶可通過程序指定FPGA實現某一特定數字電路,FPGA的的組成有CLB,IOB,可編程互聯資源,SRAM,DSP,時鐘管理模塊,CLB內包含有Filp-Flop和LUT等,可實現某些組合或時序邏輯電路;

2023-03-21 14:01:05 412

412 的不同而不同,但是每個CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2個 相同的SliceL或則一個SliceL和一個SliceM構成。每個Slice不僅可以用于實現組合邏輯、時序邏輯。其中,SliceM還可以配置為分布式RAM和分布式ROM

2023-03-21 14:14:41 554

554

我們知道FPGA由LUT、IO接口、時鐘管理單元、存儲器、DSP等構成,我覺得最能代表FPGA特點的就是LUT了。當然不同廠家、同一廠家不同階段FPGA的LUT輸入數量是不同的,隨著技術的發展,LUT的輸入數量也在增加。

2023-05-25 09:29:18 2444

2444

首先開門見山的回答這個問題——LUT的作用是 **實現所有的邏輯函數** ,也就是類似于計算Y=A&B+C+D之類的算式結果!

2023-06-28 10:56:39 1615

1615

在7系列FPGA中,將近2/3的SLICE是SLICEL,其余的是SLICEM[1],也就是說,FPGA內2/3的資源在bitstream文件下載后,其邏輯功能就無法更改了,除非修改代碼并生成新的bitstream文件。

2023-08-26 14:18:37 1039

1039

FPGA的BRAM和LUT等資源都是有限的,在FPGA開發過程中,可能經常遇到BRAM或者LUT資源不夠用的情況。

2023-08-30 16:12:04 949

949

電子發燒友App

電子發燒友App

評論