數(shù)字硬件建模SystemVerilog-程序塊 (procedural blocks)

?

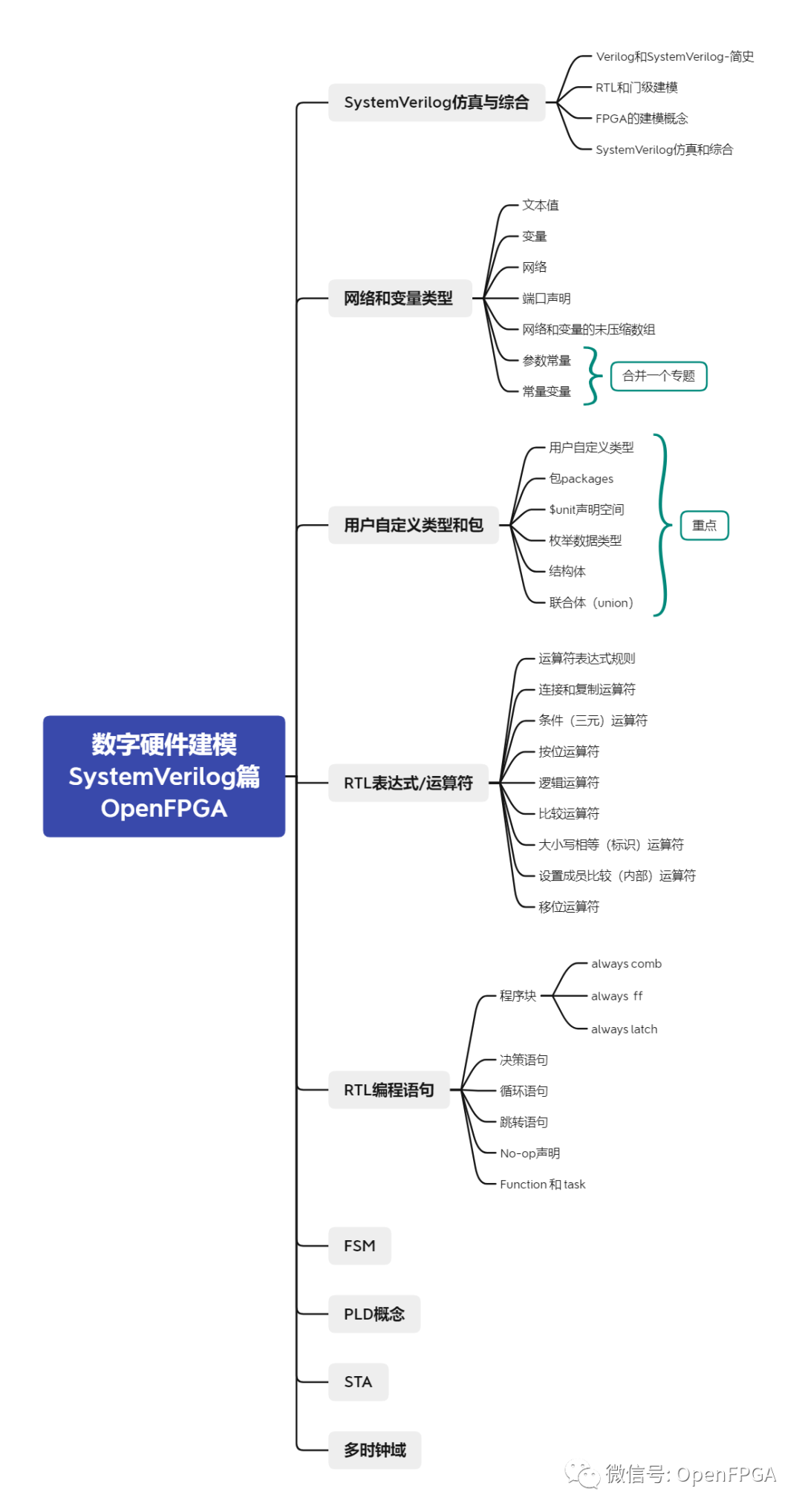

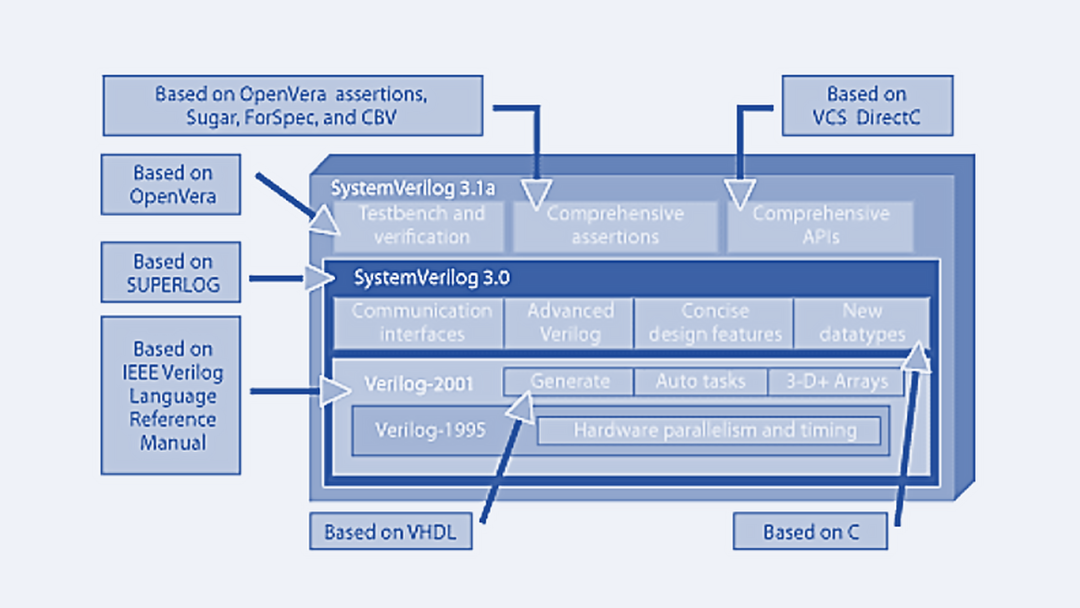

經(jīng)過幾周的更新,SV核心部分用戶自定義類型和包內(nèi)容已更新完畢,接下來就是RTL編程語句。

程序塊是編程語句的容器。程序塊的主要目的是控制何時(shí)應(yīng)執(zhí)行編程語句,例如每當(dāng)時(shí)鐘上升沿出現(xiàn)時(shí),或每當(dāng)信號(hào)或總線改變值時(shí)。SystemVerilog有兩種主要類型的程序塊: initial 程序塊和always 程序塊。

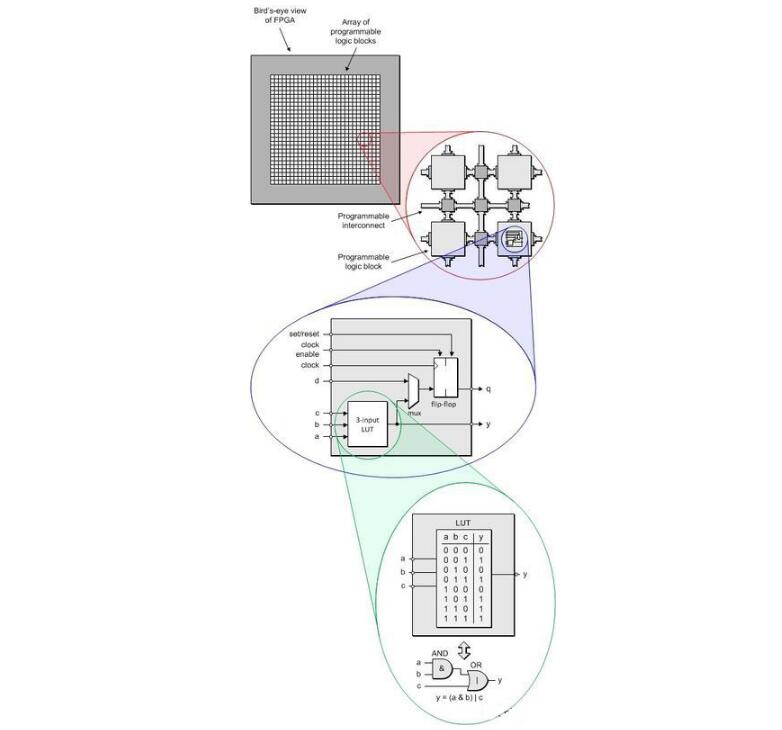

initial 程序是一種驗(yàn)證結(jié)構(gòu);綜合編譯器不支持。但是有一個(gè)例外是,綜合編譯器支持使用readmemh系統(tǒng)任務(wù)加載內(nèi)存塊或分配給特定內(nèi)存地址的 initial 程序。FPGA綜合器可能還允許使用 initial 程序?qū)υO(shè)備通電狀態(tài)進(jìn)行建模,本文不討論或使用 initial 程序,因?yàn)樗鼈儾挥糜趯TL功能進(jìn)行建模。

過程是無限循環(huán)。它們執(zhí)行編程語句,完成后自動(dòng)重新開始。一般的概念是,當(dāng)電源打開時(shí),硬件在做一些連續(xù)的事情。這種連續(xù)行為是使用always 程序建模的。

SystemVerilog有四種類型的always 程序:使用關(guān)鍵字always的通用過程和使用關(guān)鍵字always_ff, always_comb 和 always_latch的專用always 過程。

always 程序塊可用于多種類型建模,包括可綜合RTL模型、抽象行為模型(如不會(huì)綜合的RAM)以及驗(yàn)證代碼(如時(shí)鐘振蕩器或連續(xù)響應(yīng)檢查器)。雖然通用always程序的靈活性使其在各種建模和驗(yàn)證項(xiàng)目中都很有用,但同樣的靈活性意味著軟件工具不知道always的預(yù)期用途是什么,什么時(shí)候用于可綜合的RTL模型。為了將RTL模型準(zhǔn)確地轉(zhuǎn)換為ASIC或FPGA設(shè)備,綜合器對通用always程序設(shè)置了許多編碼限制。

專用的RTL程序。Always_ff、always_comb和always_latch專用always程序塊的行為與通用always程序塊相同,但會(huì)施加綜合所需的特殊編碼限制。這些額外的限制有助于確保RTL仿真的行為與實(shí)際ASIC或FPGA的門級(jí)行為相匹配。正如這些專用程序的名稱所表明的,Always_ff對仿真觸發(fā)器等時(shí)序邏輯器件施加了某些綜合限制。Always_comb為建模組合邏輯(如解碼器)施加了某些綜合限制,always_latch為建模鎖存行為施加了某些綜合限制。后面會(huì)詳細(xì)說明每個(gè)過程塊功能及驗(yàn)證。

敏感列表

always 程序告訴仿真,應(yīng)該“always”評(píng)估被建模的功能(一個(gè)無限循環(huán)),但仿真和綜合都需要了解更多信息,以便準(zhǔn)確地建模硬件行為。這些工具還需要知道何時(shí)執(zhí)行程序塊中的語句。對于RTL建模,時(shí)間要么在表示時(shí)序邏輯的時(shí)鐘邊沿上,要么在表示組合邏輯或鎖存邏輯的過程更改值所使用的任何信號(hào)上。

為了控制在可綜合RTL模型中何時(shí)執(zhí)行編程語句,程序是以敏感列表開始,敏感列表是一個(gè)信號(hào)列表,值的變化將觸發(fā)程序的執(zhí)行。通用always和RTL特定always_ff程序要求RTL設(shè)計(jì)工程師明確規(guī)定靈敏度列表。RTL特定的always_comb和always_latch程序?qū)⑼茢喑鲆粋€(gè)隱式靈敏度列表。

顯式指定的敏感度列表與@標(biāo)記一起引入,口頭上稱為“at”。在可綜合RTL建模中,靈敏度列表包含一個(gè)或多個(gè)網(wǎng)絡(luò)或變量名的列表。名稱可以用逗號(hào)(,)或關(guān)鍵字”or”分隔。

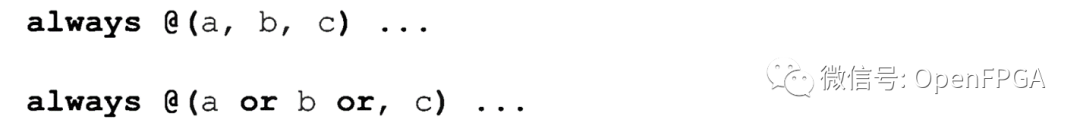

以下兩個(gè)明確的敏感度列表功能相同:

在敏感度列表的上下文中,or關(guān)鍵字只是一個(gè)分隔符:它不是or操作。逗號(hào)與關(guān)鍵字or的使用取決于用戶的偏好。一種風(fēng)格在功能上并不優(yōu)于另一種風(fēng)格。

靈敏度列表還可以指定標(biāo)量(l位)信號(hào)的特定邊沿,該邊沿將觸發(fā)always 程序。邊沿由關(guān)鍵詞posedge和negedge指定,邊沿靈敏度對于基于時(shí)鐘的功能非常重要:

always?@(posedge?elk?or?negedge?rstN)…

posedge關(guān)鍵字是“正邊沿”的縮寫,negedge是“負(fù)邊沿”的縮寫。正邊沿是任何可能被硅晶體管感知為正向過渡的過渡。因此,posedge將在0-to-1、0-to-z、0-to-x、z-to-1、x-to-l、z-to-x和x-to-z轉(zhuǎn)換時(shí)觸發(fā),相反,negedge將在1-to-0、1-to-z、1-to-x、z-to-0、x-to-0、z-to-x和x-to-z轉(zhuǎn)換時(shí)觸發(fā).

時(shí)序邏輯靈敏度。時(shí)序邏輯元件,如觸發(fā)器,在時(shí)鐘邊沿觸發(fā),通常是該時(shí)鐘的上升沿。(一些ASIC和FPGA設(shè)備具有在時(shí)鐘下降沿觸發(fā)的組件,很少有在時(shí)鐘兩側(cè)觸發(fā)的組件。)為了指示always 程序代表時(shí)鐘觸發(fā)的時(shí)序邏輯行為,always或always_ff關(guān)鍵字后跟:

@?(posedge?

例如:

always_ff?@(posedge?clk) q?<=?d;?//時(shí)序邏輯觸發(fā)器

一些時(shí)序元件具有異步輸入,例如set或reset控制。這些異步信號(hào)也會(huì)影響仿真或綜合時(shí)評(píng)估always程序的運(yùn)行時(shí)間,因此也應(yīng)該包括在靈敏度列表中。

后面章節(jié)更詳細(xì)地討論了時(shí)序邏輯的建模,包括同步和異步set、enable控制,以及正確使用通用always和專用always_ff程序塊的指南。

組合邏輯靈敏度。組合邏輯(如加法器或解碼器)的輸出反映了該邏輯塊當(dāng)前輸入值的組合。因此,每當(dāng)組合邏輯的任何輸入值改變時(shí)(即敏感度列表),就需要重新評(píng)估組合邏輯中的編程語句。為了仿真這種行為,always關(guān)鍵字后面是一個(gè)明確的敏感度列表,其中包括該邏輯塊讀取的所有信號(hào),其形式為:

??????@(

例如:

always?@(a,?b) sum?=?a?+?b;

always_comb專用always程序的一個(gè)特點(diǎn)是,它自動(dòng)推斷出一個(gè)合適的組合邏輯靈敏度列表。上述加法器代碼使用always_comb建模為:

always_comb?@(a,?b) sum?=?a?+?b;

后面章節(jié)將更詳細(xì)地討論組合邏輯建模,以及always和always_comb程序塊的正確使用指南。

latch邏輯靈敏度。鎖存是組合邏輯塊的一種形式,可以存儲(chǔ)其當(dāng)前狀態(tài),建模鎖存行為遵循與建模組合邏輯行為相同的敏感度列表規(guī)則。Always_latch關(guān)鍵字后面是一個(gè)靈敏度列表,其中包括該邏輯塊讀取的所有信號(hào),格式為:

@(

如下所示:

Always_latch專用always程序自動(dòng)推斷出正確的組合邏輯靈敏度列表。

后續(xù)章節(jié)將更詳細(xì)地討論了鎖存邏輯的建模,包括使用always和always_latch程序塊的最佳實(shí)踐編碼指南。

不可綜合的敏感度列表。從語法上講,靈敏度列表可以包含操作,例如@(a+b)或iff保護(hù)條件,posedge和negedge限定符也可以用于大于1位寬的向量,但只使用向量的最低有效位(最右邊的位),向量中其他位的更改不會(huì)觸發(fā)敏感度列表,RTL綜合編譯器通常不支持操作:iff和向量邊沿(posedge和negedge)。

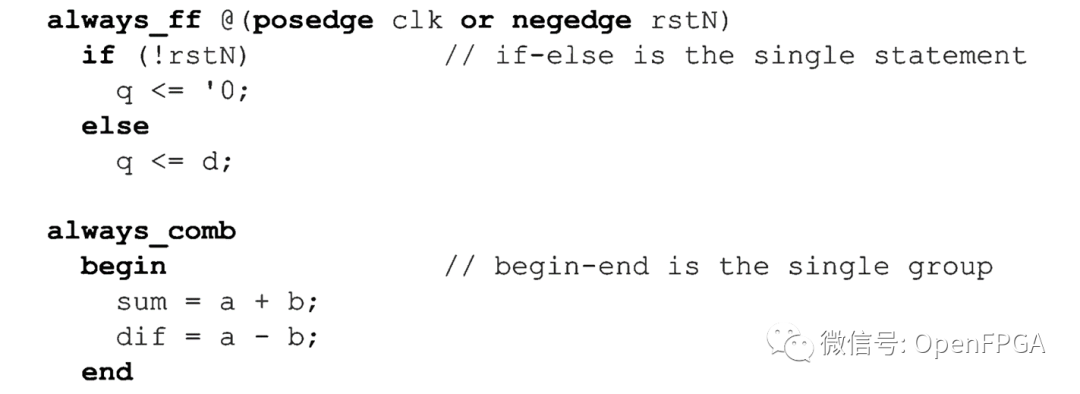

begin-end語句組

所有形式的程序塊都可以包含一條語句或一組語句。語句組包含在關(guān)鍵字begin和end之間,可以包含任意數(shù)量的語句,包括none語句。下面的代碼片段顯示了一個(gè)包含單個(gè)語句的always 程序和一個(gè)包含begin end組的always 程序。

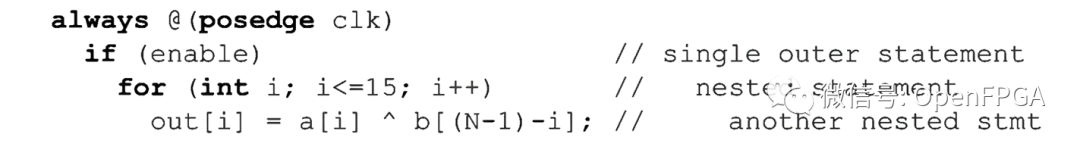

一條語句可以嵌套在另一條語句中,如:

在前面的代碼段中,外部語句是always 程序中的單個(gè)語句,因此不需要begin-end語句組。

可以使用以下語法命名begin-end語句組:

begin:

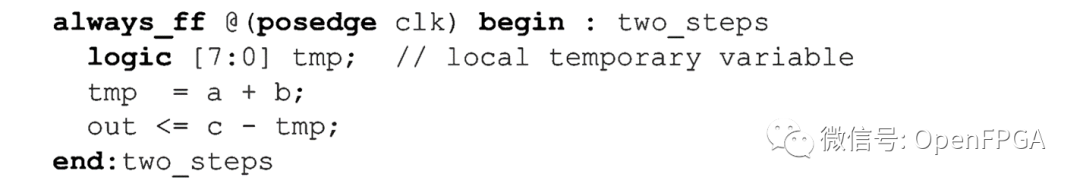

命名語句組可以包含局部變量聲明,局部變量可以在語句組內(nèi)使用,但不能在可綜合RTL模型的組外引用,(SystemVerilog的更高版本增加了在未命名的begin端組中聲明局部變量的功能,但在編寫本文時(shí),大多數(shù)綜合編譯器都不支持這種功能。)

也可以選擇命名組的匹配端。命名語句組的結(jié)尾可以幫助直觀地匹配嵌套的語句組。SystemVerilog要求用于開始和結(jié)束的名稱必須完全匹配。

局部變量的使用有助于確保在某些情況下得到適當(dāng)?shù)木C合結(jié)果。在時(shí)序always程序中計(jì)算并由另一個(gè)程序使用的臨時(shí)中間變量可能在仿真中起作用,但可能綜合出與RTL仿真行為不匹配的門級(jí)功能,在過程中聲明局部變量將防止此編碼錯(cuò)誤-無法從過程外部訪問局部變量,

下面的示例聲明了一個(gè)臨時(shí)變量,該變量位于always_ff 過程的局部。臨時(shí)變量用于計(jì)算中間結(jié)果,然后用于計(jì)算最終結(jié)果(本例中的計(jì)算特意保持簡單,以便專注于局部變量的聲明,而不是一些可能需要中間計(jì)算的復(fù)雜算法)

請注意,冒號(hào)前后允許有空白,如上面的begin后面所示。但是,end后面不能有空白,如上圖所示。使用空格有助于使復(fù)雜的代碼更易于閱讀。

在程序塊中使用變量和網(wǎng)絡(luò)

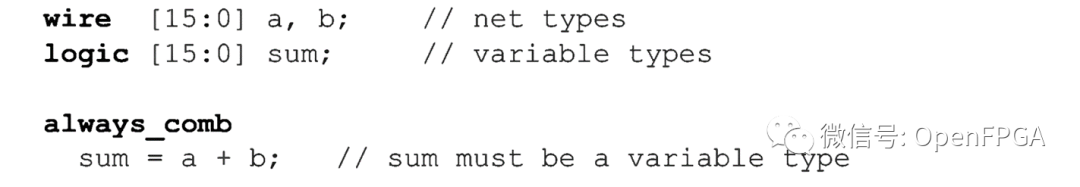

程序賦值的左側(cè)只能是變量類型,包括基于變量的用戶自定義類型。在運(yùn)算符或賦值語句更新之前,變量仍然保持其先前的值,變量的這種特性會(huì)影響仿真和綜合。

在下面的代碼段中,sum必須聲明為變量類型,因?yàn)樗挥谶^程賦值的左側(cè)。有關(guān)RTL建模中可使用的可綜合變量類型的討論,請參見之前的文章。

只有程序賦值的左側(cè)必須是變量。賦值的右側(cè)可以使用變量、網(wǎng)絡(luò)、參數(shù)或文字值。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論