有想法把最近看到關(guān)于FPGA相關(guān)的(名詞)概念做個(gè)總結(jié),解釋內(nèi)容主要來(lái)自其他博客,我只加部分個(gè)人理解,做個(gè)拾荒者,撿其重點(diǎn),作為摘錄,文末羅列參考資料。

1、異步復(fù)位、同步釋放

1.1.解釋

同步復(fù)位:需要時(shí)鐘參與,一般只有時(shí)鐘上升沿到來(lái)復(fù)位信號(hào)才有效;

異步復(fù)位:不需要時(shí)鐘參與,只要復(fù)位信號(hào)一有效就立即進(jìn)行復(fù)位操作;

1.2.優(yōu)缺點(diǎn)

同步復(fù)位:防止復(fù)位信號(hào)的毛刺引起誤復(fù)位操作,利于靜態(tài)時(shí)序分析;較異步復(fù)位更消耗邏輯資源,復(fù)位信號(hào)脈沖寬度必須大于時(shí)鐘周期,同步復(fù)位依賴于時(shí)鐘;

異步復(fù)位:無(wú)需額外的邏輯資源,復(fù)位信號(hào)不依賴于時(shí)鐘;容易受毛刺影響,如果復(fù)位釋放恰好在時(shí)鐘有效沿附近容易使寄存器輸出亞穩(wěn)態(tài);

1.3.CODE

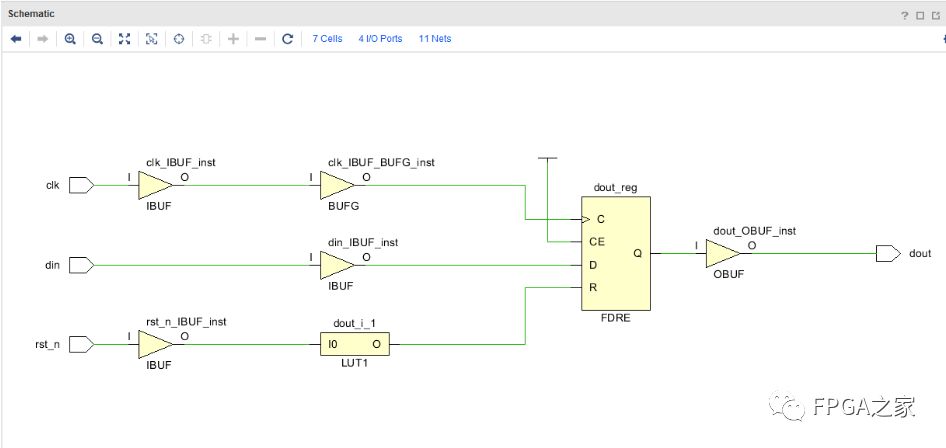

同步復(fù)位:

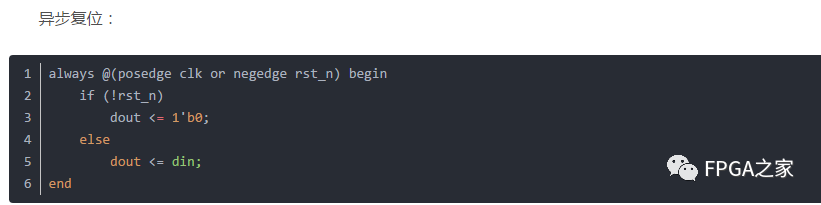

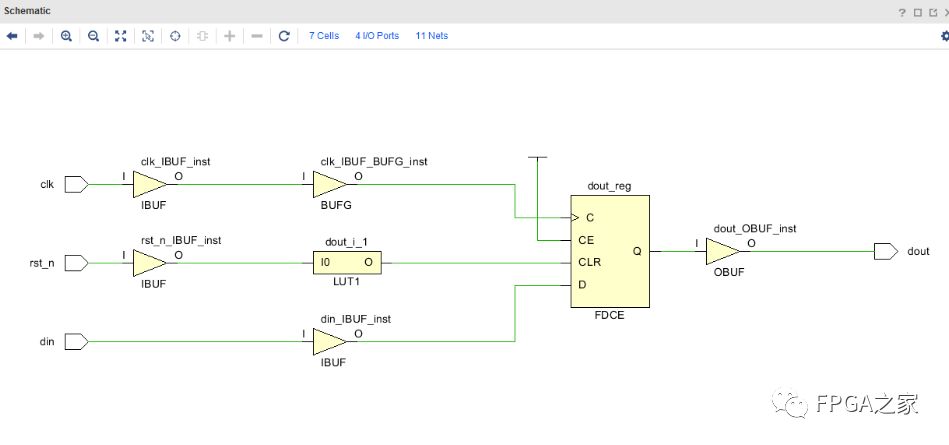

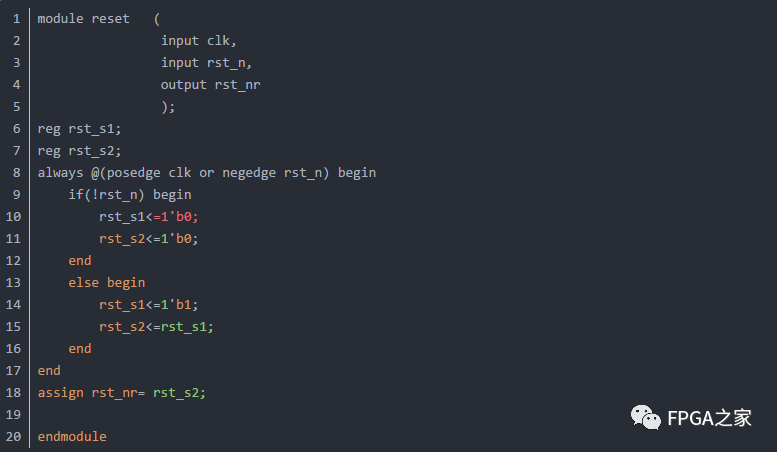

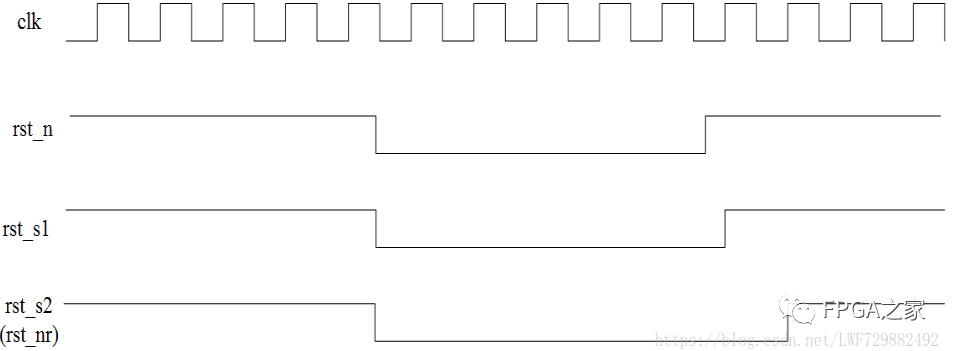

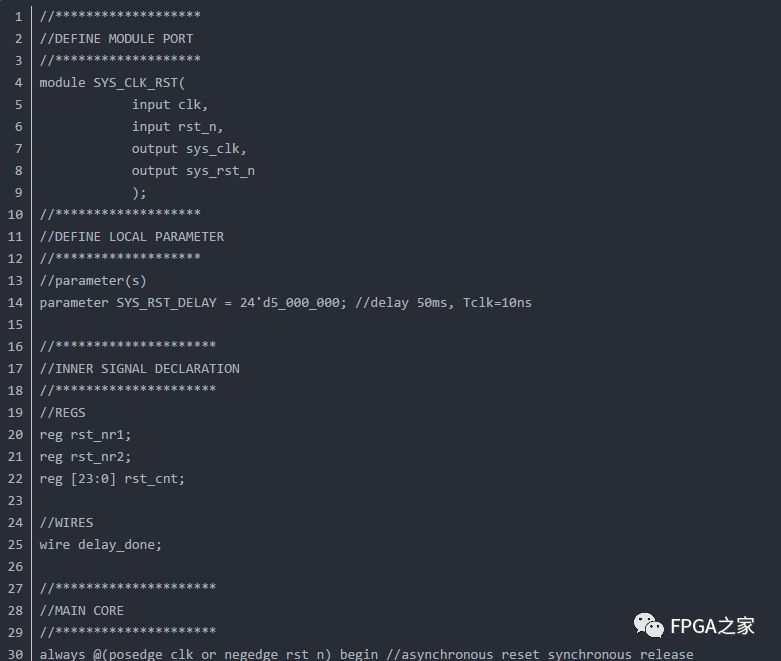

異步復(fù)位,同步釋放(Synchronized Asynchronous Reset):目的為了防止復(fù)位信號(hào)在撤除時(shí)產(chǎn)生亞穩(wěn)態(tài)。

異步復(fù)位:將復(fù)位信號(hào)rst_n接入到DFF的清零端,不存在復(fù)位信號(hào)必須要檢測(cè)到大于一個(gè)時(shí)鐘周期才能被檢測(cè)到的局限,只要rst_n則將rst_s1,rst_s2賦0。

同步釋放:當(dāng)rst_n重新拉回高電平,進(jìn)行removal,時(shí)鐘參與。

或:異步復(fù)位、同步釋放(考慮上電延遲)

2、觸發(fā)器與鎖存器

2.1.解釋

觸發(fā)器Flip-Flop:收到輸入脈沖,觸發(fā)器輸出根據(jù)賦值規(guī)則作出改變,保持此狀態(tài)知道下一個(gè)觸發(fā)。。。對(duì)時(shí)鐘邊沿敏感,其狀態(tài)只在時(shí)鐘的上升沿或者下降沿的瞬間改變;

鎖存器Latch:兩輸入,EN和DATA_IN,當(dāng)電平EN有效時(shí),鎖存器處于使能狀態(tài),輸出數(shù)據(jù)Q隨輸入數(shù)據(jù)DATA_IN變化,否則數(shù)據(jù)被鎖存;

2.2.區(qū)別

latch跟它所有的輸入信號(hào)有關(guān),當(dāng)輸入信號(hào)變化時(shí),latch就變化,沒有時(shí)鐘觸發(fā);flip_flop受時(shí)鐘控制,只有時(shí)鐘沿觸發(fā)時(shí)才采樣當(dāng)前輸入,產(chǎn)生輸出。

1)latch由電平觸發(fā),非同步控制。在使能信號(hào)有效時(shí)latch等效于通路,使能信號(hào)無(wú)效時(shí)latch保持輸出狀態(tài);flip_flop由時(shí)鐘沿觸發(fā),同步控制;

2)latch對(duì)輸入電平敏感,受布線延遲影響較大,很難保證輸出沒有毛刺產(chǎn)生;flip_flop不易產(chǎn)生毛刺;

3)latch消耗的門資源比f(wàn)lip_flop少,但是其靜態(tài)時(shí)序分析更為復(fù)雜;

2.3.CODE

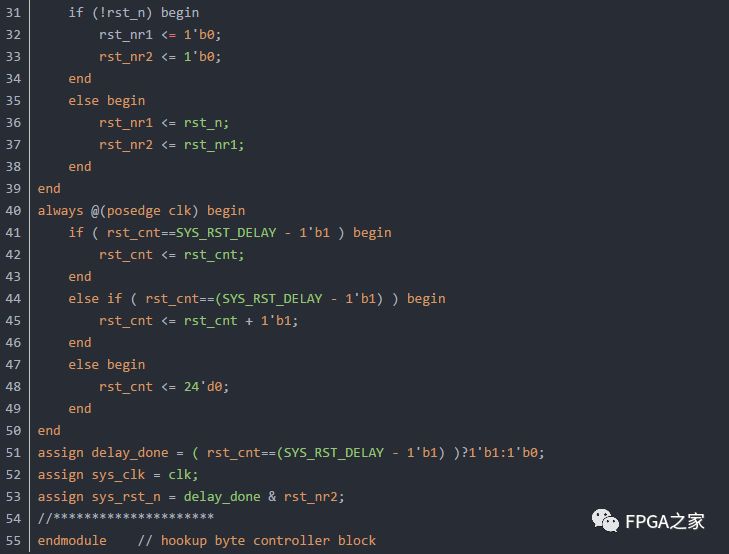

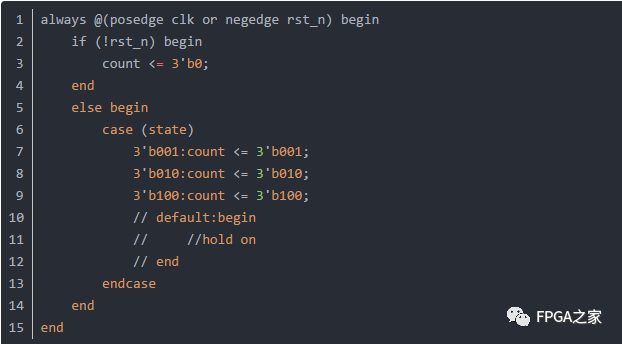

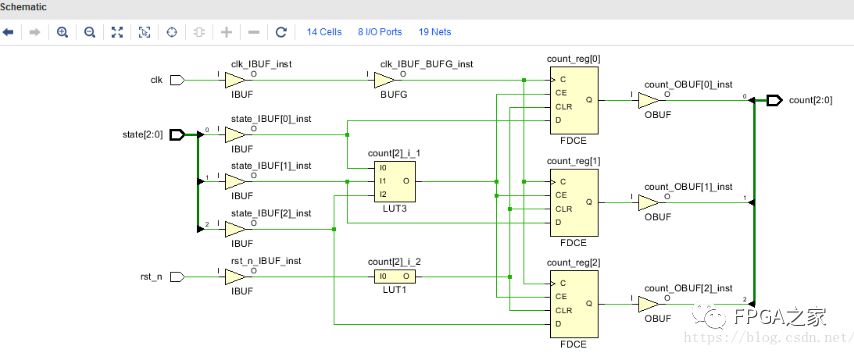

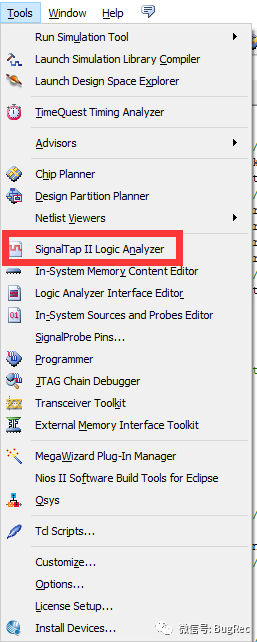

針對(duì)網(wǎng)上博客所說(shuō),容易生成鎖存器的四種情況:1)if語(yǔ)句結(jié)束無(wú)else;2)case語(yǔ)句結(jié)束無(wú)default;3)輸出變量無(wú)賦初值;4)always@ (敏感信號(hào))。我嘗試過1),2)兩種情況,遺憾的是,在Vivado17.2中綜合后查看Schematic并沒有看到有鎖存器,就下邊這段而言,case有無(wú)default,Schematic上看到的都是由FDCE(D觸發(fā)器)和LUT(查找表)等元素組成,如圖1所示。

圖1 case有無(wú)default后的Schematic

有博主是通過QUARTUS II中的Technology Map View查看門級(jí)電路,確是論證了上述四種情況,因?yàn)槲乙矝]用過QUARTUS II所以不進(jìn)一步實(shí)驗(yàn)了,不過,綜合后如果出現(xiàn)鎖存器,Vivado17.2會(huì)在“Messege”窗口警告提示有l(wèi)atch。

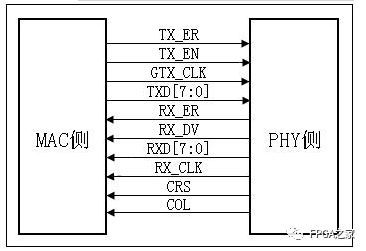

這兒所說(shuō)的以太網(wǎng)接口只是其中三種,GMII,RGMII,SGMII,也是實(shí)驗(yàn)室所用的三種。首先說(shuō)明一下MII(Media Independent Interface),不用考慮媒體材料是銅軸、電纜還是光纖,媒體處理的相關(guān)工作都有MAC芯片或者PHY來(lái)完成,MII支持10/100兆接口速率,而GMII(Gigabit MII)支持1000兆,同時(shí)往下兼容10/100兆速率。

3.1.GMII接口

GMII(Gigabit Media Independent Interface),數(shù)據(jù)位寬8bit,發(fā)送參考時(shí)鐘和接收參考時(shí)鐘均為125M,上升沿對(duì)數(shù)據(jù)采樣,125M*8bit=1000Mbps。

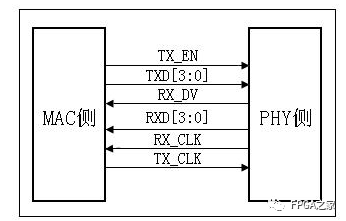

3.2.RGMII接口

RGMII(Reduced Gigabit Media Independent Interface),數(shù)據(jù)位寬4bit,發(fā)送參考時(shí)鐘和接收參考時(shí)鐘均為125M,上升沿發(fā)送GMII接口中的TXD[3:0]/RXD[3:0];在下降沿發(fā)送GMII接口中的TXD[7:4]/RXD[7:4]。這樣速率就是125M*4bit*2=1000Mbps。向下兼容,取參考時(shí)鐘為2.5M/25M,則接口速率為10/100Mbps。

拓展:DDR3也是上升沿下降沿采樣,主時(shí)鐘為400M,用戶時(shí)鐘為100M,突發(fā)長(zhǎng)度為8,數(shù)據(jù)位寬為256bit,存儲(chǔ)位寬為32bit,則MIG IP核的用戶接口和內(nèi)部存儲(chǔ)接口速率匹配:100M*256bit=400M*32bit*2

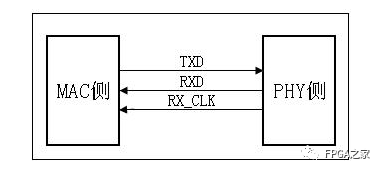

3.3.SGMII接口

SGMII(Serial Gigabit Media Independent Interface),既然是串行,那么數(shù)據(jù)位寬1bit,收發(fā)各有一對(duì)差分信號(hào)線,工作時(shí)鐘由PHY提供,頻率為625M,時(shí)鐘的上升沿和下降沿均采樣,考慮到IP核對(duì)串行數(shù)據(jù)進(jìn)行了8b/10b編碼,所以有效數(shù)據(jù)傳輸速率為625M*1bit*2*8b/10b=1000Mbps。

拓展:關(guān)于這個(gè)8/10b編碼,最早由IBM發(fā)明應(yīng)用,在pcie、hdmi及USB接口中均有體現(xiàn),8/10b編碼是高速串行總線常用的編碼方式,為了保證直流平衡(數(shù)據(jù)流中出現(xiàn)的0/1數(shù)量基本一致,連續(xù)的0/1不超過5個(gè))。。。hdmi中最小化傳輸差分信號(hào)的8/10b編碼的前8位由原始數(shù)據(jù)經(jīng)運(yùn)算獲得,第9位是“運(yùn)算方式位”,表示前邊8位是異或還是異或非等方式進(jìn)行編碼,第10位是為了保證直流平衡。

4、FPGA設(shè)計(jì)思想與技巧//2018-6-20 1640

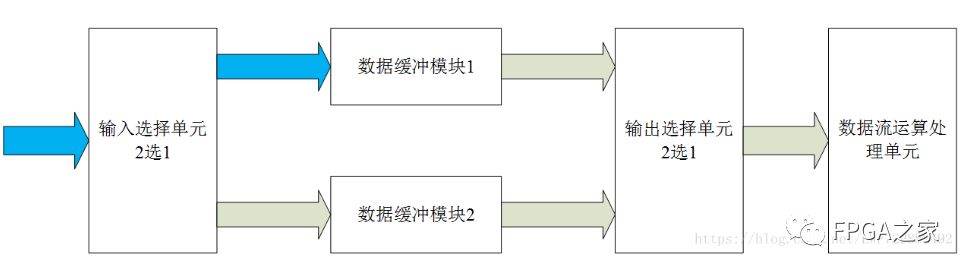

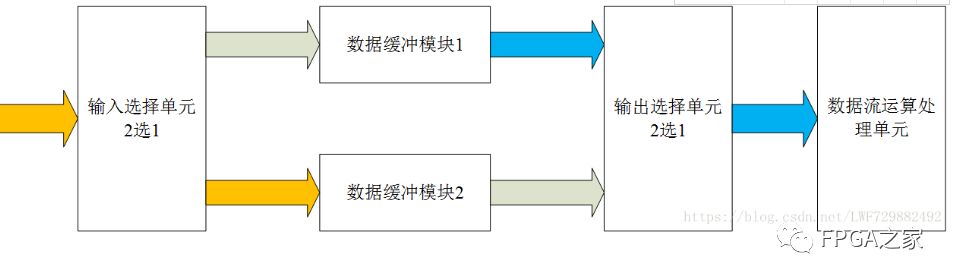

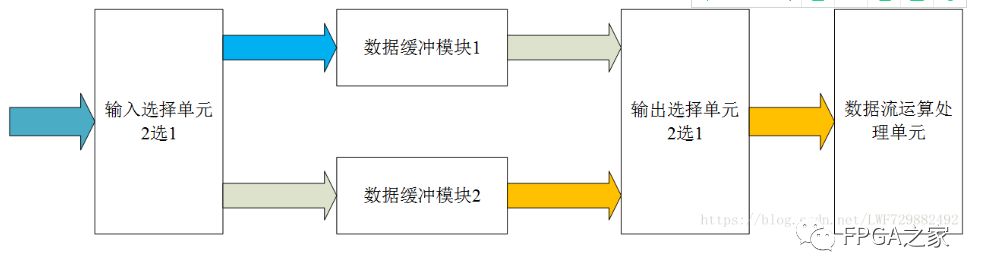

4.1.乒乓操作

在第一個(gè)緩沖周期,將輸入數(shù)據(jù)緩存到“數(shù)據(jù)緩沖模塊1”;

在第二個(gè)緩沖周期,通過“輸入選擇單元”切換,將輸入數(shù)據(jù)流緩存到“數(shù)據(jù)緩沖模塊2”中,同時(shí)將“數(shù)據(jù)緩沖模塊1”緩存的第一個(gè)周期數(shù)據(jù)通過“輸出選擇單元”的選擇,送到”數(shù)據(jù)流運(yùn)算處理模塊“進(jìn)行數(shù)據(jù)處理;

在第三個(gè)緩沖周期,再次通過“輸入選擇單元”切換,將輸入數(shù)據(jù)流緩存到“數(shù)據(jù)緩沖模塊1”中,同時(shí)將”數(shù)據(jù)緩沖模塊2“緩存的第二個(gè)周期數(shù)據(jù)通過”輸出選擇單元“的選擇,送到”數(shù)據(jù)流運(yùn)算處理模塊“進(jìn)行數(shù)據(jù)處理;

如此循環(huán)。。。

4.2.串并轉(zhuǎn)換

串并轉(zhuǎn)換的實(shí)現(xiàn)根據(jù)數(shù)據(jù)的排序和數(shù)量要求,可以選用寄存器、RAM等實(shí)現(xiàn)。乒乓操作就是通過DPRAM實(shí)現(xiàn)數(shù)據(jù)流的串并轉(zhuǎn)換,由于使用DPRAM,數(shù)據(jù)緩沖區(qū)可以設(shè)置很大,,,對(duì)于數(shù)量較小的設(shè)計(jì)采用寄存器,如:temp<={ temp, srl_in }

4.3.流水操作

一種處理流程和順序操作的設(shè)計(jì)思想,多使用寄存器以換取面積和速度

4.4.數(shù)據(jù)接口同步化

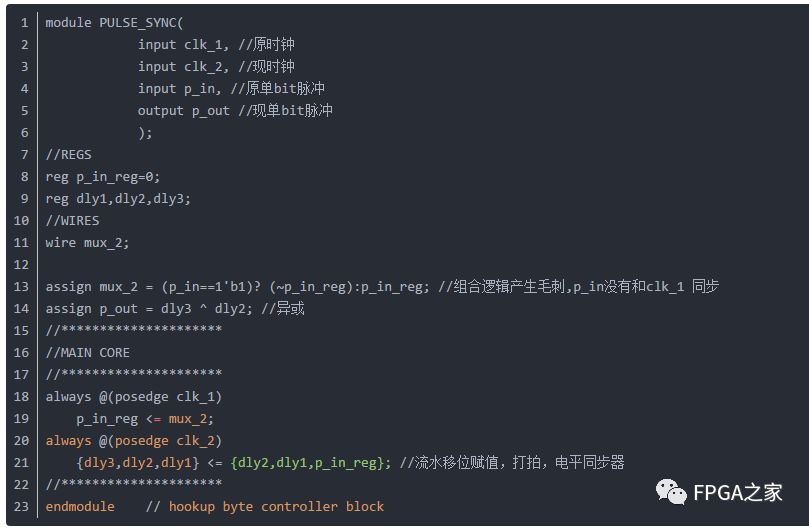

這里的數(shù)據(jù)可以是單bit數(shù)據(jù)也可以是多位寬數(shù)據(jù),多位寬數(shù)據(jù)的話例化異步FIFO即可,這里主要討論的是高頻采低頻的單bit(控制信號(hào),脈沖使能信號(hào)等)。在文檔“Crossing the abyss: Asynchronous signals in a synchronous world”中提及三種方法:1,.電平同步器(打拍,雙鎖存器法);2.邊沿同步器;3.脈沖同步器(推薦,但是工程中覺得要例化這個(gè)模塊很麻煩,還不如直接打兩拍來(lái)得快),下邊給出網(wǎng)上的脈沖同步器源代碼,實(shí)測(cè)仿真可行。//Edited by LIUWF 設(shè)計(jì)思想:原時(shí)鐘域下將原脈沖轉(zhuǎn)為電平,然后在現(xiàn)時(shí)鐘域下將輸入電平打兩拍,再異或處理得到現(xiàn)時(shí)鐘域下的脈沖//

5、接口、總線與協(xié)議//2018-6-21 1542

在口頭表達(dá)上,我總是把PCIe接口/總線/協(xié)議混為一談,沒有細(xì)致地作區(qū)分。昨晚跟室友討論到這個(gè)點(diǎn),在接口和協(xié)議部分達(dá)成了“共識(shí)”,當(dāng)然,在總線部分也有一些小分歧,下邊就這三種簡(jiǎn)練的説一下。

5.1.接口

接口理解為一類設(shè)備口。比如USB口、網(wǎng)口、PCIe口以及SATA口等

5.2.總線

總線這部分我理解是高速(差分)通道,IP核實(shí)現(xiàn)數(shù)據(jù)的串并轉(zhuǎn)換,其實(shí)PCIe,MAC,SATA等都是基于Serdes接口傳輸?shù)模瑩Q言之,底層都是Serdes串行高速信號(hào)傳輸,但是到IP層根據(jù)不同的應(yīng)用場(chǎng)景可以是PCIe,MAC或者SATA。

5.3.協(xié)議

協(xié)議和接口一樣比較好理解:傳輸數(shù)據(jù)數(shù)據(jù)的規(guī)則。比如PCIe每種TLP包有特定的包頭封裝規(guī)則;MAC的數(shù)據(jù)頭部字段是0x55d5;

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論