DC-DC將啟動Rise Vadj電源。一直以來,我的Vccint,Vccaux,Vccmgt,一些擁有DDR3和其他功能的銀行都在上電和工作。我的問題:這是正常的操作嗎?它不會傷害芯片嗎?我知道VCCO

2020-08-18 09:51:02

FPGA各管腳含義用戶I/O:不用解釋了。配置管腳:MSEL[1:0] 用于選擇配置模式,比如AS、PS等。DATA0 FPGA串行數據輸入,連接到配置器件的串行數據輸出管腳。DCLK FPGA串行

2014-12-29 11:46:33

文章目錄各種硬件CPUGPUNPUFPGA各芯片架構特點總結國產化分析華為Atlas 300寒武紀比特大陸各種硬件CPUCPU(Central Processing Unit)中央處理器,是一塊

2021-07-26 07:02:18

電壓 VCCINT 的緩升時間必須在制造商規定的范圍內。對于一些 FPGA,由于 VCCINT 會在晶體管閾值導通前停留更多時間,因此過長的緩升時間可能會導致啟動電流持續較長時間。如果電源向 FPGA

2020-10-22 11:35:35

的VCCIO必須相同,不能夠使用2種VCCIO標準;3、一個bank不需要VCCIO,也可以把VCCIO連接到外部電壓上;4、一個bank內使用多個電源管腳是為了均衡供電,避免一個管腳電流...

2021-12-28 07:06:23

告如下的錯誤(截圖的原因,只給出Error的前半部分):可以看出,差分信號需要的VCCIO是2.5V。實際上軟件并不知道在實際的系統上該BANK的VCCIO接的電源是多少,只要不定義該BANK的任一IO

2018-09-03 11:08:41

FPGA使用的電源類型有哪些? FPGA電源要求輸出電壓范圍從1.2V到5V,輸出電流范圍從數十毫安到數安培。可用三種電源:低壓差(LDO)線性穩壓器、開關式DC-DC穩壓器和開關式電源模塊。最終

2012-02-24 11:42:19

特殊供電需求)。這4類電源分別是內核電壓VCCINT、I/O電壓VCCIO、PLL模擬電壓VCCA和PLL數字電壓VCCD_PLL。這4類電源電壓中,內核電壓固定1.2V、PLL模擬電壓固定2.5V

2015-04-22 12:06:21

,Cyclone III系列器件的供電一般是分4大類,壓值有2-3檔(可能更多檔,這主要取決于不同bank的I/O電壓是否有特殊供電需求)。這4類電源分別是內核電壓VCCINT、I/O電壓VCCIO、PLL

2019-01-10 09:34:18

本人小菜鳥一個,剛開始學習FPGA,希望各位大神指點,最近看DATASHEET有點暈,求助Xilinx Spartan6—LX的電源供電怎么設計,IO電壓和核電壓這個還好理解,可是那個輔助電壓

2014-06-13 10:55:11

,可以請您介紹一下FPGA的電源要求嗎?好的!我覺得這樣更容易理解該DC/DC轉換器系列被定義為“FPGA用”的原因。說到FPGA,制造商有很多,功能以及構成也各式各樣。在這里希望大家了解的是相比之下

2018-12-03 14:40:01

,Vccbram,Vccaux,Vccaux_io,Vcco。其中,如果Vccint和Vccbram是相同的電壓,則可以采用同一電源供電,同時啟動。Vccaux,Vccaux_io和Vcco為同一電壓則亦可以采用

2023-11-03 11:08:33

以采用同一電源供電,同時啟動。Vccaux,Vccaux_io和Vcco為同一電壓則亦可以采用同一電源,同時啟動。除此,在設計FPGA的原理圖中要需要特別關注Serdes的供電(不同的廠家,甚至同一廠家

2019-07-18 14:26:01

FPGA的特殊電源有哪些要求 為確保正確上電,內核電壓VCCINT的緩升時間必須在制造商規定的范圍內。對于一些FPGA,由于VCCINT會在晶體管閾值導通前停留更多時間,因此過長的緩升時間可能會

2012-02-24 11:35:48

你好根據數據表,Virtex6需要按VCCINT-> VCCAUX-> VCCO的順序上電順序。 VCCAUX和VCCO允許同時斜坡,前提是兩者均由相同電源供電。對于斷電,排序為

2020-06-12 16:33:31

學習的時候了解到FPGA的多路供電要求一定的上電斷電順序,目前在搞Altera的Cyclone IV系列的FPGA,主要有內部邏輯供電VCCINT,PLL供電VCCD_PLL,IO口供電VCCIO等

2017-05-18 22:36:29

的電平。FPGA設置為QSPI引導,但QSPI中沒有映像。電源是:Bank 0,12,13是+ 2V533銀行是+ 1V834,35銀行是+ 1V5銀行500,5001是+ 2V5Bank 502

2020-07-14 14:25:30

我在我的自定義主板上使用Spartan 3A DSP。所有電源均來自外部電源(包括1.2V核心電源(Vccint))。我的問題是,如果意外的話,如果任何電源線損壞且Vcco或Vccint長時間沒有

2019-05-28 12:16:42

在Spartan 6上,它顯示VCCINT范圍為1.14V至1.26V。我想在1.1V下運行器件,并且需要知道這可能會對器件產生什么影響。我確定這是一個不同于過電壓的條件,這可能會傷害它。我認為它可

2019-07-22 10:45:30

連接?我想不是,但只是為了確保。我應該為J-TAG TDI和TMS引腳放置任何外部上拉電阻嗎?或者內部的就足夠了?使用3.3V(VCCIO和VCCAUX)和1.2V(VCCINT)為我的設計供電時,我

2019-06-06 13:09:53

的VCCINT和VCCO / VCCAUX電源低于a某個門檻。來自此上電復位電路的復位信號與FPGA固件中的DCM相連。通過在我們的設計中移除此上電復位電路,我們基本上將DCM模塊作為固件中的獨立模塊

2019-04-18 10:15:45

- >(SW電源) - > 1.8V - >(LDO) - > 2.5V所以1V到VCCINT&來自LDO的VCCBRAM在1.35V之后施加到VCCO_34&組

2020-07-31 08:16:06

s/PCB-decoupling-capacitors-for-Virtex-6/mp/87968#M7230后,我仍有一些關于Virtex-6電源去耦的擔憂。UG373(v1.2)提到的ONLY電容是VCCINT的330μF電容

2020-06-15 16:27:01

您好,我正在試圖弄清楚XC2V6000在上電時會消耗多少電流。 DS表示“VCCINT,VCCAUX和VCCO電源應逐漸上升,單調,不超過200μs,不低于50 ms。”這意味著,如果VCCINT

2018-09-30 11:20:54

_XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)電壓主要有VCCINT(內核電壓),VCCRAM(RAM塊電壓),VCCAUX(輔助電壓),VCCO(IO電壓)以及高速串行收發器GTX Transceiver的供電電壓。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2021-12-28 06:38:44

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-05-28 09:23:25

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到

2021-07-08 08:00:00

此篇先細致探索一下板卡的硬件資源。 如下圖所示,主要以Artix-7 50T FPGA為核心,外圍有電源管理和時鐘電路,通信、輸入輸出端口,和存儲器。電源管理: 板卡電源輸入有兩種方式1) 由DC

2016-12-12 22:12:39

作為ESD保護元件。如果電源違反了跟蹤要求并超過了保護二極管的正向偏置,那么該器件就可能被損壞。內核電壓:內核電壓軌通常設定成VCCINT,為FPGA邏輯供電。要求的電流從幾百毫安到幾十安培,具體大小

2015-05-19 16:45:58

電源軌在1.8V FPGA電源軌實際啟用之前緩慢上升至約1V,之后它會下降至0V并正常上升至2.5V。如果我刪除所有外部電路,我沒有看到這種行為(圖片也附上)。根據數據表:建議的上電順序為VCCINT

2020-07-30 09:51:29

嗨,我目前正在使用Artix-7 FPGA進行低功耗技術的實驗,我觀察到很少有Vccint引腳連接到Artix-7芯片。我想知道為什么我們需要很少的Vccint引腳用于芯片而不僅僅是1個引腳?如果1

2020-08-26 15:33:42

我有一個使用Artix-7 FPGA(不使用GPT接口)的電路板設計,其中VCCINT,VCCBRAM和MGTAVCC電壓軌連接到一個1.0V的VRM電源。電源順序正確(VCCINT

2020-04-08 10:05:14

你好根據ZYNQ-7000 TRM,板載最小/最大電源軌[VCCINT,VCCAUX& VCCBRAM]等...可以使用內部XADC電源傳感器進行監控。你能否分享一下procdure或命令來監控linux環境中的ZYNQ rails。謝謝

2020-04-13 06:44:08

本帖最后由 Stark揚 于 2018-10-11 15:31 編輯

想請教各位,fpga設計的信號發生器的輸出脈沖在示波器中顯示的波形幅值特別低,請問這個幅值是與芯片的VCCIO口的電壓有關么,VCCIO電壓3.3v。這個幅值應該是3.3v的但是特別低,不知道是什么問題?

2018-10-11 11:17:41

斯巴達6:如果所有VCCIO-s都是2.5V,那么VCCAUX仍然必須是3.3V,還是2.5V?哪些是VCCAUX的完整要求?

2019-08-09 09:36:33

將一些引腳連接到1.2V,一些引腳連接到2.5V。我可以分別將它們連接到VCCINT和VCCAUX嗎?或者我需要從VCCINT和VCCAUX隔離電源。2.我是否需要繞過引腳的電源?3. 1.2V

2020-07-13 16:02:14

13和bank 14的VCCO。所有其他電源(VCCINT,VCCAUX,VCCBRAM,......)是否關閉時,我可以保持這些VCCO開啟(1.8V)嗎?謝謝你的幫助,羅曼。

2020-08-17 09:14:32

你好在vivado Select Device窗口中,有xc7a15ticsg***。它的速度等級是-1L。我想決定Vccint和Vccbram值,我在DS181文件中找到它們(第2頁)但是沒有1L

2020-08-10 09:49:01

,推薦的上電順序依次為Vccint,Vccbram,Vccaux,Vccaux_io,Vcco。其中,如果Vccint和Vccbram是相同的電壓,則可以采用同一電源供電,同時啟動。Vccaux

2020-12-23 17:44:23

怎樣才能產生“空白”比特流?我正在嘗試在自定義Kintex-7設計上測量VCCINT的靜態電流,它與DS182中列出的典型值有很大不同,所以我想確保正確配置(或不配置)FPGA。

2020-07-16 09:37:15

/s3ask_power_testing.pdf我嘗試使用相同的方法,但在斯巴達3E套件問題是如何在斯巴達3E中測量VCCint和VCCaux currnet ???當前的jummber在哪里下圖來自該模塊

2019-07-12 08:16:01

我們想建議如何對電源連接到VCCO,VCCINT和VCCAUX的PCB上安裝的virtex 5進行簡單測試。 ISE 14.1用于分配輸入和輸出引腳:ISE 14.1中的VHDLENTITY

2019-11-07 06:16:18

我正在使用SAKURA_G板開展項目。我想知道是否可以將VCCINT分成不同的組來為FPGA的不同部分提供電壓?或者是否可以讓SAKURA_G板的Spartan 6 FPGA在多個電源電壓下工作?非常感謝你!

2019-08-12 08:52:03

如何控制FPGA各電源的上電順序呢?請教一下大神

2023-03-27 13:48:32

、VADC_AVCCAUX、VDAC_AVCC、VDAC_AVCCAUX、VDAC_AVTT、VCCINT_AMS、VCCSDFEC等;二、如何測試FPGA的供電電源硬件工程師通常會在硬件設計初期對各路電源的功耗做

2022-09-27 08:00:00

我的第一個計劃是禁用VCCINT輸入并使用外部源連接。可能嗎?如果沒有,另一種方法是使用分流器,這需要識別兩個引腳。我可以找到穩壓器輸出引腳,但我找不到Virtex5芯片的輸入。我該如何識別該針?

2020-06-08 06:51:35

我不能使用由軟件GUI編程的電壓定序器。可以使用LM3881(根據Xilinx電源參考設計),如下所示,1. VCCINT& VCCBRAM&由LM3881啟用的VMGTAVCC(1V

2020-07-17 13:31:26

= 3.3V真的可以在VCCINT或VCCAUX之前多達5-10 ms嗎?這些電源的上電復位閾值電壓是多少? (重新:在配置進入步驟2:清除配置存儲器之前,這些電源必須達到這些電平)。我假設

2020-07-24 13:45:03

CLB和IOB的輸入和輸出至合適的網絡.施加于CLB(或核心)的電壓被稱為VCCINT.VCCO為IOB的供電電壓.一些FPGA有被稱為VCCAUX的另外一個電壓輸入. VCCINT的典型電壓和電路

2012-04-28 15:05:10

介意嗎?據我所知,推薦的電源序列是VCCINT- > VCCAUX- > VCCIO。如果VCCIO在0V內保持很長時間,那會有問題嗎?如果僅使用其他存儲體,FPGA配置是否會完成并且

2019-06-10 08:36:46

大家好,我讀到,按順序啟動CPLD和FPGA是一種很好的做法。首先是VccInt,然后是VCCIO和VCCAUX,我的問題是關于這個測序所需的延遲?是20-80我們夠嗎?關于功率的增加,我讀到它

2019-03-08 07:44:13

當沒有電源給該組時,我無法找出IO引腳的狀態。 Spartan 6 SelectIO用戶指南告訴我以下內容VCCINT(1.2V),VCCAUX和VCCO電源可以按任何順序應用。在FPGA啟動配置

2019-06-28 10:36:33

我想在任何FPGA設計完成之前為VCCINT / VCCO / VCCAUX構建一個穩壓器。是否有一種智能方法可以準確估算FPGA的功耗?以上來自于谷歌翻譯以下為原文I'm trying

2019-05-21 06:58:03

`箭頭指的是什么芯片,各引腳定義是什么`

2020-03-07 14:36:59

那些沒有用過引腳的銀行的VCCIO怎么樣?問候達維德

2020-07-25 11:17:34

你好,任何人:我現在用兩塊Kintex超大規模FPGA開發單板。我應該如何為兩個FPGA供電?1)單一解決方案,一個DCDC穩壓器供電兩個FPGA的相同電源軌(如VCCINT)。2)單獨解決方案

2019-04-03 15:26:53

,可用于要求更高精度、更靈活時序控制的應用。 圖1 所示為一種要求多個供電軌的應用。這些供電軌為內核電源(VCCINT)、I/O 電源(VCCO)、輔助電源(VCCAUX)和系統存儲器電源。 圖

2019-07-03 08:15:19

VCCO設置為1.8V,表1-5說明我們可以通過輸入和輸出獲得LVCMOS1V8操作。但是我在1.8V LVDS輸入上看不到任何東西(只有2.5V和3.3V變體)。我的問題是:VCCAUX是否有任何限制

2019-07-19 13:42:12

嗨,我在新設計中使用XC7A100T設備。在那,我將按順序使用以下電源。可以繼續下去嗎?VCCINT / VCCBRAM(1V0) - > MGTAVCC(1V0) - > VCCAUX

2020-07-30 16:35:53

如果我在所有2.5V電源(所有VCCIO-s,VCCAUX)下運行SPARTAN 6,那么DS_FT2232D USB控制器的JTAG接口是否有效? JTAG使用'A'端口的四條線。 “A”端口

2019-08-02 08:26:56

大家好,當我測試virtex6 FPGA時,我遇到了一些奇怪的事情。我之前從未為FPGA供電,這是第一次為FPGA供電FPGA的電源電壓如下:VCCINT:1.0VVCCO:2.5VVCCAUX

2020-06-17 13:50:43

你好,教授們:我有兩個相同的FPGA,它們是240t我已經知道測量FPGA的阻抗是一件危險的事情,但我把它們放在同一塊電路板上。我測量了每塊板的阻抗,發現數據不同。我測量的數據如下:VCCINT

2020-06-17 11:25:59

VCCO組,VCCINT和VCCAUX提供470nF陶瓷電容和10uF陶瓷電容。當我將帽(特別是1nF / 47nF)直接放在頂層(FPGA所在的位置)的電源引腳上時,我阻止了對I / O引腳的訪問。但是

2019-06-20 11:54:46

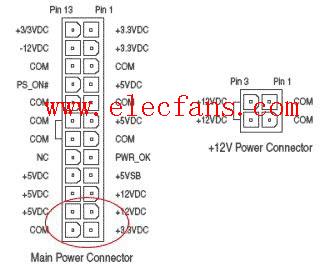

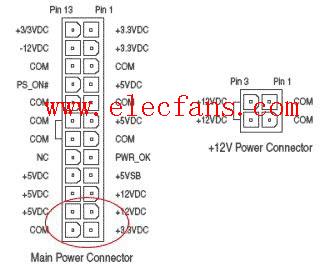

atx電源引腳定義 atx電源針腳定義 atx電源接口定義

2008-01-24 16:34:04 15564

15564

Spartan3 的內核使用1.2v,此外還需要一個2.5v 的Vccaux 輔助電源,這意味著如果用戶使用3.3VTTL,為了使Spartan3 正常工作,必須同時使用3 種電源:1.2v(Vccint), 2.5v(Vccaux), 3.3v(Vcco)

2011-05-16 16:49:29 0

0 SelectIO Resources》后,得到了以下信息:Spartan-6的供電來源于3個引腳:VCCINT、VCCO、VCCAUX。 VCCINT is the main power supply for the internal FPGA logic. VCCINT also powers s

2017-02-08 10:36:06 892

892

本文介紹了Spartan-6 FPGA中電源管理的各種硬件方法,主要介紹了暫停模式。其他電源管理主題包括低功耗斯巴達-6 LX設備(-1L)和所有斯巴達-6設備中可用的可編程VCCAUX級別。此外,電源軌上還提供了更多詳細信息,包括熱插拔和休眠(關機)選項。

2019-02-14 17:33:49 12

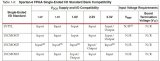

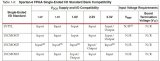

12 Xilinx Virtex UltraScale+? FPGA有-3、-2、-1個速度等級,其中-3e設備具有最高的性能。-2le設備可以在0.85V或0.72V的VCCINT電壓下工作,并提供較低

2019-02-20 15:58:16 11

11 Xilinx Kintex UltraScale?FPGA有-3、-2、-1和-1L的速度等級,其中-3的性能最高。-1L設備可以在0.95V和0.90V兩個VCCINT電壓中的任何一個下工

2019-02-21 16:48:53 6

6 Kintex-7 FPGA有-3、-2、-1、-1L和-2L速度等級,其中-3的性能最高。2L設備的最大靜態功率較低,可以在較低的核心電壓下運行,動態功率低于-2設備。-2L工業(I)溫度設備只能

2019-02-25 16:13:13 28

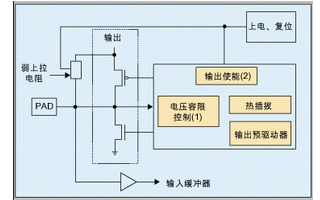

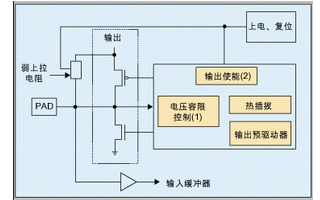

28 PLD熱插拔的基本原理是在加電(VCCINT或任何VCCIO電源)或關電過程中關斷輸出緩沖。當VCCINT或VCCIO低于閾值電壓時,熱插拔電路都會產生一個內部的HOTSCKT信號,HOTSCKT信號將關斷輸出緩沖,以便確保沒有直流電流通過管腳(不包括通過弱上拉電阻的漏電流)(見圖1)。

2020-09-02 12:06:36 1046

1046

引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到:

2021-05-01 09:47:00 10367

10367

的VCCIO必須相同,不能夠使用2種VCCIO標準;3、一個bank不需要VCCIO,也可以把VCCIO連接到外部電壓上;4、一個bank內使用多個電源管腳是為了均衡供電,避免一個管腳電流...

2022-01-06 11:18:18 2

2 _XCKU060_2FFVA1517E、FPGA_XC7A200T_2FFG1156C)電壓主要有VCCINT(內核電壓),VCCRAM(RAM塊電壓),VCCAUX(輔助電壓),VCCO(IO電壓)以及高速串行收發器GTX Transceiver的供電電壓。一般,VCCINT=VCCBRAM=1.0V,VCCO=VCCAUX=VCCAUX_IO=1.8V.高速

2022-01-06 11:20:19 11

11 -已經請您介紹了FPGA的電源要求,接下來請您介紹一下將該DC/DC轉換器系列定義為“FPGA用”的原因。首先,該系列中有些什么樣的DC/DC轉換器IC呢?目前有8種機型,是覆蓋FPGA電源的電壓與電流的產品陣容。

2023-02-17 09:25:10 721

721

電子發燒友App

電子發燒友App

評論