大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

半導體存儲器是一種能存儲大量二值信息的半導體器件。在電子計算機以及其他一些數字系統的工作過程中,都需要對大量的數據進行存儲。因此,存儲器也就成為了數字系統不可缺少的組成部分。

由于計算機處理的數據量越來越大,運算速度越來越快,這就要求存儲器具有更大的存儲容量和更快的存取速度。通常把存儲量和存取速度作為衡量存儲器性能的重要指標。因為半導體存儲器的存儲單元數目及其龐大而器件的引腳數目有限,所以在電路結構上就不可能像寄存器那樣把每個存儲單元的輸入和輸出直接引出。為了解決這個矛盾,在存儲器中給每個存儲單元編了一個地址,只有被輸入地址代碼指定的那些存儲單元才能與公共的輸入/輸出引腳接通,進行數據的讀出或寫入。

半導體存儲器的種類很多,首先從存、取功能上可以分為只讀存儲器(read only memory 簡稱ROM)和隨機存儲器(random access memory 簡稱RAM)兩大類。

ROM:只讀存儲器(Read-Only Memory)是一種只能讀取資料的存儲器。在制造過程中,將資料以一特制光罩(mask)燒錄于線路中,其資料內容在寫入后就不能更改,所以有時又稱為“光罩式只讀內存”(mask ROM)。此內存的制造成本較低,常用于電腦中的開機啟動如啟動光盤,在系統裝好的電腦上時,計算機將C盤目錄下的操作系統文件讀取至內存,然后通過cpu調用各種配件進行工作這時系統存放存儲器為RAM。

PROM:可編程只讀存儲器(Programmable ROM,PROM)之內部有行列式的熔絲,是需要利用電流將其燒斷,寫入所需的資料,但僅能寫錄一次。PROM在出廠時,存儲的內容全為1,用戶可以根據需要將其中的某些單元寫入數據0。部分的PROM在出廠時數據全為0,則用 戶可以將其中的部分單元寫入1, 以實現對其“編程”的目的。PROM的典型產品是“雙極性熔絲結構”,如果我們想改寫某些單元,則可以給這些單元通以足夠大的電流,并維持一定的時間,原 先的熔絲即可熔斷,這樣就達到了改寫某些位的效果。另外一類經典的PROM為使用“肖特基二極管”的PROM,出廠時,其中的二極管處于反向截止狀態,還 是用大電流的方法將反相電壓加在“肖特基二極管”,造成其永久性擊穿即可。

EPROM:可抹除可編程只讀存儲器(Erasable Programmable Read Only Memory,EPROM)可利用高電壓將資料編程寫入,抹除時將線路曝光于紫外線下,則資料可被清空,并且可重復使用。通常在封裝外殼上會預留一個石英透明窗以方便曝光。

OTPROM :一次編程只讀存儲器(One time Programmable Read Only Memory,OTPROM)之寫入原理同EPROM,但是為了節省成本,編程寫入之后就不再抹除,因此不設置透明窗。

EEPROM :電子式可抹除可編程只讀存儲器(Electrically Erasable Programmable Read Only Memory,EEPROM)之運作原理類似EPROM,但是抹除的方式是使用高電場來完成,因此不需要透明窗。

FLASH :快閃存儲器(Flash memory)的每一個記憶胞都具有一個“控制閘”與“浮動閘”,利用高電場改變浮動閘的臨限電壓即可進行編程動作。

隨機存取存儲器(英語:Random Access Memory,縮寫:RAM),也叫主存,是與CPU直接交換數據的內部存儲器。它可以隨時讀寫(刷新時除外),而且速度很快,通常作為操作系統或其他正在運行中的程序的臨時數據存儲介質。

RAM工作時可以隨時從任何一個指定的地址寫入(存入)或讀出(取出)信息。它與ROM的最大區別是數據的易失性,即一旦斷電所存儲的數據將隨之丟失。RAM在計算機和數字系統中用來暫時存儲程序、數據和中間結果。

SRAM :靜態隨機存儲器(SRAM)是在靜態觸發器的基礎上附加門控管而構成的。因此,它是靠觸發器的自保功能存儲數據的。SRAM存放的信息在不停電的情況下能長時間保留,狀態穩定,不需外加刷新電路,從而簡化了外部電路設計。但由于SRAM的基本存儲電路中所含晶體管較多,故集成度較低,且功耗較大。

DRAM :動態隨機存儲器(DRAM)利用電容存儲電荷的原理保存信息,電路簡單,集成度高。由于任何電容都存在漏電,因此,當電容存儲有電荷時,過一段時間由于電容放電會導致電荷流失,使保存信息丟失。解決的辦法是每隔一定時間須對DRAM進行刷新,使原處于邏輯電平“l”的電容上所泄放的電荷又得到補充,原處于電平“0”的電容仍保持“0”,這個過程叫DRAM的刷新。

上述簡單介紹了各類存儲器,內部結構和驅動原理不在介紹,有興趣的讀者可以自己查閱資料。

集成電路(integrated circuit)是一種微型電子器件或部件。采用一定的工藝,把一個電路中所需的晶體管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導體晶片或介質基片上,然后封裝在一個管殼內,成為具有所需電路功能的微型結構;其中所有元件在結構上已組成一個整體,使電子元件向著微小型化、低功耗、智能化和高可靠性方面邁進了一大步。它在電路中用字母“IC”表示。集成電路發明者為杰克·基爾比(基于鍺(Ge)的集成電路)和羅伯特·諾伊思(基于硅(Si)的集成電路)。當今半導體工業大多數應用的是基于硅的集成電路。

集成電路是20世紀50年代后期一60年代發展起來的一種新型半導體器件。它是經過氧化、光刻、擴散、外延、蒸鋁等半導體制造工藝,把構成具有一定功能的電路所需的半導體、電阻、電容等元件及它們之間的連接導線全部集成在一小塊硅片上,然后焊接封裝在一個管殼內的電子器件。其封裝外殼有圓殼式、扁平式或雙列直插式等多種形式。集成電路技術包括芯片制造技術與設計技術,主要體現在加工設備,加工工藝,封裝測試,批量生產及設計創新的能力上。

ASIC即專用集成電路,是指應特定用戶要求和特定電子系統的需要而設計、制造的集成電路。

在設計一個復雜的數字系統后,在用量不大的情況下,設計和制造這樣的專用集成電路不僅成本很高,而且設計、制造的周期很長。可編程邏輯器件(programmable logic device 簡稱PLD)的研制成功為解決這個問題提供了理想途徑。

PLD是做為一種通用集成電路產生的,他的邏輯功能按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。這樣就可以由設計人員自行編程而把一個數字系統“集成”在一片PLD上,而不必去請芯片制造廠商設計和制作專用的集成電路芯片了。

基于SRAM(靜態隨機存儲器)的可重配置PLD(可編程邏輯器件)的出現,為系統設計者動態改變運行電路中PLD的邏輯功能創造了條件。PLD使用SRAM單元來保存配置數據。這些配置數據決定了PLD內部的互連關系和邏輯功能,改變這些數據,也就改變了器件的邏輯功能。

下面我們介紹兩種常用的PLD器件:CPLD和FPGA;

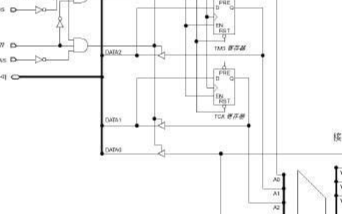

CPLD:復雜可編程邏輯器件,CPLD主要由邏輯塊、可編程互連通道和I/O塊三部分構成。CPLD中的邏輯塊類似于一個小規模PLD,通常一個邏輯塊包含4~20個宏單元,每個宏單元一般由乘積項陣列、乘積項分配和可編程寄存器構成。每個宏單元有多種配置方式,各宏單元也可級聯使用, 因此可實現較復雜組合邏輯和時序邏輯功能。對集成度較高的CPLD,通常還提供了帶片內RAM/ROM的嵌入陣列塊。可編程互連通道主要提供邏輯塊、宏單元、輸入/輸出引腳間的互連網絡。輸入/輸出塊(I/O塊)提供內部邏輯到器件I/O引腳之間的接口。

FPGA :FPGA(Field Programmable Gate Array)是在PAL、GAL等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA 器件屬于專用集成電路中的一種半定制電路,是可編程的邏輯列陣,能夠有效的解決原有的器件門電路數較少的問題。FPGA 的基本結構包括可編程輸入輸出單元,可配置邏輯塊,數字時鐘管理模塊,嵌入式塊RAM,布線資源,內嵌專用硬核,底層內嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數字電路設計領域得到了廣泛的應用。

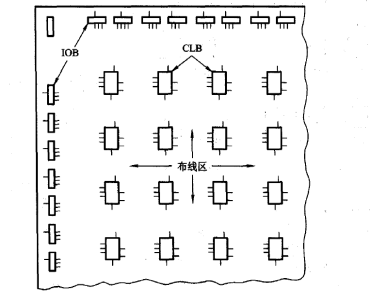

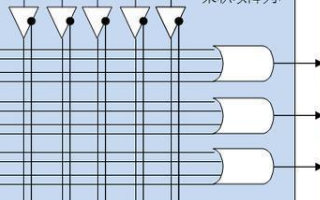

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸入輸出模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。現場可編程門陣列(FPGA)是可編程器件,與傳統邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的結構。FPGA利用小型查找表(16×1RAM)來實現組合邏輯,每個查找表連接到一個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O,由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程。

圖1 :FPGA的基本結構圖

FPGA在安防,工業等領域有著比較廣泛的應用,比如安防領域的視頻編碼解碼等協議在前端數據采集和邏輯控制的過程中可以利用FPGA處理。工業領域主要采用規模較小的FPGA,滿足靈活性的需求。另外,由于 FPGA具有比較高的可靠性,因此在軍工以及航天領域也有比較廣泛的應用。未來,隨著技術的不斷完善,相關工藝將會完成升級改造,在諸多新型行業比如大數據等,FPGA將會有更為廣泛的應用前景。伴隨5G網絡的建設,會大量應用FPGA,人工智能等新型的領域也會更多的用到FPGA。

目前用CPLD(復雜可編程邏輯器件)和 FPGA(現場可編程邏輯陣列)來進行ASIC設計是最為流行的方式之一,它們的共性是都具有用戶現場可編程特性,都支持邊界掃描技術,但兩者在集成度、速度以及編程方式上具有各自的特點。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論