一、DDS相關

1.??DDS調幅,想到了兩個方案:①改變DAC的參考電壓②改變DAC的電流,哪個好些?

答:A.能用數字電路直接調制解決的,就不用到模擬域去做了。 B.只要DAC速率夠高,可以數字生成任意波形發出去。有很多任意波形發生器的設計,可以實現調幅、調頻或調相。

C.對于AM,是要求載波幅度大于基帶的,過大的基帶信號會發生過調幅。所以不能對任意幅度信號進行AM調制。

D.對于調幅,需要考慮調制指數。設基帶最大幅度為1,基帶乘以調制指數,然后加加上1,之后再乘以幅值為1的載波,就是AM了。

E.對于調幅精度,考慮幅度的定點化,在高精度的ADC下,可以實現略有精度損失的信號調幅。

二、國產FPGA相關

1請教大家一個問題,外面買安路的FPGA開發版的商家有哪些?

答:最好聯系原廠。

2.誰知道復旦微的開發板哪里有賣?問過原廠,他們說都沒有板子了(型號JFMK50T4)。

答:一般只有原廠有,實在沒有,就自己畫,若能找到一個demo板驗證,可以降低風險。

3. 國產器件有zynq這種的嗎?

答:有,但是ARM核還是有差異。例如:復旦微的7045。管腳有差異,Vivado里需要打補丁,用GT,MIG這些的時候不同組合的步驟還有區別。

4.??國產并行flash目前大家主要用過哪些家的?最后可pin2pin鎂光的。

答:暫無回答,讀者中有了解的,可以在評論區留言。

1.??在設計中用了個localparam,定義某個參數,想在tb中修改這個localparam的值,除了就是例化的時候引入進去,還有啥辦法可以修改這個值?force這個語句只能對信號起作用。

答:A.localparam是局部常量,沒法外部修改。可以做成宏定義,或者將該參數做成輸入端口信號。

B.如果是vcs工具的話,可以通過-pvalue+parameter_hierarchical_value=value,可以修改某個指定參數到特定的值。具體用法,可參考《Synopsys VCSUser Guide》。

四、FPGA邏輯運算和時序相關

1.?實現多信號輸入有符號數據加法,調用IP方便還是自己編程方便?

答:若是有符號數,聲明signed類型直接+就行,同時注意是否存在進位,必要時進行位寬擴展。

2.?現在fpga做摳圖都用什么算法?

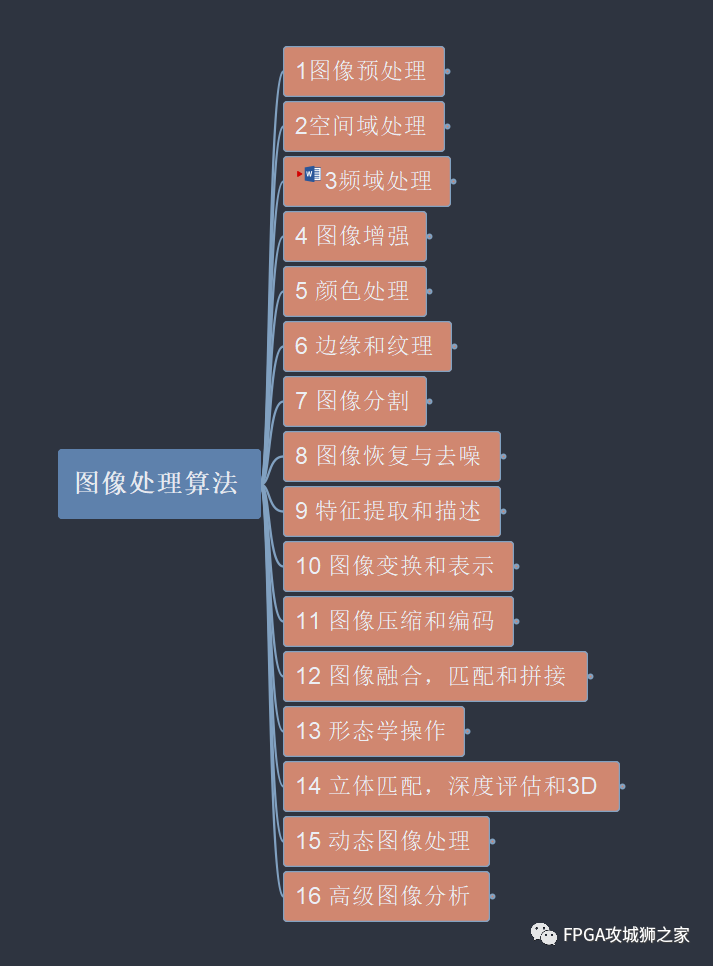

答:對于摳圖,比較簡單的方法是圖像分割,這是很老的方法,但這其實算不上真正意義的摳圖,因為他的主要目的是用于圖像之間塊與塊的分割。典型的就是grabcut算法,opencv上面有相應的優化好的算法。還有一種就是對于前后景的分割,叫做Alpha Matting,這是摳圖的主要實現方法,好的算法對頭發絲也能處理得很好。(摘自網絡SCDN博客) FPGA基本上能實現所有應用算法,關鍵要分析出算法的處理過程,從架構和資源消耗等角度考慮怎么去進行邏輯實現。

3.有沒有可以推薦的講解FPGA基礎知識的書和視頻啊,像Verilog語言會對應什么樣子的電路結構這種的?遇到過大的slack會導致問題,但是查找原因根本不會往這方面去想。

答:FPGA底層邏輯是LUT、CLB單元、BRAM等,門級或寄存器級就是時序分析的基礎。時序違例問題,可以去看一下靜態時序分析的資料,例如《Static Timing Analysis for Nanometer Designs A Practical Approach》、《Constraining Designs for Synthesis andTiming Analysis》,對于Vivado開發環境,可以參考Xilinx的UG903、UG602。

4.?請教一下大家IP及IO口的輸出電流強度應該怎么選擇?現在用的都是默認值。

答:IO驅動電流默認是12,最大可以選24。一般默認就可以,若有時序問題,可以微調。另外,溫度會影響晶體管的靜態工作點,PN結特性對溫度敏感。

5.?VIVADO資源統計里沒有LUT和FF 意思就是完全沒有用到嗎?

答:一般情況下,有邏輯設計,LUT會有消耗的,如果綜合后查看資源報告,沒有消耗LUT資源,可能是該模塊信號由于沒有連接到端口引腳,被優化掉了。可以加上“keep ture”屬性或者將信號接到vio、ILA上,再查看資源消耗。

五、衛星互聯網相關

1.?中國某網是新成立的大型央企,馬斯克的Starlink成為商業衛星最為成功的代表,國內的衛星商業化道路還很漫長。

2.?搶占近地軌道和頻率,是比較關心的兩個領域。

3.??NTN與DVB哪個有前途?

答:NTN是最近幾年基于5G技術標準提出來的,3GPP協議38.811比較全面地介紹了NTN的應用前景,也是目前除了DVB外最為熱門的衛星通信應用技術。國內和國際上眾多手機廠商和設備商,都在積極研發支持NTN的終端和基站等。就目前看來,NTN的商業化過程還比較長,相關的技術標準和協議,都屬于探索和逐步落地階段。

DVB協議經過十幾年的發展,技術路線比較成熟,商業化,應用廣泛。2020年,DVB-RCS2等新一代DVB協議發布,支持高帶寬衛星通信。兩個標準,互相借鑒,考慮專利和技術壁壘,不同的企業可能采用不同的技術路線。

六、接口相關

1.?SPI接口怎么通過修改邏輯代碼來提高SPI讀寫的速率呢?

答:一般是提高時鐘頻率,做好接口約束,把FPGA端的IO的驅動能力設高一些。

2.?大家對于GT口傳輸AXIS,轉成AXI有什么好想法?

答:DMA接口。

七、GTX時鐘相關

1.?有個高精度的10MHz時鐘,怎么提供給FPGA的GTX使用呢,GTX的時鐘不支持這么低的時鐘輸入,如果經過時鐘芯片精度就損失了。要用這個高精度時鐘進行碼環相位測量。

答:一般可以用MMCM進行時鐘倍頻,GTX的參考時鐘一般在手冊中也會有要求。特殊情況,可能需要特殊設計。

八、DDR相關

1.?DDR原理圖設計里 DQ不按順序有什么影響嗎?

答:一般沒影響,只要綜合約束過,就算開始按順序,PCB走線不過也要調線序。不放心的話可以預先弄個MIG約束下引腳,看能不能校驗過。

2.請問ADC DDR輸出進ddio,而input-pad到ddio-in有10ns的延遲,造成setup時間違例5.6ns,這種怎么解決?程序是只寫了關于ADC芯片采集接口,然后約束了ADC的數據輸入接口和pll,還需要其他的嗎,還是ADC數據輸入接口約束錯了?

答:應該是沒約束對,看樣子應該是lvds接口的,input-pad到ddio-in的延遲不單單是數據線,時鐘線也一樣,這個setup時間應該是由input delay決定的。

九、vivado綜合問題

1.?Vivado綜合著就不動了,半個小時過去了,之前都是綜合10幾分鐘,布局布線3個多小時?

答:綜合一般不會很長時間,如果出現綜合過程中一直卡著,大概率是代碼設計有缺陷,或者XDC約束有不合理的地方。此外,可以看一下log文件,一般來說,會有打印,執行到哪一步了。通常情況下,在布局布線階段更容易出現一直卡住的情況,查看log打印,會有提示,例如因為時序太差,布線走不通,導致擁塞。或者停止綜合,復位一下綜合過程,關掉vivado,重來一次。

十、電機控制

1.?想請教一下,電機的速度環,大概多長時間對電機控制一次?

答:一般10KHz以下。

2.??24xx的DSP能夠達到這種控制速度嗎?

答:DSP普遍帶計數器的,能脈沖計數,也能輸出帶死區的PWM波,用中斷計數基本做不了電機控制。記得今年TI出了一個超強的片子,把MOS和FOC全部集成到一個片子上,6塊錢的片子,不用寫代碼,不用驅動板,就能實現電機調速,實在強。

十一、時序約束相關

1.?請問如果時序約束不滿足上板一定會有問題嗎?

答:看一下最差路徑是屬于哪個時鐘域,最差裕量不超過時鐘頻率的15%,應該能跑。有個評估能跑最高時鐘的公式,好像是1/(T-WNS),T是目標時鐘周期,WNS是最差負時序裕量,可以故意約束緊一點,跑出時序報告,看時序裕量。

余量為正不一定跑出來就對,為負也不見得跑出來就不對,先有正確的約束才能有正確的時序分析。

編輯:黃飛

電子發燒友App

電子發燒友App

評論