對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 8153

8153 大家好,博主最近有事忙了幾天,沒有更新,今天正式回來了。那么又到了每日學習的時間了,今天咱們來聊一聊 簡談FPGA的上電復位,歡迎大家一起交流學習。 在基于verilog的FPGA設計中,我們常常

2018-06-18 19:24:11 19894

19894

最近看advanced fpga 以及fpga設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-09-01 15:37:07 1461

1461

本篇文章參考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在沒看這篇文章前,回想一下平時我們常用的復位方式

2020-11-18 17:32:38 3110

3110 內都是將復位信號作為一個I/O口,通過撥碼開關硬件復位。后來也看了一些書籍,采用異步復位同步釋放,對自己設計的改進。 不過自從我研讀了Xilinx的White Paper后,讓我對復位有了更新的認識

2020-12-25 12:08:10 2303

2303

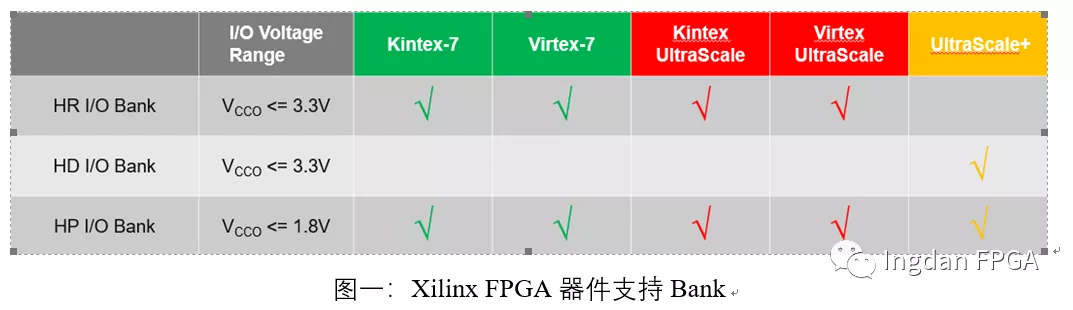

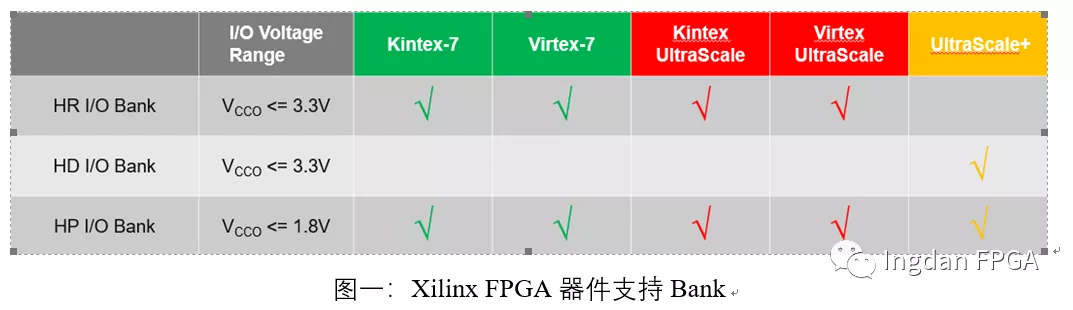

FPGA是電子器件中的萬能芯片,Xilinx FPGA處于行業龍頭地位更是非常靈活。FPGA管腳兼容性強,能跟絕大部分電子元器件直接對接。Xilinx SelectIO支持電平標準多,除MIPI

2022-08-02 09:31:28 4824

4824

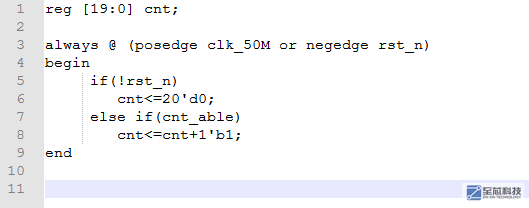

在FPGA設計中,復位電路是非常重要的一部分,它能夠確保系統從初始狀態開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復位電路:同步復位、異步復位和異步復位同步釋放,以及相應的Verilog代碼示例。

2023-05-14 14:44:49 1679

1679

在FPGA設計中,當復位整個系統或功能模塊時,需要將先關寄存器被清零或者賦初值,以保證整個系統或功能運行正常。在大部分的設計中,我們經常用“同步復位”或“異步復位”直接將所有的寄存器全部復位,這部分可能大家都習以為常。但實際上,是否需要每個寄存器都進行復位呢?這是一個值得探討的問題。

2023-05-14 14:49:19 1701

1701

鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 2883

2883

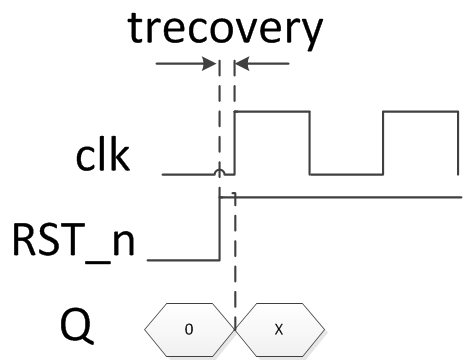

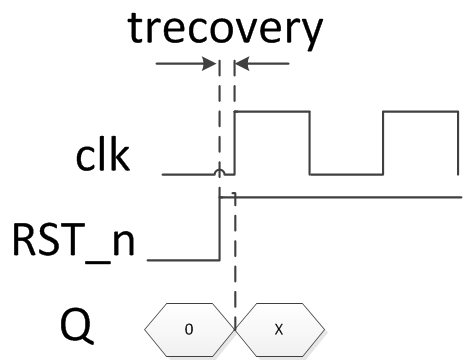

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2023-06-21 09:59:15 647

647

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1956

1956

需要注意以下幾個要點:●盡可能使用FPGA的專用復位引腳。(特權同學,版權所有)●上電復位時間的長短需要做好考量。(特權同學,版權所有)●確保系統正常運行過程中復位信號不會誤動作。(特權同學,版權所有) Xilinx FPGA入門連載

2019-04-12 06:35:31

隨著FPGA設計越來越復雜,芯片內部的時鐘域也越來越多,使全局復位已不能夠適應FPGA設計的需求,更多的設計趨向于使用局部的復位。本節將會從FPGA內部復位“樹”的結構來分析復位的結構。我們的復位

2019-05-17 08:00:00

FPGA的任意一個管腳都可以作為時鐘輸入端口,但是FPGA專門設計了全局時鐘,全局時鐘總線是一條專用總線,到達片內各部分觸發器的時間最短,所以用全局時鐘芯片工作最可靠,但是如果你設計的時候時鐘太多

2012-02-29 09:46:00

本帖最后由 ycq654263138 于 2012-9-13 16:53 編輯

各位FPGA工程師們,本人FPGA新手,但對FPGA有著極大的興趣!所以,想問問前輩們,你們的FPGA開發板,你

2012-09-06 16:19:02

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA技巧Xilinx,

2017-10-21 20:30:04

FPGA技巧Xilinx,,

2017-09-28 13:45:41

圖如圖2所示。圖2 異步復位電路圖根據異步電路的特點,異步復位的優點有:(1)由于多數目標器件庫的觸發器都包含異步復位端口,異步復位會節約邏輯資源。(2)異步復位設計簡單。(3)對于多數FPGA,均有

2021-06-30 07:00:00

FPGA設計高級技巧Xilinx篇

2012-08-11 16:07:48

Use Virtual IO core and TCL script to accommodate FPGA debugging/testing.基礎:Virtual IO 是Xilinx FPGA

2012-03-08 15:29:11

本本將從常見的XILINX FPGA和Altera 兩家FPGA的電源供電作如下介紹:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

`Xilinx FPGA入門連載17:PWM蜂鳴器驅動之復位與FPGA重配置功能特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1 復位

2015-10-26 12:05:15

Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之FPGA配置芯片固化Lesson19 特權Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之復位與FPGA重配

2015-07-22 11:49:20

Xilinx_FPGA_內部結構深入分析存儲單元存儲單元可以配置為D觸發器,就是我們常說的FF,Xilinx稱之為FD;也可以配置為鎖存器,Xilinx稱之為LD。輸出和三態通路各有一對寄存器外加一

2012-08-02 22:48:10

好。 另外就是關于塊RAM,Xilinx的雙口RAM是真的,Altera的沒有雙口RAM,如果你要實現真正的雙口RAM,只能用兩塊RAM來背靠背地實現,這樣你的RAM資源就少了一半,如果你的應用對片內雙口RAM的需求很重要,用Altera的就劃不來。更多資料請點擊下載:[hide][/hide]

2012-02-28 14:40:59

您好Xilinx社區,有人能否就Spartan-6 FPGA是否需要設計中的上電復位電路給出明確的答案?在附圖中,我們的設計中有這個上電復位電路。然而,我們遇到了電路問題,并決定在我們的設計中將

2019-04-18 10:15:45

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產品介紹使用Xilinx的FPGA、SoC和ACAP進行設計和開發

2021-01-22 06:38:47

Altera所不及,馬上要找工作了,僅僅會一點Altera的FPGA,對當前國內大部分公司用的FPGA是什么都不太清楚,Xilinx做的那么好市場那么大,我學的Altera是否還有用武之地,望大神們賜教,別跟我說學什么都一樣,我只是想知道現狀,謝謝

2016-12-04 15:42:25

很逼真的水淹電腦屏保_可能會嚇壞你哦

2008-06-23 12:34:52

本帖最后由 jfzhangjin 于 2015-1-8 10:48 編輯

之前也一直在做關于Xilinx FPGA各個方面的文章,但是總體而言就顯得有些雜,總希望能有人能整理一下便于查閱;另外

2014-11-03 17:15:51

之前也一直在做關于Xilinx FPGA各個方面的文章,但是總體而言就顯得有些雜,總希望能有人能整理一下便于查閱;另外針對目前電子發燒友網舉辦的“玩轉FPGA:iPad2,賽靈思開發板等你拿

2014-11-05 13:56:42

xilinx fpga開發板spartan6 xilinx spartan-6 xilinx板xilinx套件我希望在1周內從新加坡這個董事會更老。如果你知道plz與我分享link.thx以上

2019-07-22 09:00:55

,但不建議在 FPGA 內部使用鎖存器形式的異步邏輯)。每個寄存器的時鐘(或使能信號)可以配置為高電平有效或低電平有效。同樣,置位 / 復位輸入的有效電平也是可配置的。 這些邏輯塊可以被視為漂浮

2020-10-22 11:46:32

我有一個用于過時的Xilinx FPGA的加載文件。是否有機會將其轉換為Xilinx新FPGA的文件?例如斯巴達。以上來自于谷歌翻譯以下為原文I have a loading fille fora

2019-02-13 07:53:44

簡化Xilinx和Altera FPGA調試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內部迅速移動探點,而無需重新編譯設計方案。能夠把內部FPGA

2009-11-20 17:46:26 26

26 十分鐘學會Xilinx FPGA 設計

Xilinx FPGA設計基礎系統地介紹了Xilinx公司FPGA的結構特點和相關開發軟件的使用方法,詳細描述了VHDL語言的語法和設計方法,并深入討

2010-03-15 15:09:08 177

177 安富利推出Xilinx Virtex-6 FPGA DSP開發工具套件安富利公司旗下運營機構安富利電子元件宣布推出Xilinx Virtex -6 FPGA DSP開發工具套件。這套件是為DSP設計而打造,是Xilinx目標設計平

2010-04-24 09:56:31 1331

1331 本書系統地論述了Xilinx FPGA開發方法、開發工具、實際案例及開發技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發基礎與進階、Xilinx FPGA電路原理與系統設計

2012-07-31 16:20:42 11268

11268

本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201 Xilinx FPGA設計進階(提高篇)

有需要的下來看看

2015-12-29 15:45:48 12

12 Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發環境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發環境

2016-01-18 15:30:32 45

45 Xilinx-ISE9.x-FPGA-CPLD設計指南合集

2022-03-22 18:03:09 76

76 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 FPGA學習資料教程之Xilinx-FPGA-引腳功能詳細介紹

2016-09-01 15:27:27 0

0 FPGA學習資料教程之Xilinx-FPGA高級開發工具,感興趣的可以看看。

2016-09-01 15:27:27 0

0 賽靈思(Xilinx)公司FPGA器件的高速串行收發器類別如下

2017-02-11 11:11:30 5958

5958

在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 876

876

當ISE調用ModelSim進行仿真的時候,如果在FPGA設計中使用了Xilinx提供的的IP core或者其他的原語語句,ModelSim不添加Xilinx相應的庫文件的話,是無法仿真的。

2017-02-11 15:22:37 1274

1274

(Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 64

64 文檔內容包含基于Xilinx FPGA的開發板代碼及原路圖,供網友參考。

2017-09-01 11:09:24 20

20 FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14 Xilinx FPGA的Maxim參考設計

2017-10-31 09:59:24 23

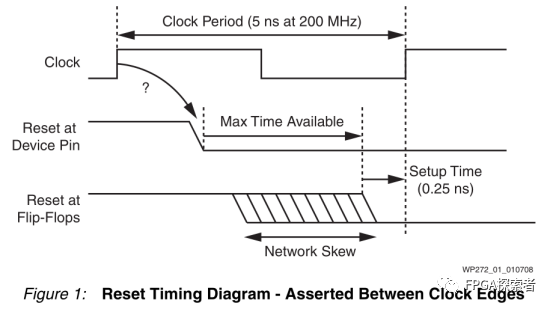

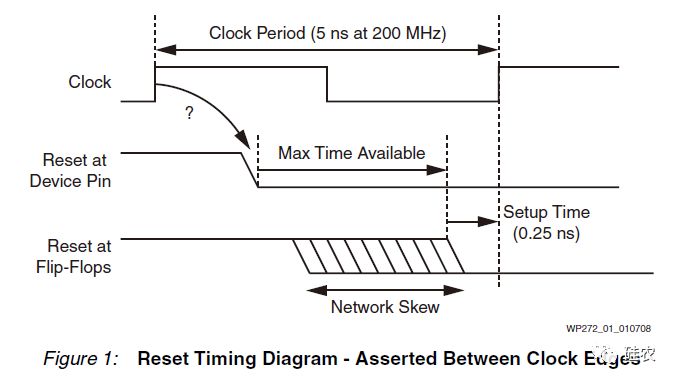

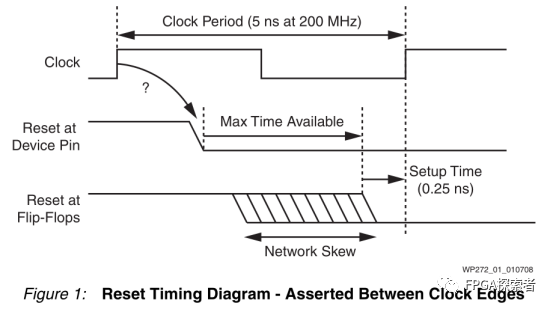

23 在FPGA設計中,復位起到的是同步信號的作用,能夠將所有的存儲元件設置成已知狀態。在數字電路設計中,設計人員一般把全局復位作為一個外部引腳來實現,在加電的時候初始化設計。全局復位引腳與任何其它輸入

2017-11-22 17:03:45 5125

5125

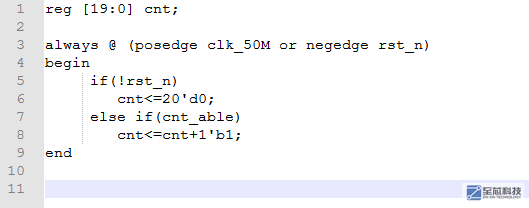

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1989

1989 對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 JESD204B協議是目前高速AD,DA通用的協議。對于基帶使用FPGA用戶來說,Xilinx品牌的FPGA使用更為常見。Xilinx提供了JESD204的IP core,設計起來比較方便。

2018-07-04 10:12:00 3977

3977 使用TI解決方案為Xilinx新型FPGA提供電源(一)

2018-08-22 00:01:00 3168

3168 在實際設計中,由于外部阻容復位時間短,可能無法使FPGA內部復位到理想的狀態,所以今天介紹一下網上流行的復位邏輯。

2018-08-07 09:17:18 10969

10969 FPGA的可靠復位是保證系統能夠正常工作的必要條件,本文對FPGA設計中常用的復位設計方法進行了分類、分析和比較,并針對各種復位方式的特點,提出了如何提高復位設計可靠性的方法。

2018-08-08 15:14:23 10154

10154 FPGA本身是有專門的時鐘cell的,以xilinx FPGA為例,就是primitive庫中的BUFG。

2018-12-22 15:33:59 1588

1588 在此Xilinx研究實驗室演示中,解釋了單源SYCL C ++示例以及生成在Xilinx FPGA上運行的硬件實現的方法。

2018-11-20 06:30:00 2918

2918 Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 3322

3322 xilinx推薦盡量不復位,利用上電初始化,如果使用過程中需要復位,采用同步高復位。

2019-02-14 14:29:49 5419

5419 復位信號設計的原則是盡量不包含不需要的復位信號,如果需要,考慮使用局部復位和同步復位。

2019-10-27 10:09:53 1735

1735

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n做異步復位、同步釋放處理,然后這個復位信號輸入PLL,同時將clk也輸入PLL。設計的初衷是在PLL輸出有效時鐘之前,系統的其他部分都保持復位狀態。

2020-03-29 17:19:00 2456

2456

最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。 流程: 1. 異步復位: 優點:⑴大多數

2020-10-30 12:17:55 323

323 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個工藝級別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點 4.7系列

2020-11-13 18:03:30 14065

14065 最近看 advanced fpga 以及 fpga 設計實戰演練中有講到復位電路的設計,才知道復位電路有這么多的門道,而不是簡單的外界信號輸入系統復位。

2020-12-22 12:54:00 13

13 本文檔的主要內容詳細介紹的是Xilinx 7 系列FPGA中的Serdes總結。

2020-12-31 17:30:58 25

25 SSM2518 pmod Xilinx FPGA參考設計

2021-04-20 16:05:07 3

3 AD5933 pmod Xilinx FPGA參考設計

2021-04-21 18:41:19 3

3 AD7780 pmod Xilinx FPGA參考設計

2021-04-22 13:35:23 11

11 引言: 我們在進行FPGA原理圖和PCB設計時,都會涉及到FPGA芯片管腳定義和封裝相關信息,本文就Xilinx 7系列FPGA給出相關參考,給FPGA硬件開發人員提供使用。通過本文,可以了解到:

2021-05-01 09:47:00 10367

10367

ADXL362 pmod Xilinx FPGA參考設計

2021-05-11 10:44:18 9

9 ADT7420 pmod Xilinx FPGA參考設計

2021-05-12 08:08:26 3

3 ADXL345 pmod Xilinx FPGA參考設計

2021-05-16 19:45:16 8

8 ADP5589 pmod Xilinx FPGA參考設計

2021-05-16 20:37:58 1

1 AD5628 pmod Xilinx FPGA參考設計

2021-05-19 14:34:17 4

4 AD5541A pmod Xilinx FPGA參考設計

2021-05-19 15:15:19 11

11 AD7193 pmod Xilinx FPGA參考設計

2021-05-19 15:18:13 2

2 AD7091R pmod Xilinx FPGA參考設計

2021-05-19 18:31:59 7

7 AD7156 pmod Xilinx FPGA參考設計

2021-05-20 12:32:16 10

10 AD7991 pmod Xilinx FPGA參考設計

2021-05-20 12:37:26 12

12 AD5781 pmod Xilinx FPGA參考設計

2021-05-24 10:29:20 17

17 基于FPGA的小波濾波抑制復位噪聲方法

2021-07-01 14:42:09 24

24 Xilinx FPGA開發實用教程資料包免費下載。

2022-04-18 09:43:46 24

24 自 1985 年 Xilinx 開發出第一個商業上可行的 FPGA 以來,FPGA 細分市場的價值已經增長到數十億美元。Xilinx 本身的年收入超過 30 億美元,在汽車、5G、基礎設施和數

2022-08-05 16:49:26 979

979 有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-03-13 10:29:49 1585

1585 本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。在FPGA和ASIC設計中,對于復位這個問題可以算是老生常談了,但是也是最容易忽略的點。本文結合FPGA的相關示例,再談一談復位。

2023-05-12 16:37:18 3347

3347

本文將探討在? FPGA ?設計中添加復位輸入的一些后果。 本文將回顧使用復位輸入對給定功能進行編碼的一些基本注意事項。設計人員可能會忽略使用復位輸入的后果,但不正確的復位策略很容易造成重罰。復位

2023-05-25 00:30:01 483

483 有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-05-25 15:50:45 2110

2110

Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 盡量少使用復位,特別是少用全局復位,能不用復位就不用,一定要用復位的使用局部復位;

2023-06-21 09:55:33 1337

1337

能不復位盡量不用復位,如何判斷呢?如果某個模塊只需要上電的時候復位一次,工作中不需要再有復位操作,那么這個模塊可以不用復位,用上電初始化所有寄存器默認值

2023-06-28 14:44:46 526

526

如果FPGA沒有外部時鐘源輸入,可以通過調用STARTUP原語,來使用FPGA芯片內部的時鐘和復位信號,Spartan-6系列內部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 215

215

電子發燒友App

電子發燒友App

評論