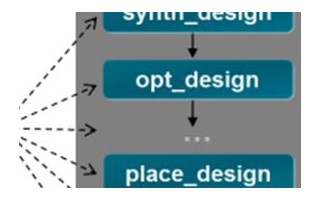

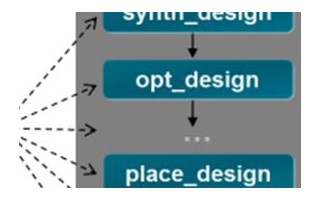

FPGA開發基本流程包括:設計輸入、設計仿真、設計綜合、布局布線,它們的連接關系如圖1 所示。

2010-06-10 08:24:15 1687

1687 設計人員選擇具有優秀調試能力的FPGA器件,可以縮短開發周期并降低成本,同時顯著加快上市速度。

2016-11-10 01:14:11 1617

1617

如圖1.9所示。這個流程圖是一個相對比較高等級的FPGA開發流程,從項目的提上議程開始,設計者需要進行FPG

2017-10-24 10:43:09 7183

7183

的事?很可能從來就沒有過。隨著FPGA變得越來越強大,處理的任務范圍也越來越廣,縮短設計周期并且最小化風險變得前所未有的重要。 Pentek公司作為一家商用現貨(COTS)FPGA的數據處理和采集產品制造商,通常是FPGA技術與最終用戶應用之間的接口。這使得Pentek處于

2020-12-20 10:04:00 1715

1715 FPGA 的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟 IC 設計流程類似,可以分為前端設計和后端設計。

2023-04-23 09:08:49 1577

1577

藥的研發周期從數年縮短至1個月,研發成本降低70%。 ? 近段時間,以ChatGPT為代表的大模型掀起新一輪人工智能熱潮,除了在娛樂、問答聊天、寫程序的應用之外,大模型產業化的應用也備受關注。 ? 2021年4月,華為云盤古大模型正式發布。

2023-03-31 01:19:00 3514

3514

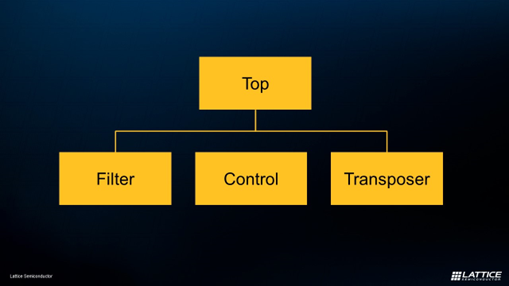

PLL、專用時鐘沿和I/O gearing邏輯解決了高速串行傳感器接口。最后,萊迪思半導體(Lattice)的 XP2提供了具有成本效益的8×8mm面積。此外,由于其非易失的特性,LatticeXP2系列

2011-05-24 14:17:00

FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖1-10所示,包括電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真

2021-07-23 09:12:07

FPGA應用設計中一種嶄新的硬宏開發流程是怎樣的

2021-05-06 06:49:19

如圖1.6所示。這個流程圖是一個相對比較高等級的FPGA開發流程,從項目的提上議程開始,設計者需要進行FPGA功能的需求分析,然后進行模塊的劃分,比較復雜和龐大的設計,則會通過模塊劃分把工作交給一個

2019-01-28 04:24:37

和萊迪思半導體的Mach XO / ICE40。中端FPGA這些類型的FPGA是低端和高端FPGA之間的最佳解決方案,它們是在性能和成本之間取得平衡而開發的。中端FPGA的示例是來自Altera

2018-12-14 17:39:44

FPGA的發展現狀如何?賽靈思推出的領域目標設計平臺如何簡化設計、縮短開發時間?

2021-04-08 06:18:44

FPGA的圖像傳感器的優勢公司Ing Arndt Bussmann,萊迪思半導體公司圖像采集是安全和監控視頻鏈中最關鍵的部 分,這是因為對于從視頻流提取有效信息的圖像信號處理能力是與獲取的圖像質量

2012-08-11 11:27:45

第二章 FPGA 開發流程FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件

2022-02-23 06:23:33

開發流程FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般如圖2所示,包括電路設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級

2017-01-10 15:50:15

的一條或多條路徑。在 FPGA 設計中主要有四種類型的時序約束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)約束。賽靈思FPGA設計時序約束指南[hide][/hide]`

2012-03-01 15:08:40

`低功耗的賽靈思 FPGA 系列使總線供電的 USB 器件設計垂手可得憑借在市場中數十億的端口數量,通用串行總線 (USB) 成為實現主機與外設之間千兆位以下連接的首選接口。不過,由于 USB 規范

2016-07-27 17:14:50

描述萊迪思HX4K FPGA 突破這款 FPGA 分線板旨在記錄如何開始 FPGA 編程,從硬件設計文件到加載比特流。為了嘗試將其作為一個項目進行訪問,該板的一個設計目標是使其能夠僅使用烙鐵進行手工

2022-08-23 07:21:04

萊迪思半導體公司和SiFive,Inc。最近,他們同意共同合作,通過萊迪思FPGA產品系列(包括最新的28 nm CrossLink-NX?FPGA),為開發人員輕松提供SiFive可擴展核心IP

2020-07-27 17:57:36

(G.8275.2)T-BC、T-TSC C類的ITU定時特性(G.8273.2)基于萊迪思FPGA的全新開發平臺也已添加到萊迪思ORAN方案中。包括了FPGA板和定時源開發板的安全定時和同步套件旨在簡化新的電信應用的測試、演示和開發。

2023-03-03 16:52:10

ASIC的設計流程是怎樣的?FPGA的開發流程又是怎樣的?

2021-11-01 07:08:47

PADS 制造準備可幫助您優化產品質量,縮短周期時間和節省成本。

2019-05-06 11:01:48

國產有哪些FPGA入門?萊迪思半導體?高云半導體?

2023-12-05 16:05:38

我們正在開發基于 imx8mp 處理器的產品。它通過 i2c 總線將程序加載到萊迪思 CrossLink FPGA。FPGA 二進制數據大小(.ied 文件)為 149KB,使用 400 KHz

2023-05-16 06:28:53

{:1:}推薦一種設計流程,它在電機控制設計中利用了 Altera FPGA 強大的適應能力、精度可調數字信號處理 (DSP) 以及集成系統設計工具。工業電機驅動設備的設計人員可

2013-11-14 00:36:28

本帖最后由 廣州虹科_FPGA技術支持 于 2020-10-29 17:44 編輯

VSTAR是一款輔助FPGA開發的調試工具,能夠大幅縮短debug階段的調試時間。對于使用Xilinx

2020-10-29 17:35:56

,FPGA能否在以便攜產品為主體的消費電子領域占到一席之地呢?對于這個問題,萊迪思半導體公司給出了肯定的答案。

2019-09-03 07:55:28

1.XILINX ISE傳統FPGA設計流程利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現、布線后仿真與驗證和下班調試等步驟。如下圖所示。1)電路設計

2021-05-27 09:28:40

,加速產品上市進程,大大降低風險 美國俄勒岡州希爾斯波羅市 — 2015年3月2日 —萊迪思半導體公司(NASDAQ: LSCC)—超低功耗、小尺寸客制化解決方案市場的領導者,今日宣布推出三款可免費下載

2019-06-17 05:00:07

前言 本部門所承擔的FPGA設計任務主要是兩方面的作用:系統的原型實現和ASIC的原型驗證。編寫本流程的目的是:l在于規范整個設計流程,實現開發的合理性、一致性、高效性。l形成風格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設計流程指南本部門所承擔的FPGA設計任務主要是兩方面的作用:系統的原型實現和ASIC的原型驗證。編寫本流程的目的是:l在于規范整個設計流程,實現開發的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

的處理器,優化了性能和成本通過不同的電壓和各種接口,如SPI、I2C、SDIO、PCI和LPC之間的橋接,最大化組件選擇的靈活性萊迪思FPGALCMXO2-640HC-4TG100C可編程邏輯器件FPGA

2019-09-20 15:13:30

又不足以提供全面的動態保護和恢復。萊迪思此次所推出的全面、真正并行、納秒級響應的安全方案可完美解決以上痛點,提供動態信任。 安全問題貫穿了設備整個生命周期,每一環節都至關重要,尤其固件正逐漸成為常見

2020-09-07 17:16:48

I2C 通道替代其中一個 I2S 接口。”理想的解決方案是采用低成本的現場可編程門陣列(FPGA),如萊迪思半導體的 iCE40 UltraPlus?器件( 圖 3)。圖 3. FPGA 價格較低且非常

2020-10-22 11:30:53

接口。”理想的解決方案是采用低成本的現場可編程門陣列(FPGA),如萊迪思半導體的 iCE40UltraPlus?器件(圖 3)。圖 3.FPGA 價格較低且非常靈活使用 FPGA 實現單線聚合功能

2020-10-23 09:16:56

I2C 通道替代其中一個 I2S 接口。”理想的解決方案是采用低成本的現場可編程門陣列(FPGA),如萊迪思半導體的 iCE40 UltraPlus?器件( 圖 3)。圖 3. FPGA 價格較低且非常

2021-05-25 14:36:00

的應用。采用FPGA技術構造雙口RAM,實現高速信號采集系統中的海量數據存儲和時鐘匹配。功能仿真驗證該設計的正確性,該設計能減小電路設計的復雜性,增強設計的靈活性和資源的可配置性能,降低設計成本,縮短

2010-04-24 09:44:28

位色深)。 萊迪思實現了同時支持DVI TX和RX功能的參考設計。該設計利用了LatticeECP3或LatticeECP2M FPGA系列中的CML SERDES通道,來支持更高速率的DVI傳輸

2019-06-05 05:00:17

本文以FPGA為核心構建了一種通用的雷達回波信號實時模擬系統。該系統采用FPGA作為回波信號模擬的運算單元,充分利用了FPGA資源豐富、并行處理能力強的特點,提高了系統的實時性;采用System

2021-04-29 06:14:20

本文采用atelra公司的可編程芯片FPGA設計了一款周期和輸出個數可變的脈沖發生器。經過板級調試獲得良好的運行效果。

2021-04-29 07:08:33

如何利用STM32F103X的串口對迪文屏發送及接收數據?

2021-12-06 07:04:09

求助高手,怎樣在labview中獲取周期波形中的一個周期的數據,方便后面的計算,我初步想法是利用matlab和labview結合使用,利用matlab的圖像處理技術不知是否可行

2013-07-14 14:37:30

全球可編程邏輯解決方案領導廠商賽靈思公司 (Xilinx Inc.) 宣布,為推進可編程勢在必行之必然趨勢,正對系統工程師在全球發布賽靈思新一代可編程FPGA平臺。和前代產品相比,全新的平臺功耗降低

2019-08-09 07:27:00

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

根據新的NIST SP 800 193標準、在硬件上使用基于FPGA的可信根器件來實現平臺硬件保護和恢復(PFR), 可讓服務器固件免受網絡攻擊,保護性能更上一層樓。萊迪思全新PFR開發工具套件能夠簡單快速實現基于FPGA的PFR解決方案。

2019-10-08 09:31:04

按照相對論的理論,時間也是可以被拉長縮短的,只不過需要巨大的能量支撐著您達到一個和光速可比擬的高速度而已。這話說著輕松,你我心里都明白,估計咱們的有生之年是看不到這樣的情景的…… 回到

2019-11-11 07:03:58

來自處理器或其他顯示控制輸出設備的RGB(紅色,綠色/藍色)像素總線數據。設計的輸出連接到D-PHY接口IP內核,允許FPGA直接驅動DSI接收設備,例如顯示器。并行RGB至DSI發送設計說明了萊迪思超低

2020-04-30 07:58:35

和工業安全等巨大商機更是鋪天蓋地而來。嵌入式系統作為兵家必爭的灘頭陣地,主控芯片商戰況火熱。 隨著賽靈思、阿爾特拉、萊迪思等一眾 FPGA 全球頂級大廠攜更高集成度、靈活、延遲小、處理速度快和整體成本

2014-07-22 13:49:58

這正是低功耗FPGA發揮作用的地方。與增強處理器來處理算法的方式不同,萊迪思iCE40 UltraPlus FPGA可以作為MCU的協處理器,處理MCU無法解決的復雜任務之余,將功耗保持在要求范圍內

2020-10-23 11:43:04

我正在使用 i.MX RT 1064 MCU 通過 NXP 的 FlexSPI 控制器通過 Quad SPI 連接到萊迪思 FPGA。FPGA 正在處理我們的外圍設備并將它從這些設備獲得的測量

2023-03-27 06:23:57

了解賽靈思產品的機會,利用賽靈思FPGA器件,開發設計產品,進一步提高FPGA設計能力和水平。 大賽參與情況 本次大賽主題是基于賽靈思(xilinx)FPGA芯片進行作品設計(芯片型號和應用領域不限

2012-09-06 11:52:48

專家進行探討交流的機會,提高對技術知識的應用和產品商業化的認知;為廣大電子愛好者深入了解賽靈思產品的機會,利用賽靈思FPGA器件,開發設計產品,進一步提高FPGA設計能力和水平。 大賽參與情況

2012-09-06 11:54:16

經歷過和牛人一起進行FPGA設計比賽的激烈競爭嗎?你感受過FPGA原廠開發板和fpga行業泰斗直接帶來的強烈震撼嗎? 沒經歷過沒關系,電子發燒友網主辦,賽靈思贊助的“賽靈思FPGA方案開發設計大賽”已經為

2012-04-23 09:31:16

只要有數字電路的基礎,還是能較容易和快速地學會利用 CPLD/FPGA 設計數字系統的。 數字系統的基本部件比較簡單,它們是一些與門、或門、非門、觸發器和多路選擇器等,宏器件是一些加法器、乘法器等

2019-02-28 11:47:32

本人手中有款LATTICE(萊迪思)100腳的貼片IC ,不知道其型號,底部印著AW44E開頭的,請那位高手指點一下是什么型號

2014-09-01 23:48:46

。ROHM與安富利公司共同開發賽靈思7系列FPGA及Zynq?–7000 All Programmable SoC的評估套件Mini-Module Plus 用的電源模塊。安富利公司已經開發出多款賽靈思

2018-12-04 10:02:08

1.XILINX ISE傳統FPGA設計流程利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現、布線后仿真與驗證和下班調試等步驟。如下圖所示。1)電路設計

2019-05-03 08:00:00

每一版本都提供了完整的FPGA設計流程,并且專門針對特定的用戶群體(工程師)和特定領域的設計方法及設計環境要求進行了優化。那大家知道賽靈思ISE? 設計套件11.1版對FPGA有什么優化作用嗎?

2019-07-30 06:52:50

【來源】:《電子設計工程》2010年02期【摘要】:<正>賽靈思公司與聯華電子共同宣布,采用聯華電子高性能40nm工藝的Virtex-6FPGA,已經完全通過生產前的驗證

2010-04-24 09:06:05

國內超過100億元的FPGA市場中,國產市占率僅為4%。目前,全球FPGA市場基本被四大巨頭壟斷:Xilinx(賽靈思)、Intel(英特爾,此前收購了Altera)、Lattice(萊迪思)、Mic...

2021-07-30 06:32:06

。此外,FPGA通常有很寬的溫度范圍,并有很長的產品生命周期。 針對ECP2M和ECP3器件系列,萊迪思(Lattice)半導體公司最近推出了DVI/HDMI接口的參考設計。萊迪思半導體公司

2019-06-06 05:00:34

章禮宏 范全潤1 引言隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

我們的客戶進行創新并加快其設計開發。萊迪思展臺展示了各類汽車級解決方案的最新演示,可用于打造基于萊迪思低功耗FPGA技術的各種車載應用。我們與行業領先的合作伙伴合作,展示了車載信息娛樂、電氣/電子架構

2023-02-21 13:40:29

`時代的發展衍生出了很多新的產品,近幾年流行于各大高級商務酒店、咖啡廳、西餐廳里的LED燈絲燈,在LED燈絲的點膠工藝上也是要求極高的。深圳市阿萊思斯科技有限公司從事全自動點膠機的研發生產已有10年

2018-07-14 10:09:47

嵌入式IC - FPGA(現場可編程門陣列), 197 I/O 256CABGA

2022-06-16 14:09:08

基于FPGA高速、可編程的優點,設計了一款可以靈活改變脈沖輸出周期和輸出個數的周期脈沖發生器。利用VHDL語言編寫了全部模塊,并在Altera公司提供的QuartusⅡ4.1開發軟件上實現了

2010-12-08 15:58:00 52

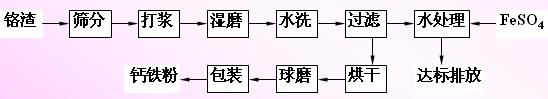

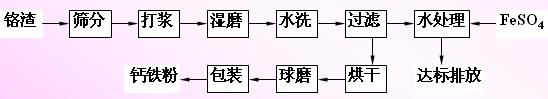

52 利用鉻渣制鈣鐵粉工藝流程

圖 利用鉻渣制鈣鐵粉工藝流程鉻渣制成的鈣鐵粉

2009-03-30 20:13:30 702

702

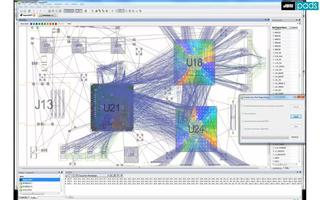

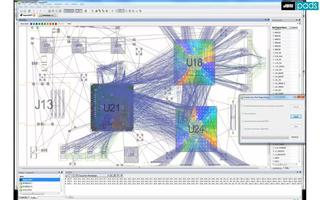

Mentor Graphics的FPGA Advantage是享譽業界,具有FPGA設計黃金組合的全流程設計工具。本次課程將使用戶體驗FPGA Advantage如何最大化地加速設計的實現以及復用。同時掌握如何利用FPGA Advantage快速實現設計從創建、理解、仿真驗證、綜合以及布局布線的全過

2011-03-15 13:39:56 97

97 WP409利用Xilinx FPGA打造出高端比特精度和周期精度浮點DSP算法實現方案: High-Level Implementation of Bit- and Cycle-Accurate Floating-Point DSP Algorithms with Xilinx FPGAs

2012-01-26 18:03:05 25

25 Alter FPGA的設計流程以及DSP設計.

2012-03-16 15:52:07 127

127 FPGA開發流程,好東西,喜歡的朋友可以下載來學習。

2016-01-18 15:17:27 32

32 FPGA的學習流程,有需要的朋友下來看看

2016-05-10 10:46:40 22

22 FPGA設計的流程,步驟,選型,仿真,軟硬件設計,調試流程。

2016-05-11 14:33:02 29

29 提高FPGA設計生產力的工具、技巧和方法,9影響FPGA設計周期生產力的最大因素是什么?

2017-02-11 12:22:06 587

587

1. FPGA 開發流程: 電路設計與設計輸入 ;仿真驗證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10000

10000 不斷 從賽靈思FPGA設計流程看懂FPGA設計 1.XILINX ISE傳統FPGA設計流程 利用XilinxISE軟件開發FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合

2018-02-20 20:32:00 15820

15820

本文首先介紹了FPGA發展由來,其次介紹了FPGA的硬件設計技巧及FPGA設計者的5項基本功,最后介紹了FPGA設計流程及工程師FPGA設計心得體會。

2018-05-31 09:35:06 11241

11241 本文檔的主要內容詳細介紹的是FPGA的設計流程是怎么樣的?FPGA設計流程指南詳細資料免費下載內容包括了:1.基于HDL 的FPGA 設計流程概述2.Verilog HDL 設計3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 29

29 Abhishek Kapoor與X-Microwave首席執行官John Richardson共同探討ADI與X-Microwave之間的合作X-Microwave工具和評估板將縮短設計周期時間,減少使用多個評估板。

2019-07-04 06:10:00 2336

2336 在遵循管腳特定的規則和約束的同時,可以在 PCB 上的多個 FPGA 之間自動優化信號管腳分配。減少布線層數,最大限度地減少 PCB 上的交叉數量并縮短總體走線長度,以及減少信號完整性問題,從而提高完成率并縮短 FPGA 的布線時間。

2019-05-14 06:23:00 3276

3276

Vishay宣布,為了兌現公司支持多層陶瓷片式電容器(MLCC)客戶的承諾,宣布縮短MLCC供貨周期。

2019-07-15 15:37:10 844

844 FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程一般包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

2019-11-06 15:17:28 2224

2224 FPGA的設計流程就是利用EDA開發軟件和編程工具對FPGA芯片進行開發的過程。FPGA的開發流程包括功能定義/器件選型、設計輸入、功能仿真、邏輯綜合、布局布線與實現、編程調試等主要步驟。

2019-11-20 15:06:28 1545

1545 最新才流行的嵌入式C程序。 FPGA的開發流程即是利用EDA開發軟件以及編程工具對FPGA芯片進行開發的過程。EDA ( Electronic Design Automation,電子設計自動化

2020-11-12 18:22:28 5791

5791 FPGA設計流程指南

2021-11-02 16:29:21 9

9 第二章 FPGA 開發流程FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件

2021-12-29 19:40:15 9

9 FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件描述語言)是兩種最常用的數字

2023-03-21 10:26:50 2624

2624 FPGA的設計流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態時序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設計的流程圖。

2023-07-04 12:06:08 795

795

??FPGA 的詳細開發流程就是利用 EDA 開發工具對 FPGA 芯片進行開發的過程,所以 FPGA 芯片開發流程講的并不是芯片的制造流程,區分于 IC 設計制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 2387

2387

根據瑞銀分析師最近提供給投資者的備忘錄,英偉達已經顯著縮短了其AI GPU的交付周期。這一周期已經從去年年底的8-11個月迅速縮短至目前的3-4個月。這一變化引發了市場的廣泛關注,分析師們普遍認為這背后有兩種可能的原因。

2024-02-18 17:31:09 451

451 電子發燒友網站提供《FPGA的PL端固化流程.pdf》資料免費下載

2024-03-07 14:48:58 0

0 FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 97

97

電子發燒友App

電子發燒友App

評論