No.1

什么是時序分析?

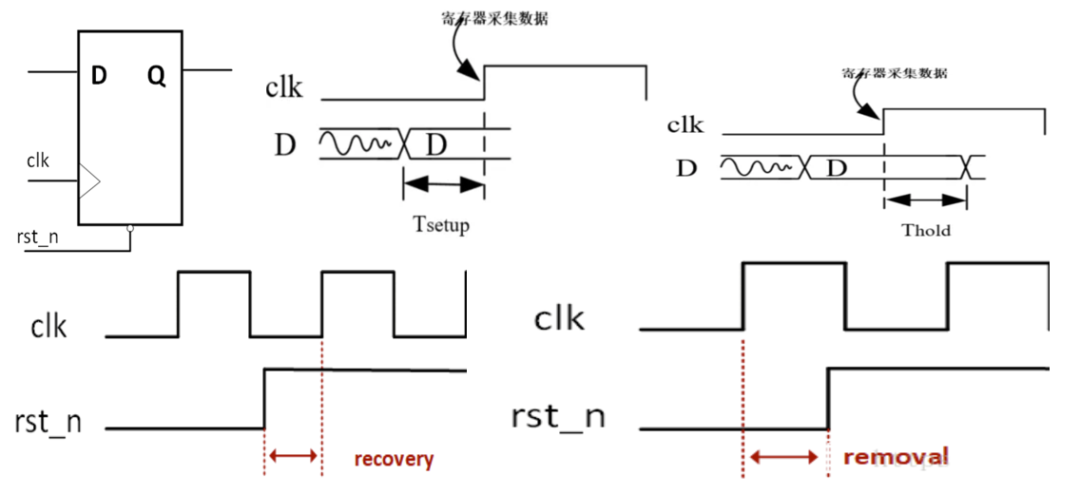

時序分析本質(zhì)上就是一種時序檢查,目的是檢查設(shè)計中所有的D觸發(fā)器是否能夠正常工作,也就是檢查D觸發(fā)器的同步端口(數(shù)據(jù)輸入端口)的變化是否滿足建立時間要求(Setup)和保持時間要求(Hold);檢查D觸發(fā)器的異步端口(異步復(fù)位端口)的變化是否滿足恢復(fù)時間要求(Recovery)和移除時間要求(Removal)。

No.2

時序分析有哪些類型?

時序分析包括靜態(tài)時序分析(STA)和動態(tài)時序分析。

動態(tài)時序分析: 將布局布線生成的布線延遲信息反標(biāo)注到門級網(wǎng)表中進行仿真,檢查是否存在時序違例。此時的仿真包括門延遲和布線延遲信息,能夠較好反應(yīng)芯片的實際工作情況。因為不可能產(chǎn)生完備的測試向量,覆蓋門級網(wǎng)表中的每一條路徑。因此在動態(tài)時序分析中,無法暴露一些路徑上可能存在的時序問題。

**靜態(tài)時序分析:**采用窮盡分析方法來提取出整個電路存在的所有時序路徑,計算信號在這些路徑上的傳播延時,檢查信號的建立和保持時間是否滿足時序要求,通過對最大路徑延時和最小路徑延時的分析,找出違背時序約束的錯誤。它不需要輸入向量就能窮盡所有的路徑,且運行速度很快、占用內(nèi)存較少,不僅可以對芯片設(shè)計進行全面的時序功能檢查,而且還可利用時序分析的結(jié)果來優(yōu)化設(shè)計,因此靜態(tài)時序分析已經(jīng)越來越多地被用到數(shù)字集成電路設(shè)計的驗證中。

No.3

時序分析使用的工具有哪些?

**> **靜態(tài)時序分析使用的工具:

①Xilinx Vivado Intergreated Design Environment Time Engine

③DC等

**> **動態(tài)時序分析使用的工具:

③Sysnopsys VCS

No.4

靜態(tài)時序分析之前的準(zhǔn)備工作

撰寫基本的時序約束文件,告知時序引擎一些必要的信息(比如時鐘,輸入輸出延時等)。若沒有正確的時序約束,那么時序分析的結(jié)果是沒有意義的。

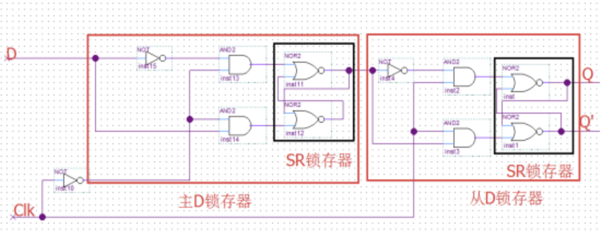

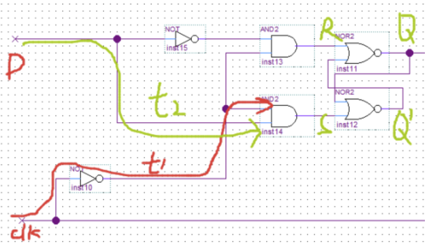

D觸發(fā)器中Tsetup,Thold,Tco的由來

No.5

時序分析中的常用術(shù)語

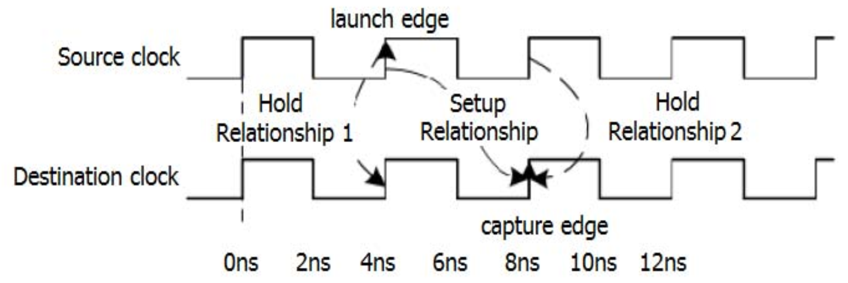

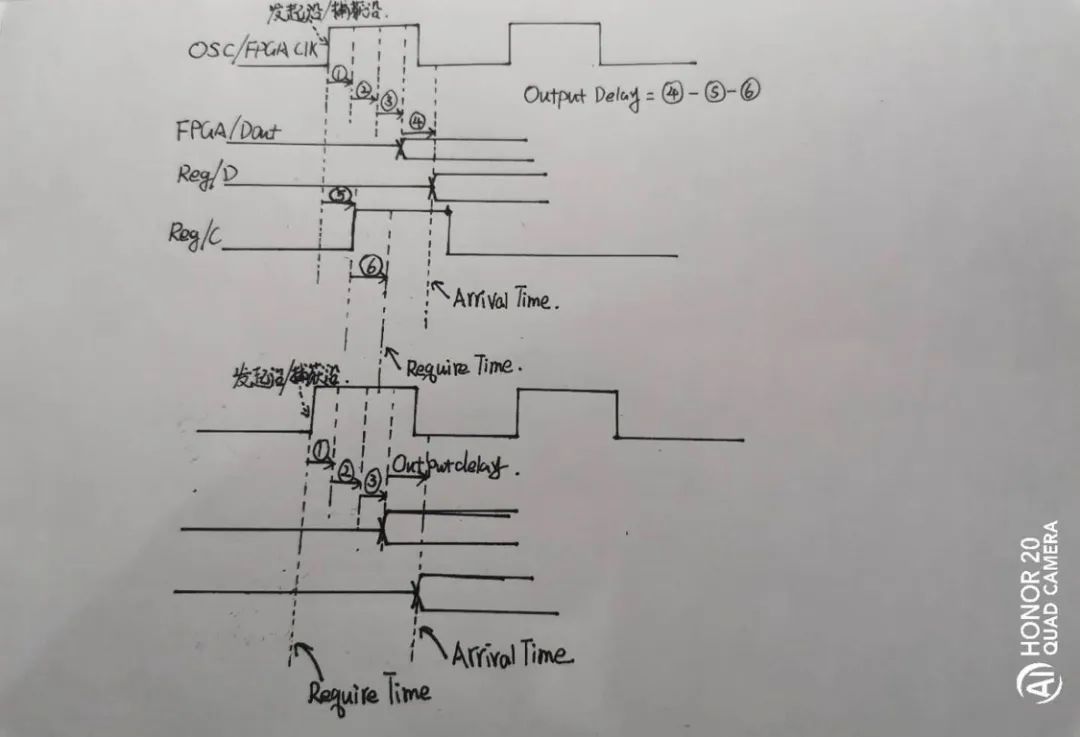

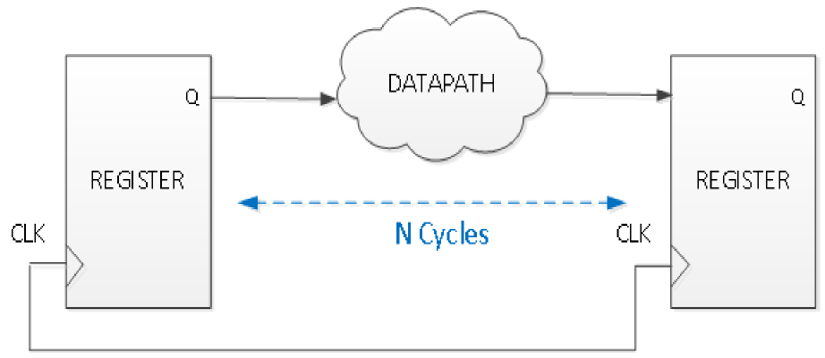

> 源時鐘 (Source Clock/Launch Clock,也稱為發(fā)起時鐘)

> 目的時鐘 (Destination Clock/Capture Clock,也稱為捕獲時鐘)

> 發(fā)起沿 (launch edge,源時鐘產(chǎn)生數(shù)據(jù)的有效時鐘沿)

> 捕獲沿 (capture edge,目的時鐘捕獲數(shù)據(jù)的有效時鐘沿)

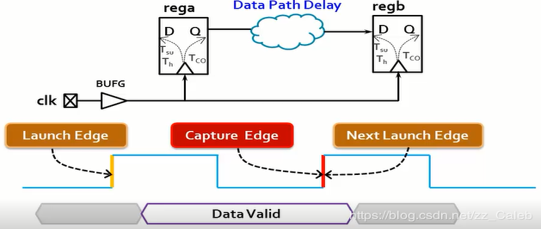

發(fā)起沿通常在0ns,捕獲沿通常在下一個發(fā)起沿,發(fā)起沿和捕獲沿通常相差一個時鐘周期。

No.6

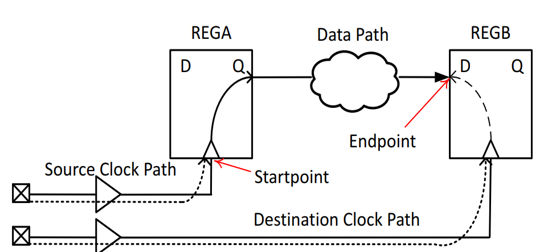

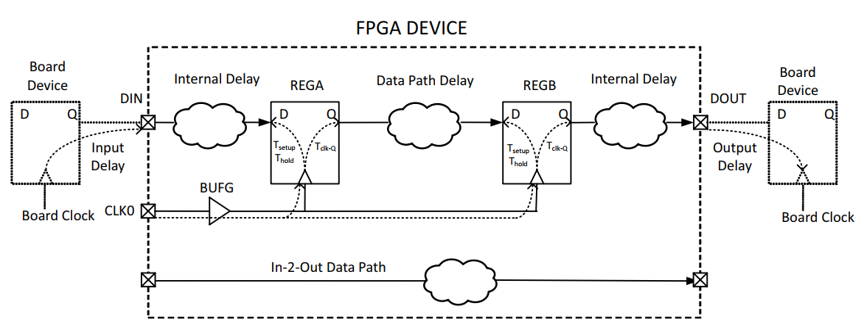

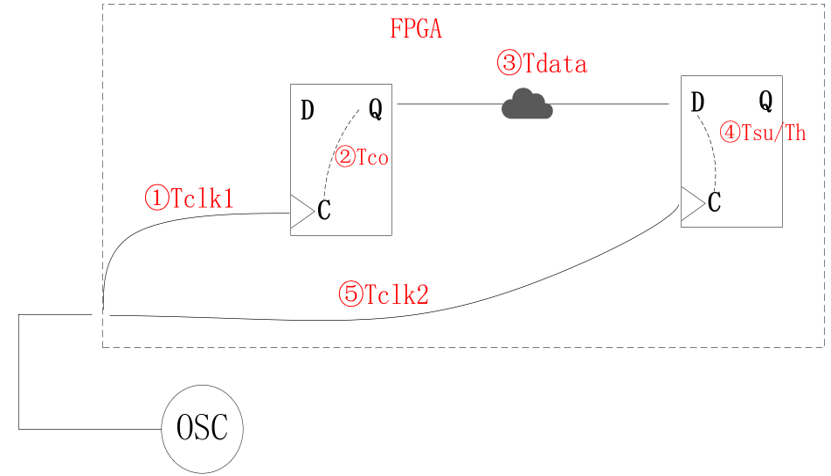

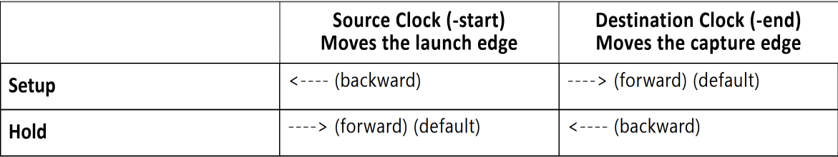

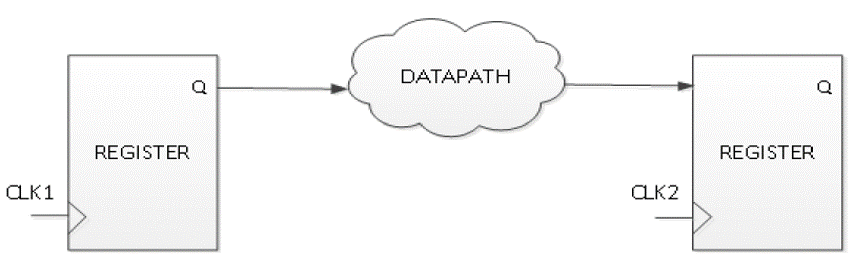

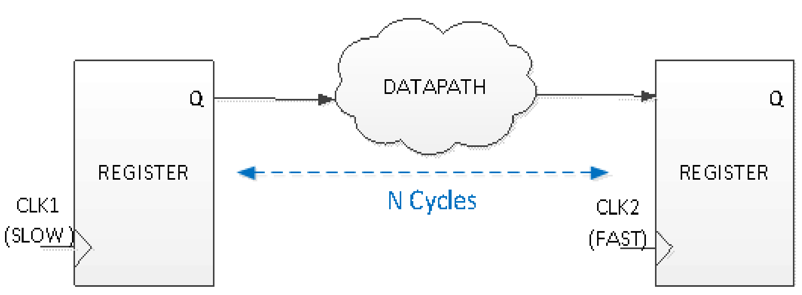

一條普通時序路徑的三要素

源時鐘路徑: 從源時鐘的源節(jié)點(通常是FPGA的時鐘輸入引腳)到源寄存器的時鐘端口的路徑。當(dāng)時序路徑的起點是FPGA輸入端口時,該時序路徑是沒有源時鐘路徑的。

數(shù)據(jù)路徑: 從時序路徑的起點到時序路徑的終點之間的數(shù)據(jù)傳播路徑。時序路徑的起點可以是源寄存器的時鐘端口或FPGA的輸入端口,時序路徑的終點可以是目的寄存器的輸入端口或FPGA的輸出端口。

目的時鐘路徑: 從目的時鐘的源節(jié)點(通常是FPGA的時鐘輸入引腳)到目的寄存器的時鐘端口的路徑。當(dāng)時序路徑的終點是FPGA的輸出端口時,該時序路徑是沒有目的時鐘路徑的。

No.7

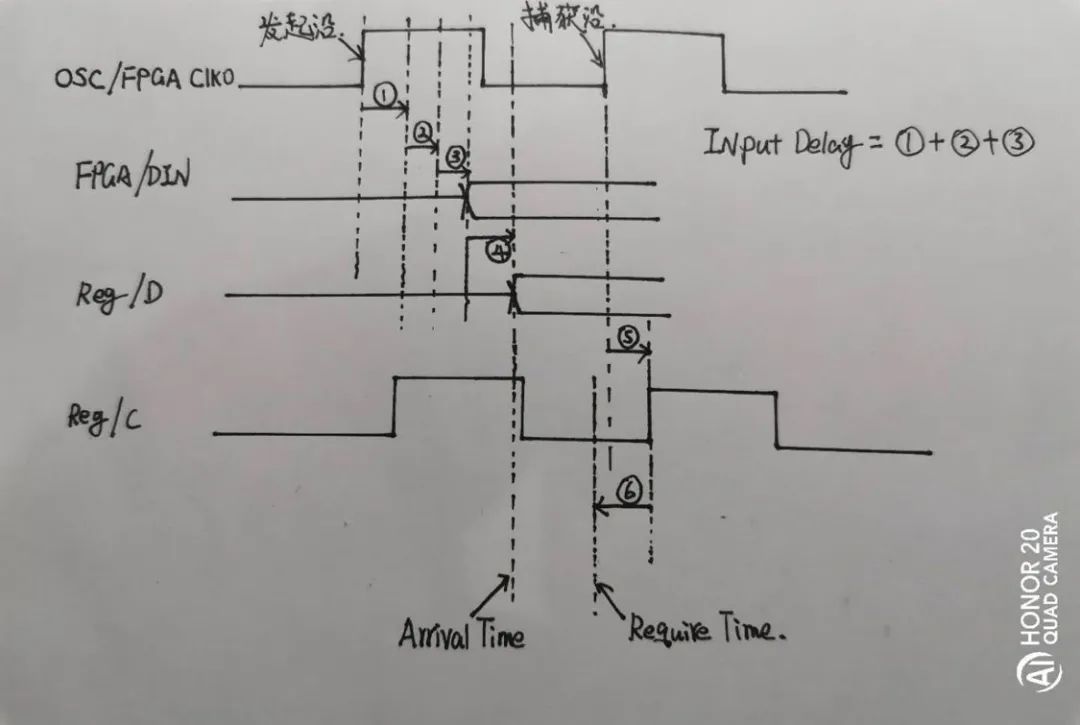

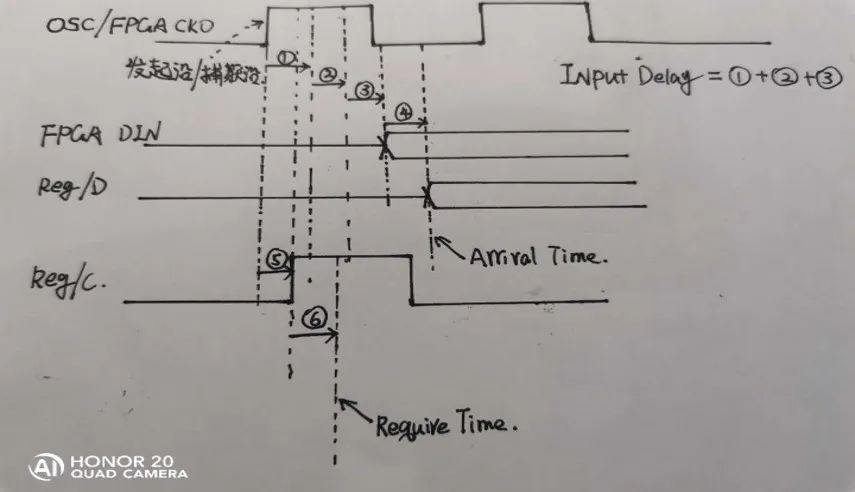

FPGA中常見的四種時序路徑

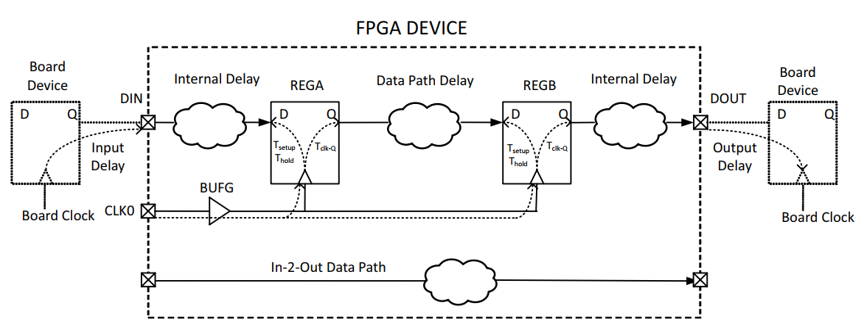

第一種,從FPGA的輸入端口到目的寄存器的數(shù)據(jù)輸入端口 。

**> **數(shù)據(jù)由Board clock發(fā)起并在FPGA外部產(chǎn)生;

**> **數(shù)據(jù)經(jīng)過Input Delay的延遲后到達(dá)FPGA的輸入端口;

**> **數(shù)據(jù)經(jīng)過FPGA的Internal Delay后到達(dá)由目的時鐘驅(qū)動的目的寄存器。

這種路徑是沒有源時鐘路徑的,用戶需要約束Input Delay和時鐘來告知時序引擎必要信息,時序引擎才能正確的分析這種路徑。

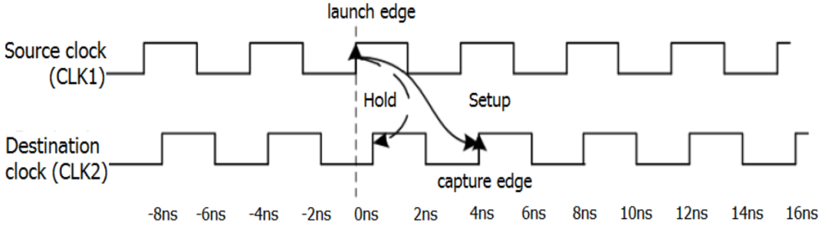

第二種,從源寄存器的時鐘端口到目的寄存器的數(shù)據(jù)輸入端口。

**> **數(shù)據(jù)由源時鐘發(fā)起并在FPGA內(nèi)部產(chǎn)生;

**> **數(shù)據(jù)經(jīng)過Data Path Delay后到達(dá)由目的時鐘驅(qū)動的目的寄存器。

這種時序路徑是最常見的,用戶需要約束源時鐘和目的時鐘告知時序引擎必要的信息,時序引擎才能正確的分析這種時序路徑。

第三種,從源寄存器的時鐘端口到FPGA的輸出端口。

**> **數(shù)據(jù)由源時鐘發(fā)起并在FPGA內(nèi)部產(chǎn)生;

**> **數(shù)據(jù)經(jīng)過Internal Delay后到達(dá)輸出端口;

**> **數(shù)據(jù)經(jīng)過Output Delay后被Board Clock捕獲到。

這種路徑是沒有目的時鐘路徑的,用戶需要約束Output Delay和時鐘來告知時序引擎必要信息,時序引擎才能正確的分析這種路徑。

第四種,從FPGA的輸入端口到FPGA的輸出端口。

**> **數(shù)據(jù)橫穿FPGA,沒有經(jīng)過任何觸發(fā)器,這種路徑也叫in-to-out path,約束輸入和輸出延時的參考時鐘可以使用虛擬時鐘。

這種路徑中只有數(shù)據(jù)路徑,用戶需要約束Input Delay和Output Delay,告知時序引擎必要的信息,時序引擎才能正確的分析這種時序路徑。

Setup檢查

No.1

時序引擎如何進行Setup檢查?

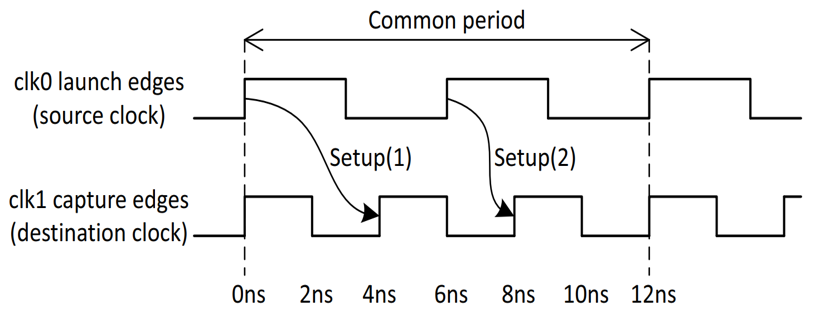

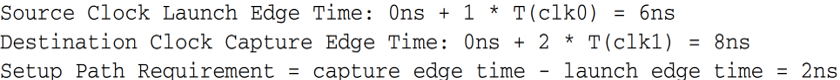

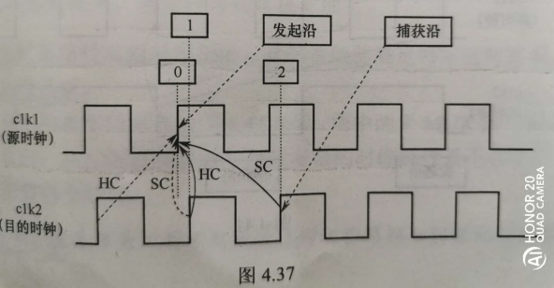

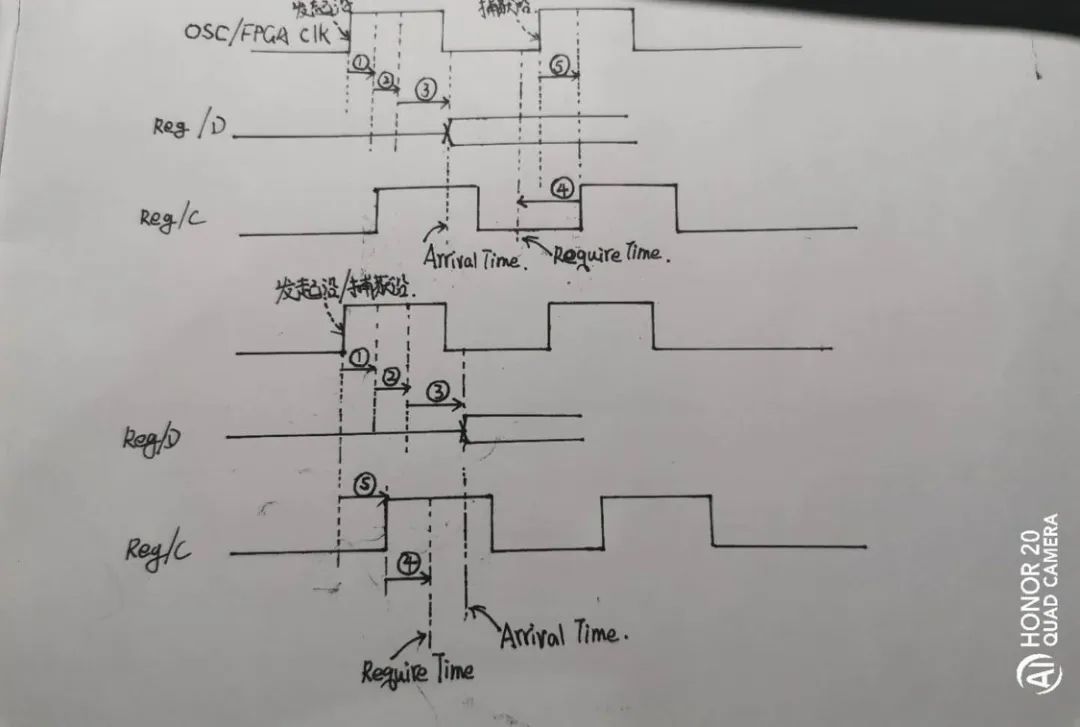

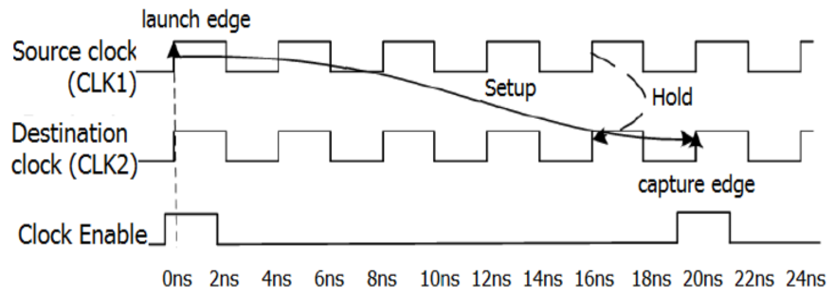

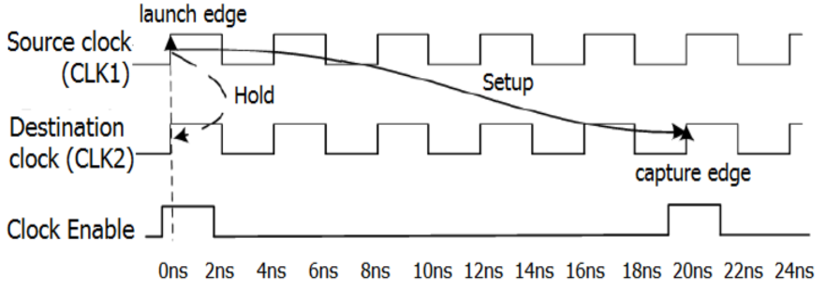

①確定建立時間要求 (確定用于建立時間分析的發(fā)起沿和捕獲沿)

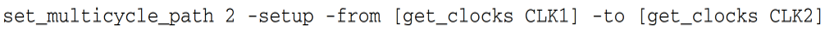

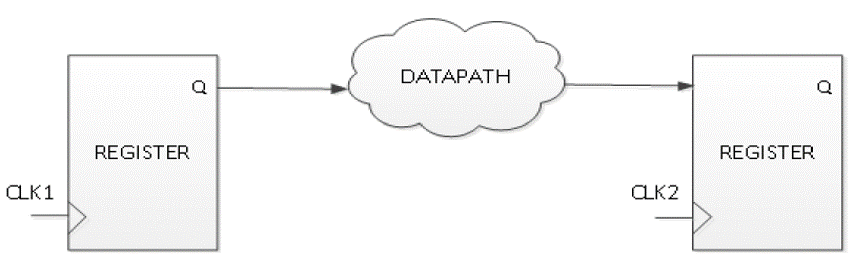

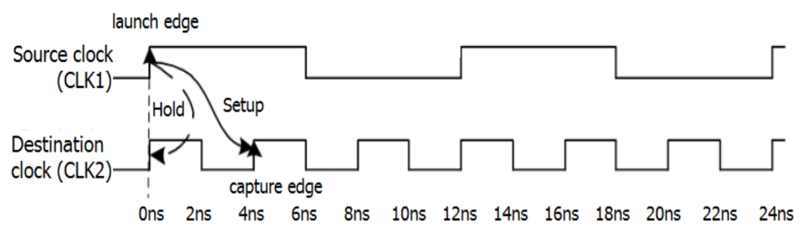

時序引擎會找出發(fā)起時鐘和捕獲時鐘的最小公共周期,然后在最小公共周期內(nèi)找到所有發(fā)起時鐘沿和捕獲時鐘沿的所有可能的情況,并在所有可能的情況中挑選出最小的建立時間需求(大于0),從而確定了Launch edge和Capture edge。

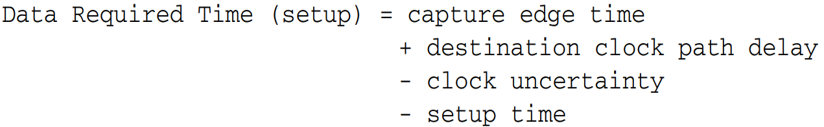

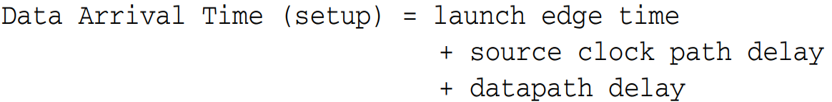

②計算數(shù)據(jù)的需求時間

③計算數(shù)據(jù)的到達(dá)時間

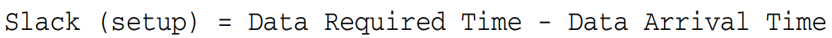

④計算Setup的裕量(Slack)

No.2

Setup分析實例

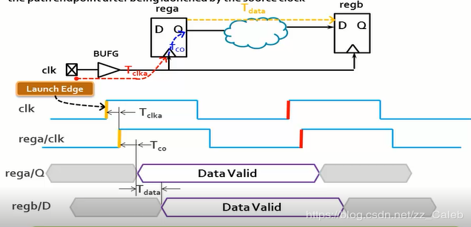

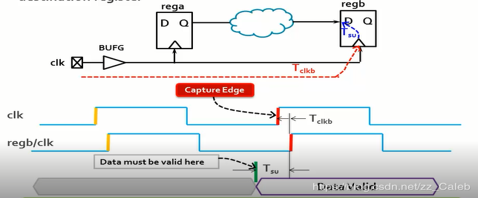

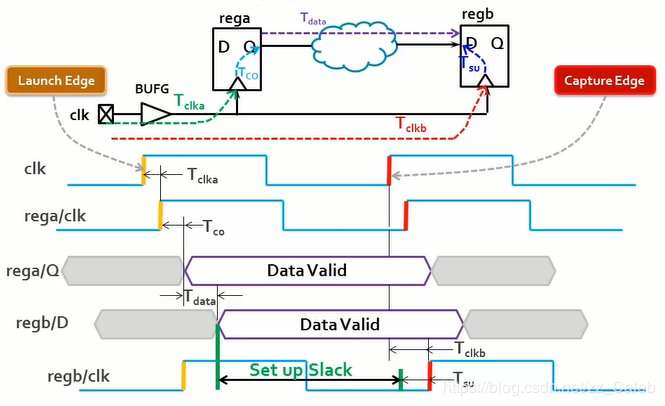

**> **Data Arrival time = lauch edge + Tclka + Tco + Tdata(Tlogic+Tnet)

> Data Require Time = capture edge + Tclkb - Tsu

> Setup Slack= Data Require Time - Data Arrival Time

No.3

根據(jù)公式分析哪些因素會導(dǎo)致Setup Slack為負(fù)呢?

**> **Setup Slack = (Capture edge – Launch edge)+ (destination clk delay – source clk delay)- Setup time - clk uncertainty – datapath delay

> Setup Slack = Setup Requirement(一定大于0) + clk skew – Tsu – Tclk uncertainty – Tlogic – Tnet - Tco

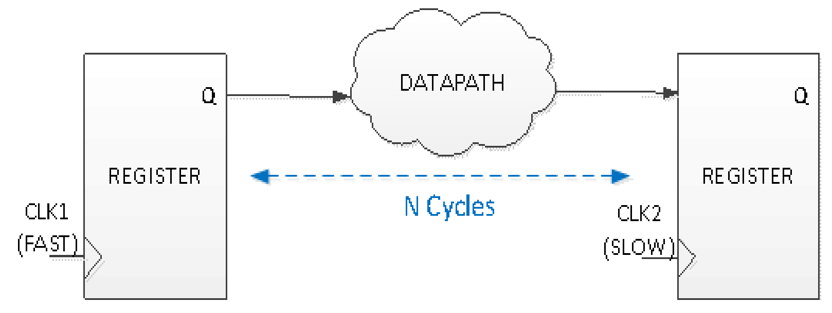

① Setup Requirement 與實際情況不符

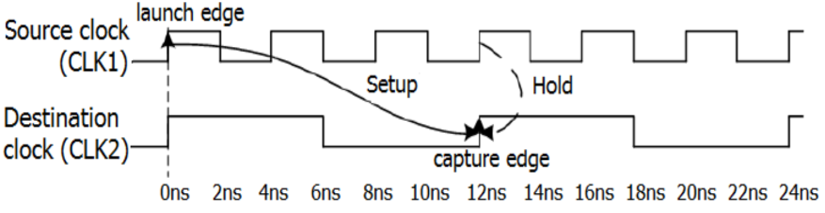

建立時間需求過小,這種情況通常會在同步跨時鐘域路徑中出現(xiàn),在同步跨時鐘域路徑中的源時鐘頻率與目的時鐘頻率的相位關(guān)系雖然是已知的,但是時序引擎默認(rèn)選擇的捕獲沿通常都是錯誤的,需要用戶通過多周期路徑約束的方式手動修正建立時間需求。比如下圖中,兩個同頻不同相的同步時鐘,時序引擎默認(rèn)選擇的捕獲沿是目的時鐘第二個上升沿,導(dǎo)致建立時間需求非常小,最終肯定會導(dǎo)致時序違例。

② clk skew為負(fù)值,且很大

通常情況下,同一個時鐘下的時鐘歪斜不應(yīng)該超過300ps,同步跨時鐘域路徑的時鐘歪斜不應(yīng)該超過500ps,異步跨時鐘域路徑的時鐘歪斜一般比較大,因為它們的時鐘源不同。

當(dāng)出現(xiàn)時鐘歪斜大的情況時:

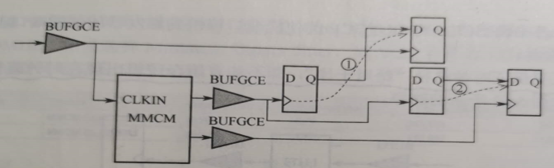

**> **檢查源時鐘路徑和目的時鐘路徑上是否干凈,時鐘路徑上是否引入了組合邏輯,時鐘路徑是否使用了過多的BUFGCE,時鐘路徑上是否級聯(lián)了多個BUFGCE導(dǎo)致時鐘延時變大。

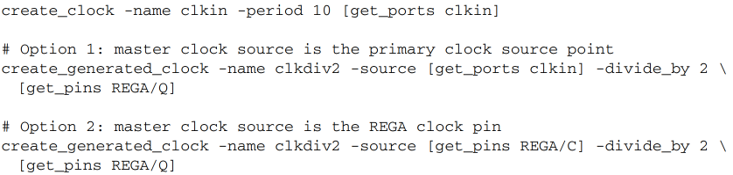

> 檢查源時鐘路徑和目的時鐘路徑所經(jīng)過的模塊是否相同,比如源時鐘路徑上經(jīng)過全局緩沖,PMMCM,但是目的時鐘路徑上只經(jīng)過了全局緩沖。如下圖所示,第一條路徑的源時鐘路徑上有BUFGCE/MMCM/BUFGCE,而目的時鐘路徑上只有BUFGCE,所以源時鐘路徑和目的時鐘路徑的延時不同,導(dǎo)致時鐘歪斜較大,應(yīng)該盡量避免此類路徑。第二條路徑的源時鐘和目的時鐘都是來源于MMCM的不同的時鐘,所以時鐘歪斜較小。

③Tsu/Tco大

當(dāng)設(shè)計中使用Block(DSP/Block RAM等)時,應(yīng)該要注意以下問題。對于以這些Block為時序路徑的起點或終點的時序路徑,這些Block的Tsu/Th/Tco都比普通的寄存器大,而且這些Block的布線延時和時鐘歪斜比較大。所以當(dāng)使用這些Block作為時序路徑的終點時,它的起點一定要是觸發(fā)器,比如說一個Block RAM的寫數(shù)據(jù)信號,輸入進Block前最好打一拍。當(dāng)使用這些Block作為時序路徑的起點時,應(yīng)該使用Block 內(nèi)部的輸出寄存器,比如使用由Block RAM組成的FIFO時,盡量不要使用首字置出的,而使用打一拍后輸出的,使用后者可以顯著降低Tco。當(dāng)時序路徑為從一個Block到另一個Block時,中間需要進行打拍操作。當(dāng)使用這些Block的控制端口時,應(yīng)該保證這些控制信號的低扇出,如使用由Block RAM組成的FIFO時,應(yīng)該盡量降低讀/寫能信/地址信號的扇出。

④Tlogic大

一般情況下,邏輯延時與時序路徑的邏輯層級數(shù)息息相關(guān),邏輯層級是指時序路徑的起點和終點之間組合邏輯單元(LUT)的個數(shù),而邏輯層級多一級意味著多1個LUT的延時加1條連接LUT的網(wǎng)線延時。通常一級邏輯層級的延時標(biāo)準(zhǔn)是1個LUT加1根網(wǎng)線的總延遲為0.5ns,如果某條路徑的邏輯級數(shù)大于時鐘周期/0.5ns,那么這條路徑就被稱為長路徑。

常用的處理長路徑的方案有兩種:

**> **修改rtl代碼,在長路徑的邏輯中插入流水線,將長路徑打破分為多條短路徑;

**> **使用綜合工具的retiming優(yōu)化方式,retiming實際上是寄存器重定向,原理是當(dāng)某條長路徑的相鄰路徑的建立時間裕量較大,那么它可以調(diào)整中間寄存器的位置,來調(diào)整布線延遲,通過適當(dāng)增加相鄰路徑的布線延遲而減少長路徑的布線延遲,使得那些時序違例較小的長路徑通過這種微調(diào)實現(xiàn)時序收斂。需要強調(diào)的是,這種方式優(yōu)化的力度非常有限,它只適合時序違例較小的長路徑,對于一些延時特別大的長路徑而言,也是無力回天。

⑤Tnet大

一般情況下,布線延遲與設(shè)計整體或局部模塊的資源利用率以及擁塞程度息息相關(guān)。

在正常情況下,一條網(wǎng)線的延時小于1ns,在發(fā)生擁塞的區(qū)域,網(wǎng)線的延時可能達(dá)到若干ns,導(dǎo)致布線延時顯著增加。為了解決布線延遲大,需要從降低資源利用率和降低擁塞程度下手,比如某個模塊使用了大量的寄存器堆,占用了大量的資源,此時應(yīng)該考慮使用Block RAM代替這些寄存器堆;某個模塊使用了大量的數(shù)據(jù)選擇器,此時應(yīng)該考慮如何優(yōu)化這些數(shù)據(jù)選擇器;某個模塊的控制信號扇出比較大,與其他模塊的互聯(lián)很重,此時應(yīng)該考慮如何降低這些信號的扇出;某條時序路徑的起點或終點是Block,由于Block的位置比較固定,所以Block的布線延遲會大一些。最后需要強調(diào)的是,一定要額外關(guān)注高扇出的網(wǎng)線也會對布線延時產(chǎn)生影響。

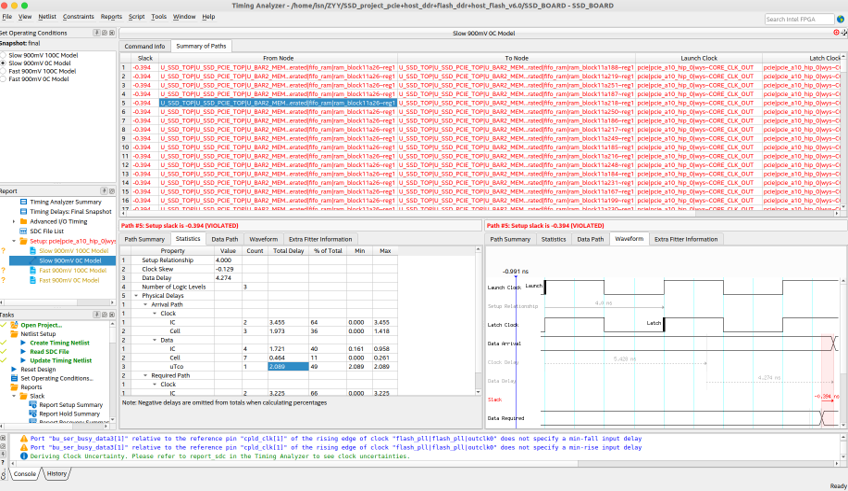

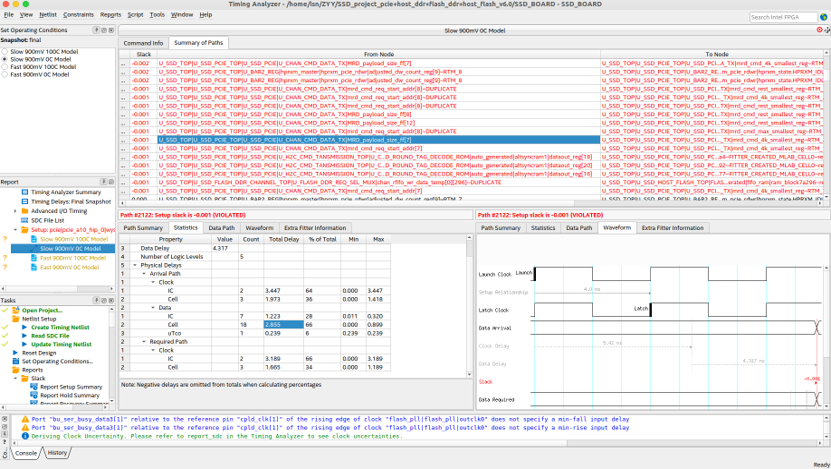

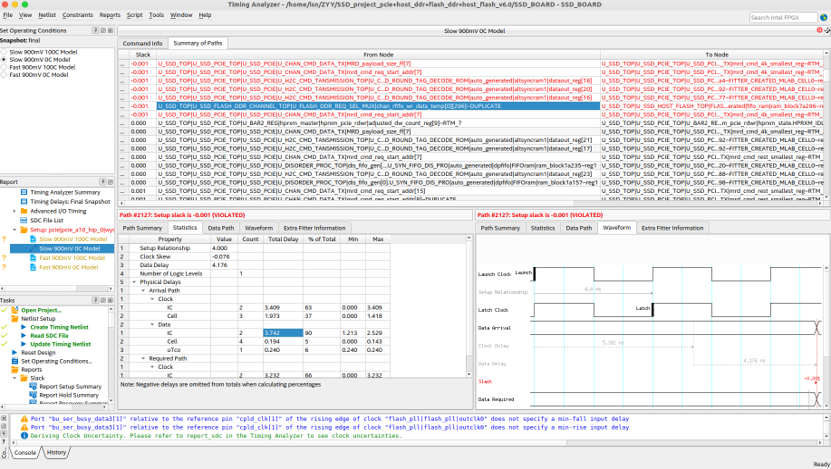

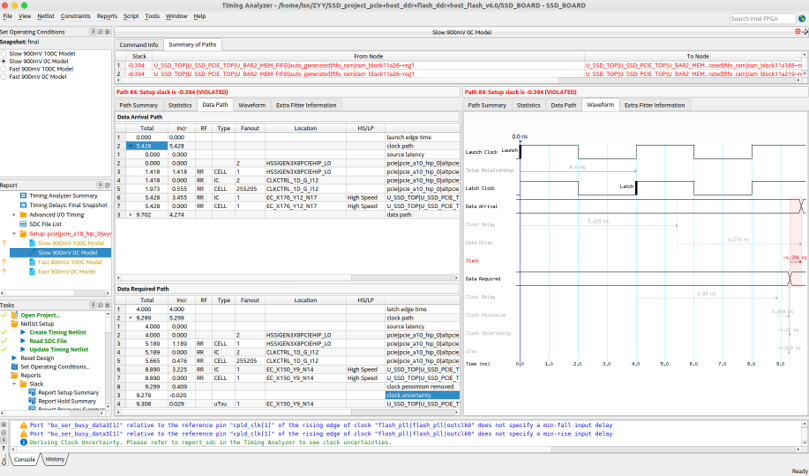

TimeQuest時序分析(Setup)

Holdup檢查

No.1

時序引擎如何進行Holdup檢查?

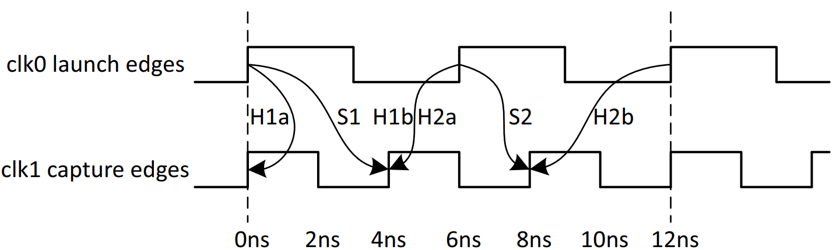

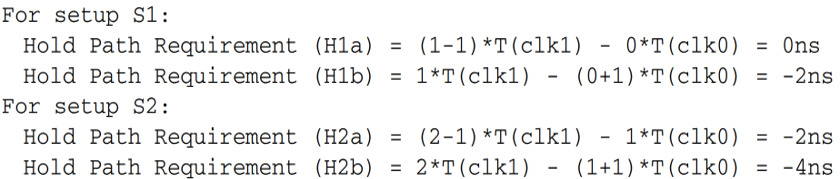

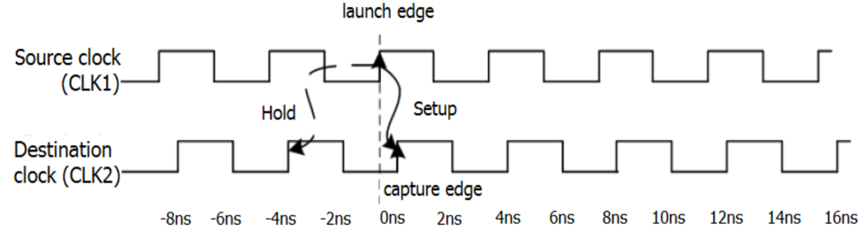

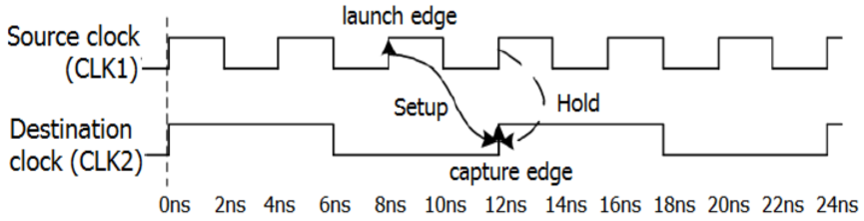

①確定保持時間要求 (確定發(fā)起時鐘沿和捕獲時鐘沿)

保持時間要求是以建立時間要求為基礎(chǔ)的,保持時間要求有兩種:

> 當(dāng)前建立時間的發(fā)起沿產(chǎn)生的數(shù)據(jù)不能被當(dāng)前建立時間的捕獲沿的前一個有效沿捕獲

> 當(dāng)前建立時間發(fā)起沿的下一個有效沿產(chǎn)生的數(shù)據(jù)不能被當(dāng)前建立時間的捕獲沿捕獲

根據(jù)所有的建立時間需求找到所有的保持時間需求,并從保持時間需求(可正可負(fù))中找到最大的保持時間需求。

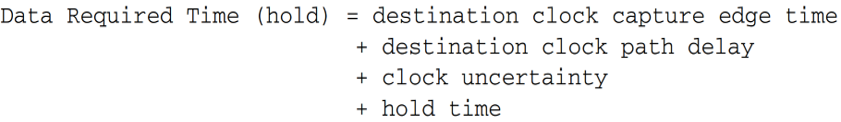

②計算數(shù)據(jù)的需求時間

③計算數(shù)據(jù)的到達(dá)時間

④計算Hold up的裕量(slack)

No.2

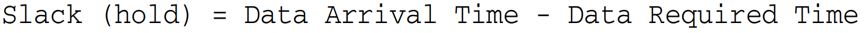

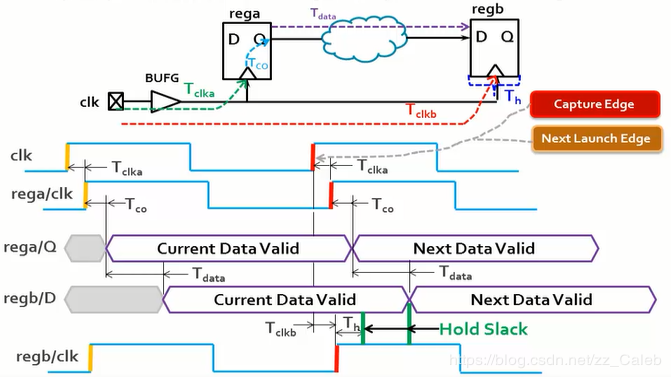

Holdup分析實例

> Data Arrival time(new data) = lauch edge + Tclka + Tco + Tdata(Tlogic+Tnet)

> Data Require time = capture edge + Tclkb + Th

**> **Hold up slack = Data Arrival time - Data Require time

No.3

根據(jù)公式分析哪些因素會導(dǎo)致Holdup Slack為負(fù)呢?

**> **Holdup Slack = (lauch edge - capture edge) + (Tclka – Tclkb) + Tco + Tdata(Tlogic+Tnet) -Th

> Holdup Slack = Tco + Tdata(Tlogic+Tnet) -Th - Holdup Requirement - clk skew

Hold up Slack為負(fù)的情況比較少見,當(dāng)Setup Slack有較大裕量時,通常工具會自動插入延時來增加Hold up Slack。

①保持時間需求大于0(通常由時序引擎選擇錯誤的捕獲沿導(dǎo)致)

②時鐘歪斜大于300ps(通常由時鐘路徑上的組合邏輯導(dǎo)致)

③Th過大(通常由時序路徑終點為Block導(dǎo)致)

TimeQuest時序分析(Holdup slack)

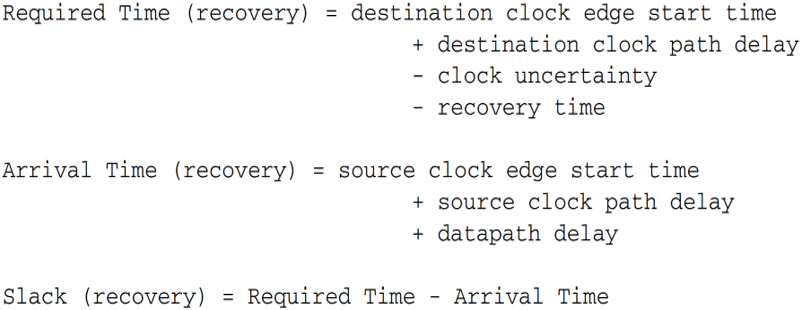

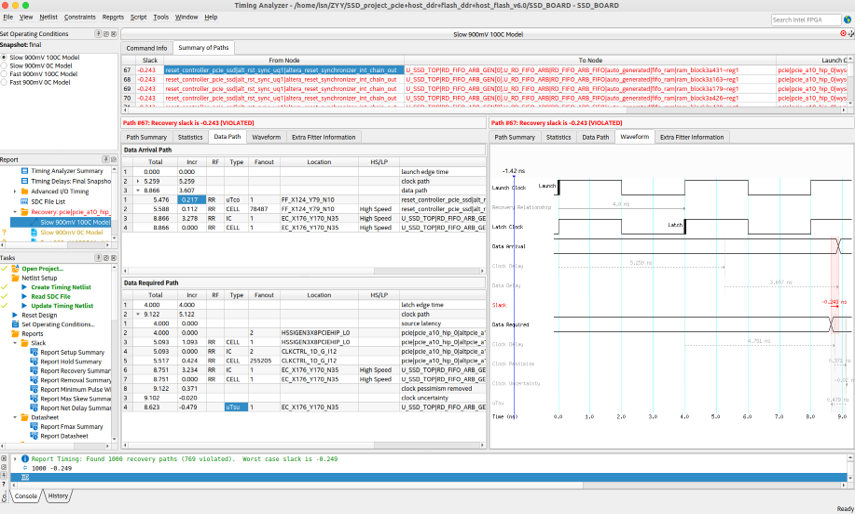

Recovery檢查

No.1

時序引擎如何進行Recovery檢查?

TimeQuest時序分析(Recovery)

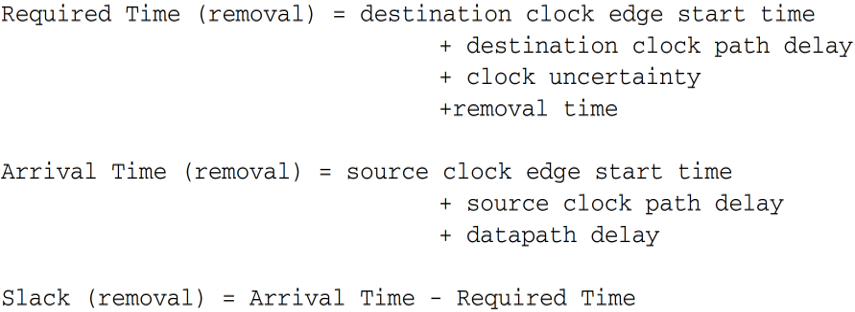

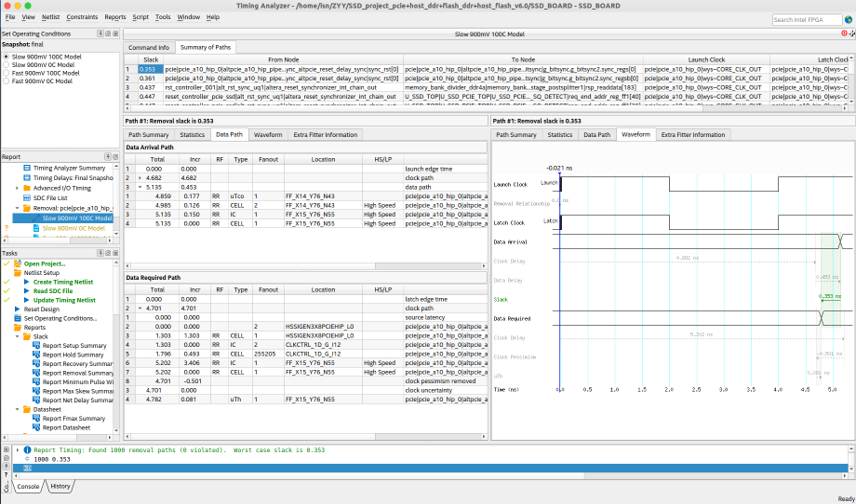

No.2

時序引擎如何進行Removal檢查?

TimeQuest時序分析(Removal)

時序約束

時序引擎能夠正確分析4種時序路徑的前提是,用戶已經(jīng)進行了正確的時序約束。時序約束本質(zhì)上就是告知時序引擎一些進行時序分析所必要的信息,這些信息只能由用戶主動告知,時序引擎對有些信息可以自動推斷,但是推斷得到的信息不一定正確。

**> **第一種路徑需要約束Input_delay;

**> **第二種路徑需要約束時鐘;

**> **第三種路徑需要約束output_delay;

> 第四種路徑需要約束Max_delay/Min_delay;

時鐘約束

No.1

時鐘約束類型

首先用戶必須要正確的約束時鐘,時序引擎才能根據(jù)時鐘信息進行各種時序檢查。

**用戶約束時鐘時,一般有兩種類型的時鐘需要約束。 **

> 主時鐘(Primary Clock)

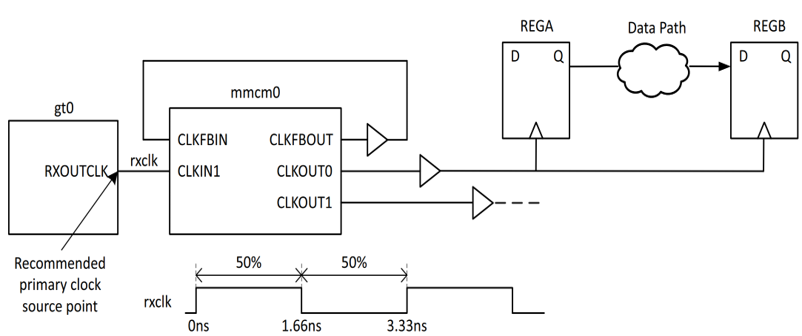

主時鐘(Primary Clock)有兩種類型:第一種是從FPGA的全局時鐘輸入引腳輸入的時鐘;第二種是從高速收發(fā)器輸出給用戶的恢復(fù)時鐘

> 生成時鐘(Generated Clock)

生成時鐘(Generated Clock)有兩種類型:第一種是由FPGA的專用時鐘管理模塊(PLL/MMCM)產(chǎn)生的時鐘(這種時鐘可以由時序引擎自動推斷出來);第二種是由用戶通過LUT或寄存器產(chǎn)生的時鐘(這種時鐘必須由用戶手動約束)。

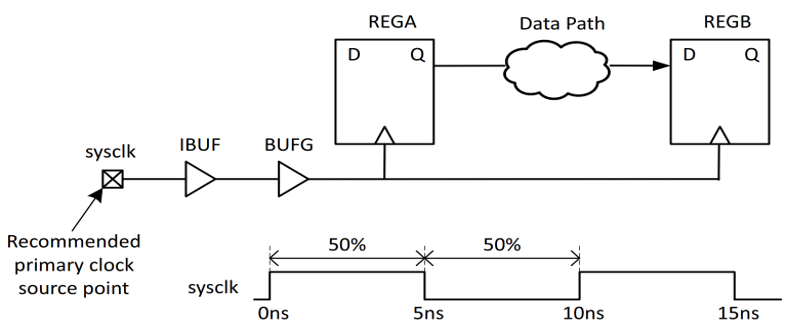

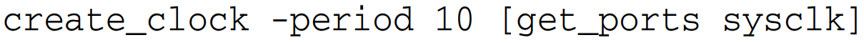

①主時鐘(Primary Clock)約束

使用Create_clock進行時序約束

> 第一種是從FPGA的全局時鐘輸入引腳輸入的時鐘:

全局時鐘輸入引腳是sysclk,時鐘周期10ns,占空比50%,相移0度。

全局時鐘輸入引腳是ClkIn,時鐘周期10ns,占空比25%,相移90度。

**> **第二種是從高速收發(fā)器輸出給用戶的恢復(fù)時鐘 全局時鐘輸入引腳是sysclk,時鐘周期3.3ns,占空比50%,相移0度。

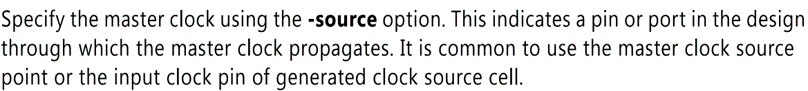

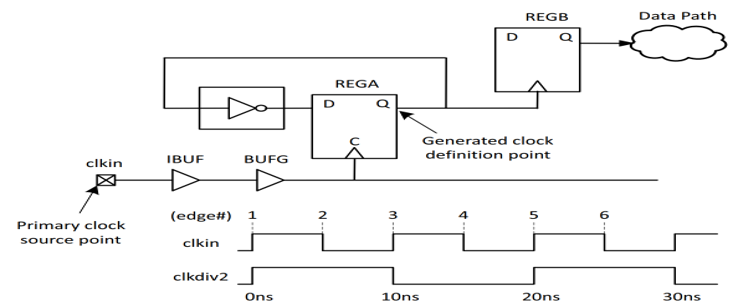

②生成時鐘(Generated Clock)約束

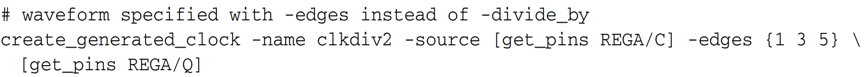

用Create_generated_clock進行時序約束

每個生成時鐘都會對應(yīng)一個時鐘源(Master_clk),這個時鐘源可以是Primary Clock或者另一個Generated Clock。

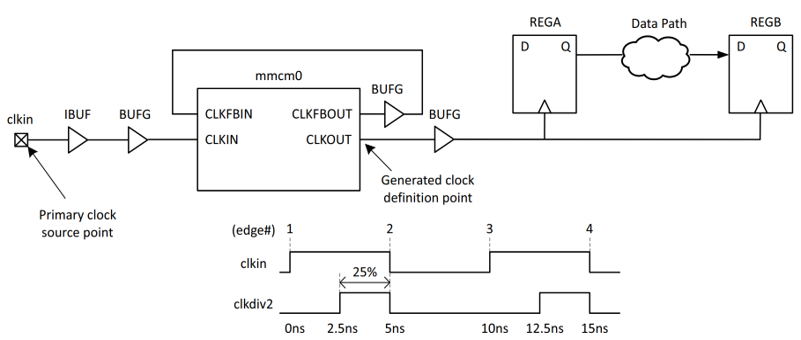

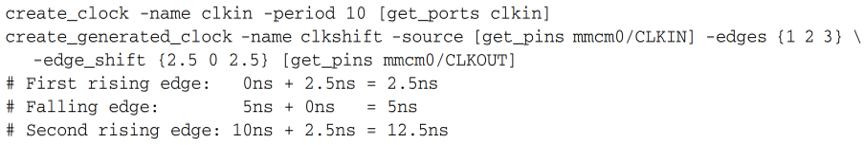

在約束生成時鐘時,用戶不需要描述生成時鐘的周期和波形,只需要描述由Master_clk經(jīng)過了怎樣的變化而產(chǎn)生的生成時鐘即可。比如經(jīng)過分頻(-devide_by),倍頻(-multiply_by),反相(-invert),相移(-edge_shift)等等操作。

當(dāng)生成時鐘需要進行相移時,使用-edge_shift選項。

-edge_shift不能與-divide_by/-multipl_by/-invert同時使用 。

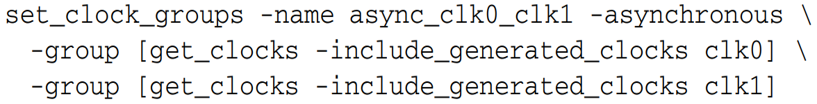

時序引擎默認(rèn)情況下會分析所有時鐘之間的時序路徑,用戶可以通過時鐘分組( set_clock_group)命令或偽路徑(set_false_path)命來關(guān)閉一部分路徑的時序分析。

**> **使用set_clock_group命令,時序引擎會將不同分組的時鐘之間的路徑分析關(guān)閉,相同分組的時鐘之間的路徑仍然存在。

> 使用set_false_path命令,時序引擎會忽略兩個時鐘的雙向路徑,被忽略的路徑不一定能夠正常工作,需要用戶確保該路徑使用了兩級觸發(fā)器同步或按照異步數(shù)據(jù)傳輸方式傳輸數(shù)據(jù)。用戶負(fù)責(zé)保證這些被忽略的路徑可以正常工作。

No.2

兩個時鐘的關(guān)系

**①同步時鐘(synchronous clock) **

兩個時鐘之間的相對相位關(guān)系是固定的(兩個時鐘來源于同一個Primary clock),并且這兩個時鐘的頻率的最小公共周期是個整數(shù)。

比如一個生成時鐘(200M)和該生成時鐘的Master_clk(100M)之間就屬于同步時鐘關(guān)系,因為這兩個時鐘的相位關(guān)系肯定是確定的,并且可以找到兩個時鐘的最小公共周期。通常情況下,一個Primary Clock和它產(chǎn)生的生成時鐘之間都屬于同步時鐘關(guān)系,除非找不到最小公共周期。屬于同步時鐘關(guān)系的兩個時鐘之間的路徑是可以進行時序分析的。

**②異步時鐘( asynchronous clock ) **

兩個時鐘之間的相對相位關(guān)系不確定。

比如FPGA上兩個晶振分別產(chǎn)生兩個Primary clock(相對相位關(guān)系不固定),這兩個Primary clock分別從FPGA的兩個全局時鐘引腳輸入給兩個MMCM,由兩個MMCM分別產(chǎn)生的生成時鐘之間屬于異步時鐘。一般情況下,不同的Primary clock之間都屬于異步時鐘,這些Primary clock分別產(chǎn)生的生成時鐘之間也屬于異步時鐘關(guān)系。

屬于異步時鐘關(guān)系的兩個時鐘之間的路徑無法進行正確的時序分析。

一般情況下,如果用戶不通過時鐘分組對時鐘之間的關(guān)系進行約束,時序引擎會默認(rèn)所有的時鐘之間都屬于同步時鐘關(guān)系。

③不可擴寬的時鐘(unexpandable clock)

對于這類時鐘,時序引擎無法在1000個時鐘周期內(nèi)找到兩個時鐘的公共周期,時序引擎就會從這1000個時鐘周期中找到建立時間需求最差的情況,并進行時序分析,然而它不一定FPGA實際允許過程中建立時間需求最差的情況,因為在1000個時鐘周期外可能還會有建立時間需求更差的情況,這樣一來,時序引擎的分析結(jié)果就無法保證該路徑一定不會出現(xiàn)問題,所以時序引擎的分析結(jié)果也就變的無意義。

比如說由同一個Primary Clock驅(qū)動的兩個MMCM的生成時鐘分別是clk0(5.125ns)和clk1(6.666ns),雖然它們的相對相位關(guān)系是固定的,但是時序引擎無法保證對兩個時鐘之間路徑的分析屬于最差情況,這種情況和異步時鐘之間的時序分析類似,時序分析的結(jié)果都看起來正常,但是這個結(jié)果確是不可信的。所以對這種時鐘的處理方式與處理異步時鐘是相同的,用戶都需要進行跨時鐘域的操作。

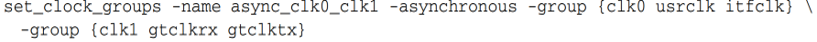

總結(jié):異步時鐘和不可擴展的時鐘之間的路徑都無法進行正確的時序分析,所以在時序分析之前,需要使用set_clock_group對時鐘進行分組,從而將這些無法進行正確時序分析的路徑忽略掉。

No.3

時鐘分組實例

> 第一個Primary clock clk0從FPGA的全局時鐘引腳進入了一個MMCM,MMCM生成了兩個生成時鐘userclk,itfclk

> 第二個Primary clock clk1是一個高速收發(fā)器輸出的恢復(fù)時鐘,將該恢復(fù)時鐘輸入進一個MMCM,MMCM生成了兩個生成時鐘gtxclkrx, gtxclktx

時鐘約束后時序引擎如何進行第二種路徑時序分析

時鐘約束后時序引擎如何進行第二種路徑時序分析

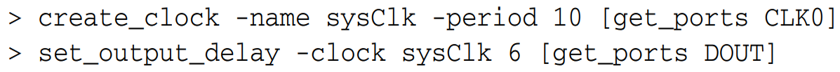

Input延時約束

Output延時約束

No.1

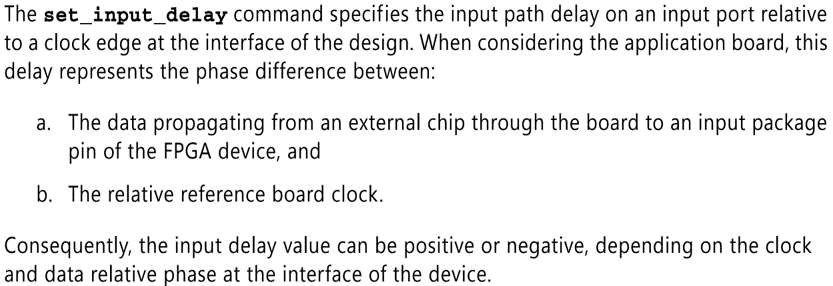

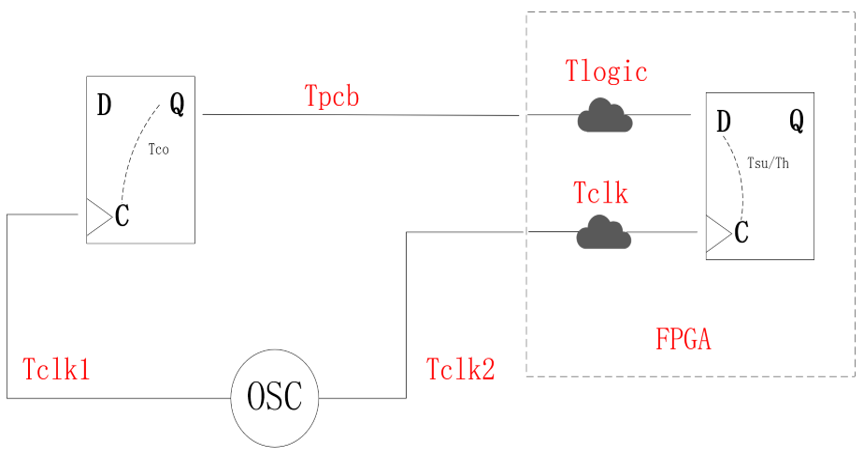

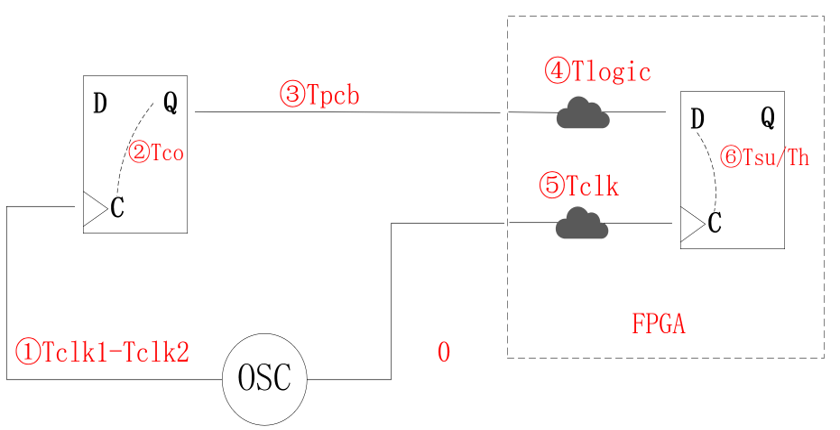

什么是Input delay?如何計算它?如何約束它?

Input delay概念

Input delay計算

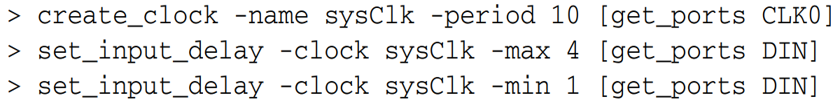

Max Input Delay = Tco(Max) + Tpcb(Max) - Clk skew(Min)

Min Input Delay = Tco(Min) + Tpcb(Min) - Clk skew(Max)

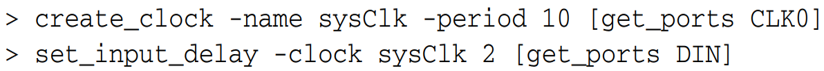

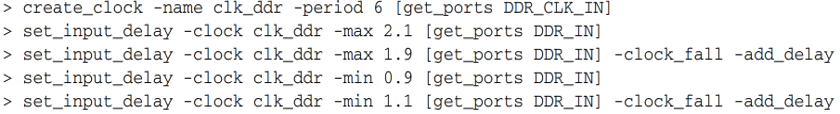

Input delay約束

No.2

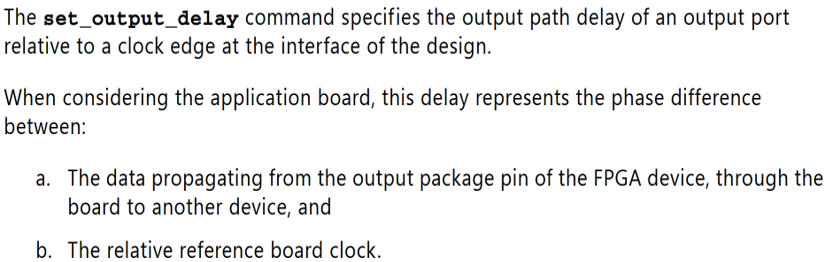

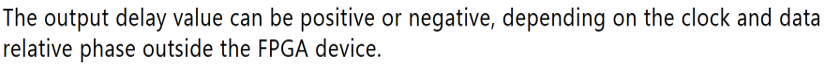

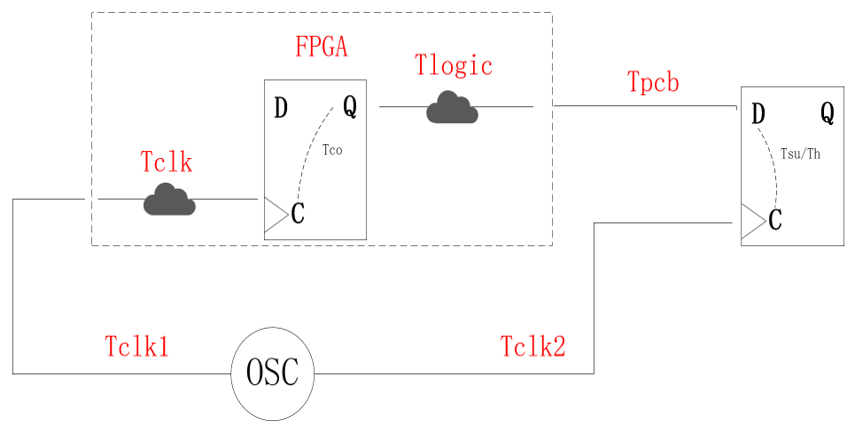

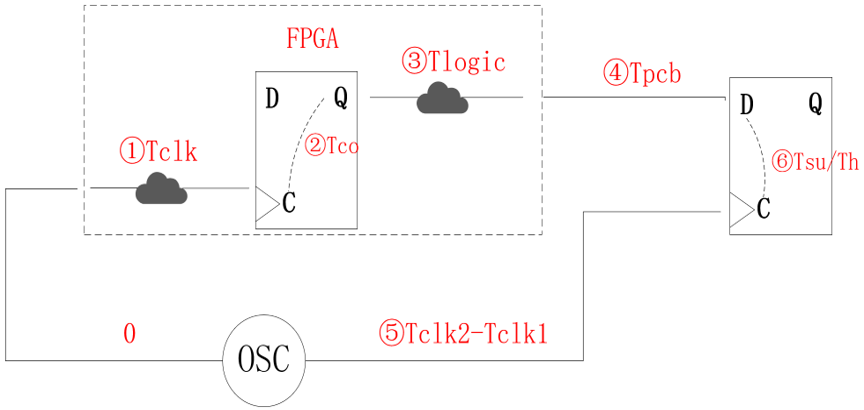

什么是Output delay?如何計算它?如何約束它?

Output delay概念

Output delay計算

Max Output Delay = Tpcb(Max) + Tsu - Clk skew(Min)

Min Output Delay = Tpcb(Min) - Th - Clk skew(Max)

Output delay約束

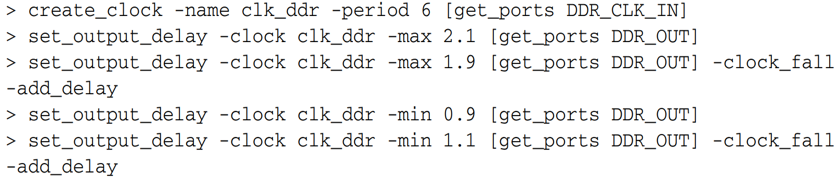

Multicycle約束

No.1

為什么要進行Multicycle約束?

時序引擎默認(rèn)情況下會在建立時間需求/保持時間需求最差的情況下進行時序分析,而時序引擎選擇的這種需求不一定是用戶真正希望的,而且時序引擎默認(rèn)選擇的這種需求是非常嚴(yán)苛的,甚至是根本無法滿足的。此時就需要用戶進行Multicycle約束,手動修改建立時間需求/保持時間需求。

用戶希望放松某些路徑的約束力度,就可以通過Multicycle約束調(diào)整建立時間需求/保持時間需求。

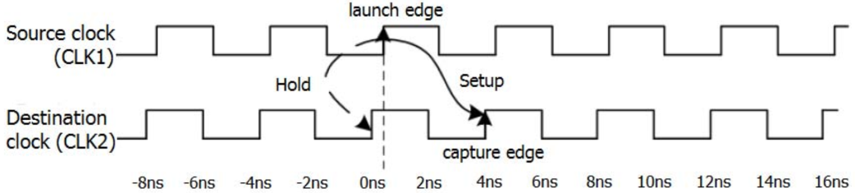

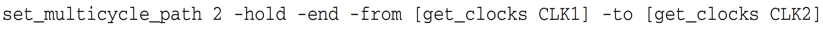

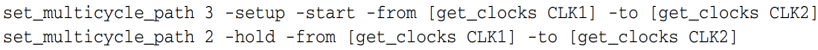

使用set_multicycle_path命令進行約束

No.2

如何進行正確Multicycle約束?

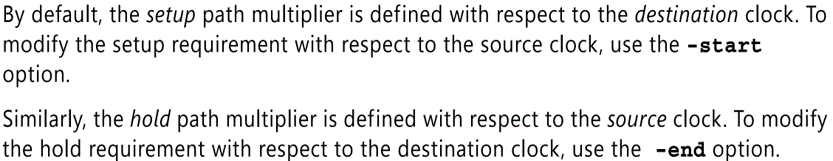

注:使用set_multicycle_path命令

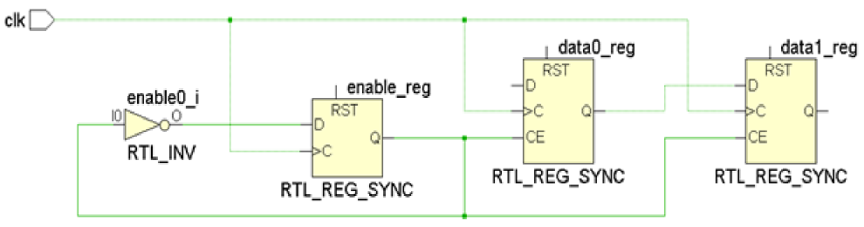

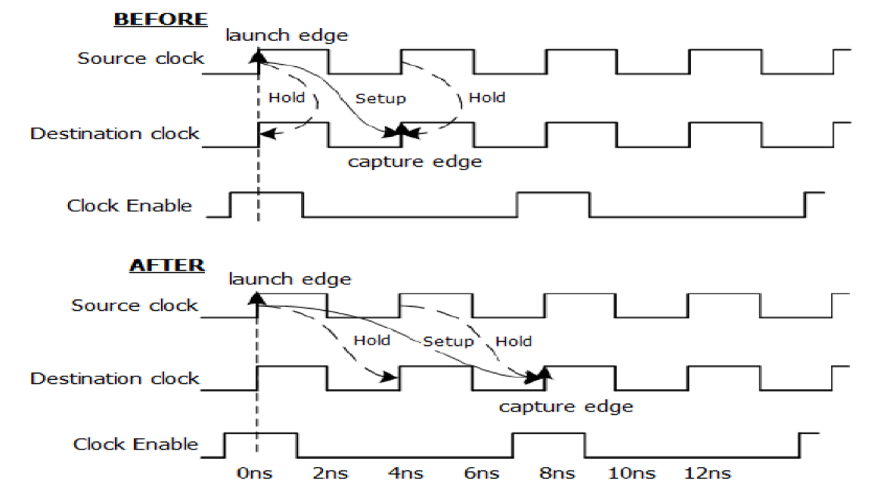

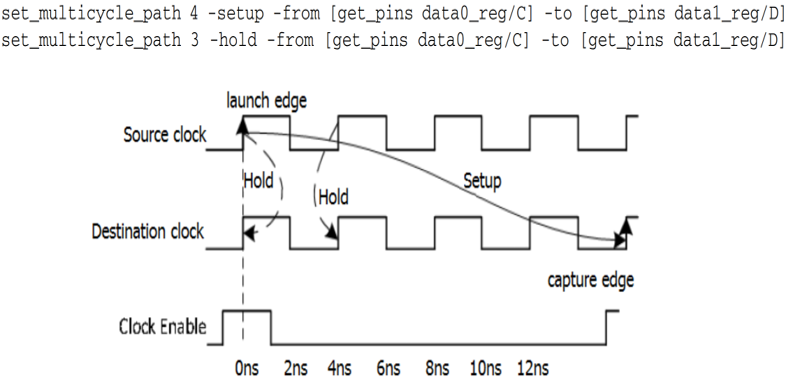

①在源時鐘和目的時鐘相同的情況下進行Multicycle約束

> 每兩個時鐘發(fā)起一次數(shù)據(jù),每兩個時鐘捕獲一次數(shù)據(jù)

> 每四個時鐘發(fā)起一次數(shù)據(jù),每四個時鐘捕獲一次數(shù)據(jù)

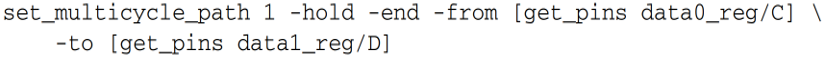

**> **只調(diào)整setup需求,Holdup需求會發(fā)生相應(yīng)的變化,但是變化結(jié)果是錯誤的

**> **進一步調(diào)整Holdup需求

**> **Set_multicycle_path 4 – hold –end –from [get_pins data0_reg/C] – to [get_pins data1_reg/C]

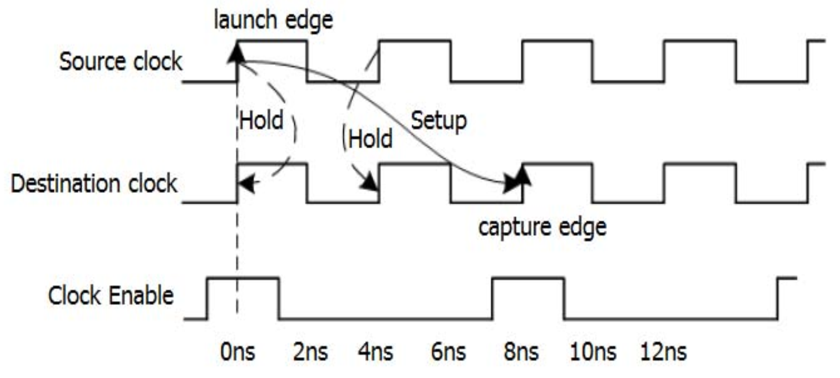

②在源時鐘和目的時鐘頻率相同且有正向偏移的情況下(正向偏移0.3ns)

先調(diào)整setup需求,holdup需求發(fā)生相應(yīng)的變化,變化的結(jié)果是正確的

③在源時鐘和目的時鐘頻率相同且有負(fù)向偏移的情況下(負(fù)向偏移0.3ns)發(fā)生負(fù)向偏移時,通常不需要進行Multicycle的約束,除非負(fù)向偏移過大

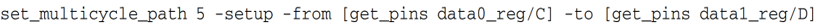

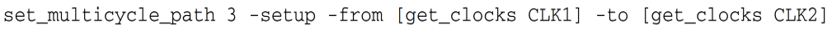

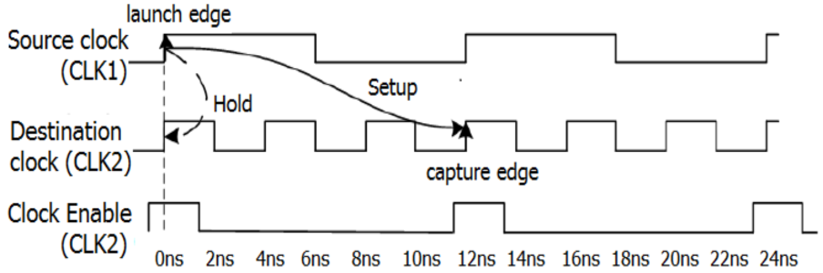

④在源時鐘和目的時鐘頻率不同的情況下(源時鐘慢,目的時鐘快)

調(diào)整setup需求(只能用-end,不能用-start ),Holdup需求發(fā)生相應(yīng)的變化,變化的結(jié)果是錯誤的。

進一步調(diào)整Holdup需求。(只能用-end,不能用-start)

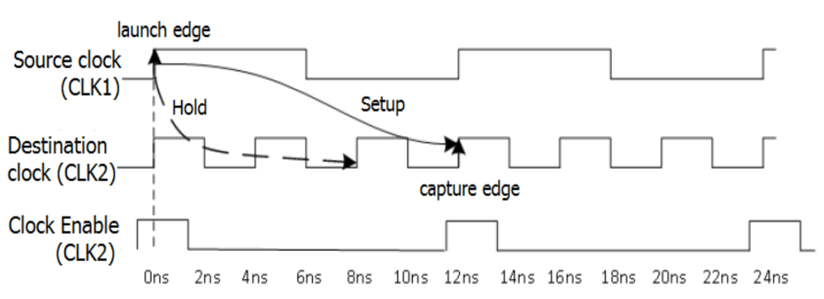

⑤在源時鐘和目的時鐘頻率不同的情況下(源時鐘快,目的時鐘慢)

同時調(diào)整setup需求(只能用-start,不能用-end)和Holdup需求(只能用-start,不能用-end)

Falsepath約束

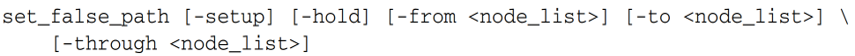

No.1

什么樣的路徑屬于FalsePath?

注:使用set_false_path命令

FalsePath路徑是指該路徑在拓?fù)浣Y(jié)構(gòu)中的確存在,但是滿足以下任一條件的路徑:

①在實際運行過程中,該路徑不工作。

②該路徑不需要進行時序分析。

比如:已經(jīng)做了兩級觸發(fā)器同步的跨時鐘域路徑

只在上電時工作一次的寄存器

異步復(fù)位路徑或用于測試的路徑

注意:如果用戶的目的只是放松某條路徑的時序約束,可以用set_multicycle_path命令進行約束,不要使用set_false_path。

設(shè)置FalsePath的好處:

①減小綜合/實現(xiàn)/時序分析的時間。

②極大的提升工具對設(shè)計的綜合/實現(xiàn)/優(yōu)化的結(jié)果。

-from/-to的node_list必須是有效的時序路徑的起點和終點,或是時鐘。-through的node_list可以是ports/pins

No.2

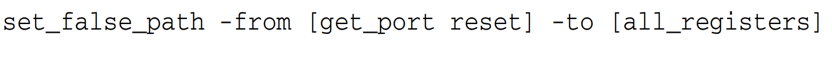

FalsePath約束舉例?

注:使用set_false_path命令

①將異步復(fù)位信號設(shè)置為偽路徑

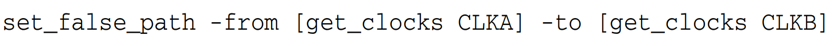

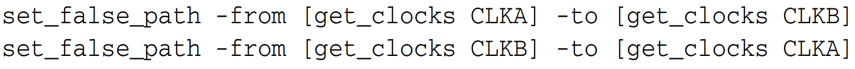

②將CLKA到CLKB的單向路徑設(shè)置為偽路徑

③將CLKA到CLKB以及CLKB到CLKA的雙向路徑設(shè)置為偽路徑

注:當(dāng)有多個異步時鐘之間的路徑需要設(shè)置為偽路徑時,推薦使用set_clock_group命令。

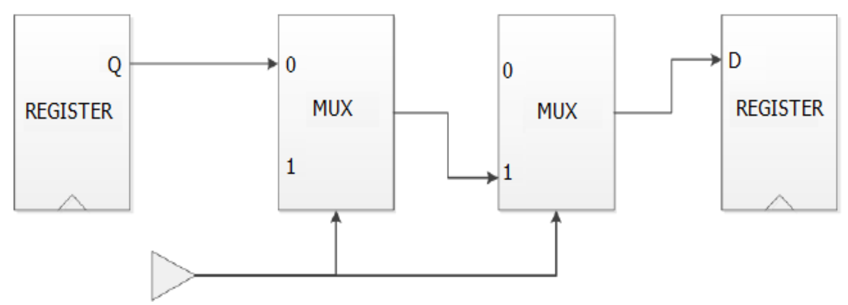

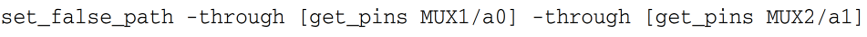

凡是經(jīng)過MUX1/a0,到MUX2/a1的時序路徑都會被忽略,采用-through的好處是不需要具體指定時序路徑的起點和終點,-through的順序需要注意,上述命令描述的是先經(jīng)過MUX1/a0,然后再經(jīng)過MUX2/a1。

電子發(fā)燒友App

電子發(fā)燒友App

評論