01

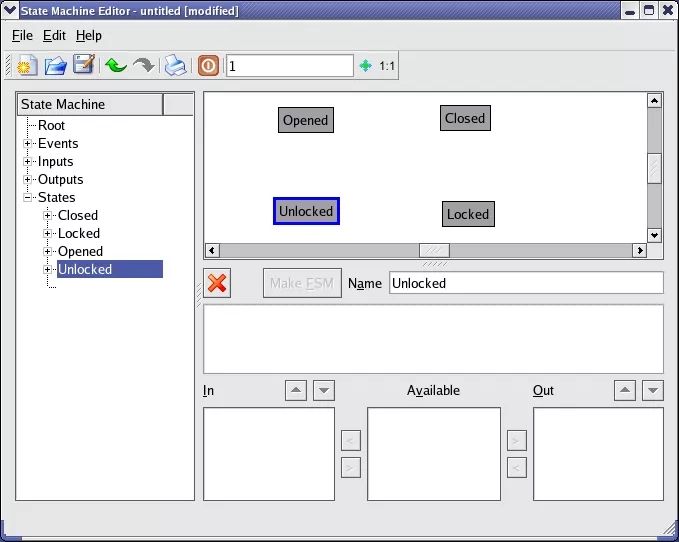

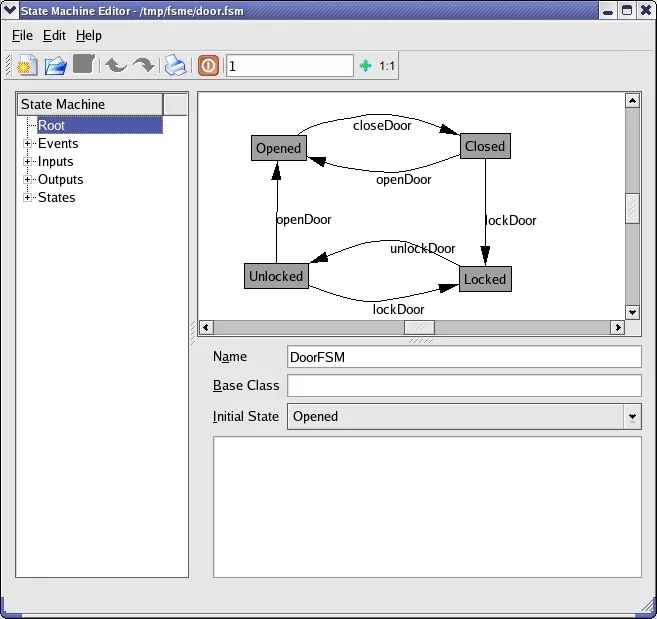

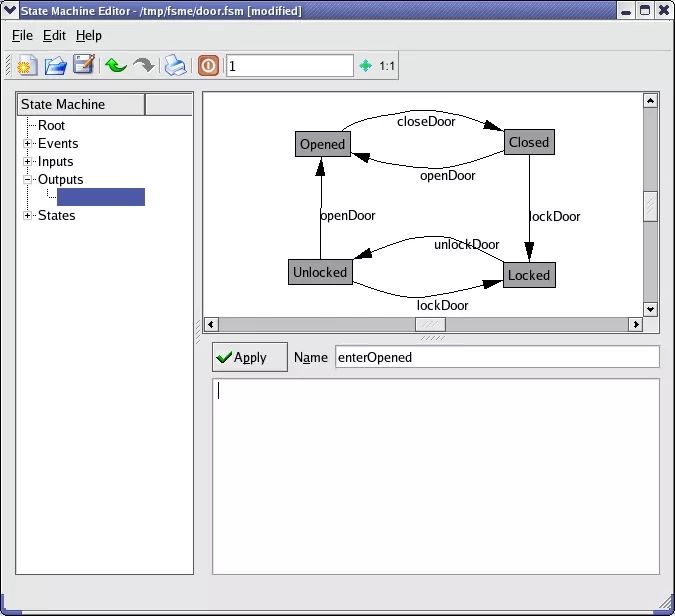

狀態(tài)機(jī)設(shè)計(jì)概述

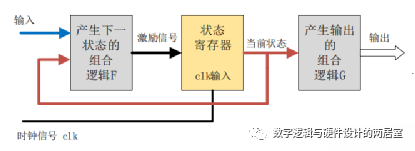

硬件電路設(shè)計(jì)通常以并行方式實(shí)現(xiàn),但是在實(shí)際工程中經(jīng)常會(huì)存在系統(tǒng)按照順序邏輯執(zhí)行的需求。如果希望分多個(gè)時(shí)間步驟完成一個(gè)任務(wù),同時(shí)減少使用大量使能信號(hào)銜接多個(gè)模塊造成的麻煩,就需要引出狀態(tài)機(jī)的概念。

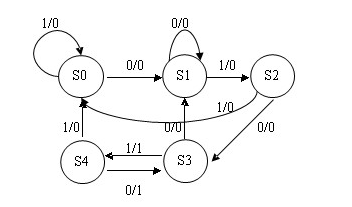

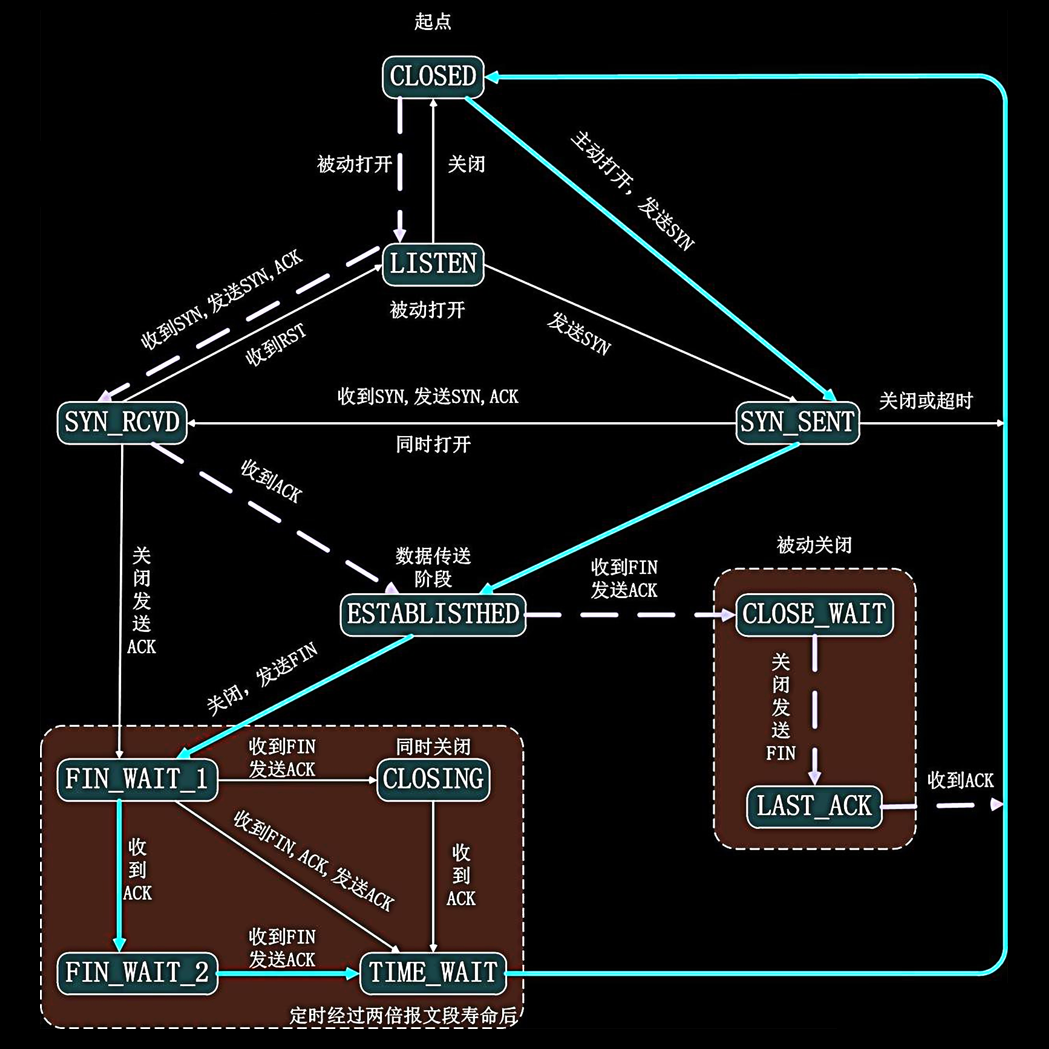

狀態(tài)機(jī)(State Machine)由輸入、輸出和狀態(tài)三要素構(gòu)成,輸入是指一些引發(fā)狀態(tài)變化的條件,輸出是指狀態(tài)改變后引起的變化,狀態(tài)是指順序邏輯執(zhí)行的步驟,通常利用一些邏輯值進(jìn)行表示。

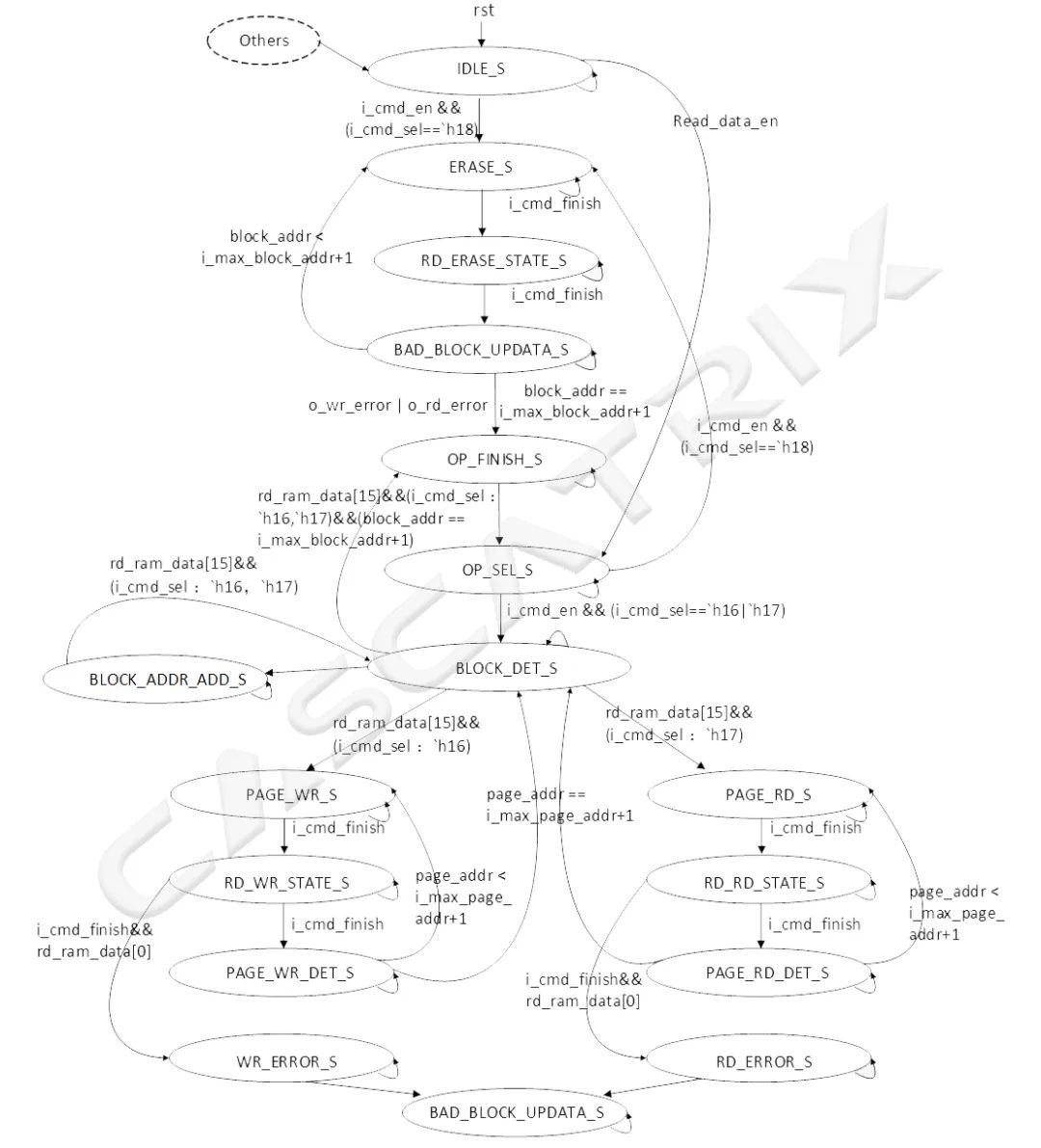

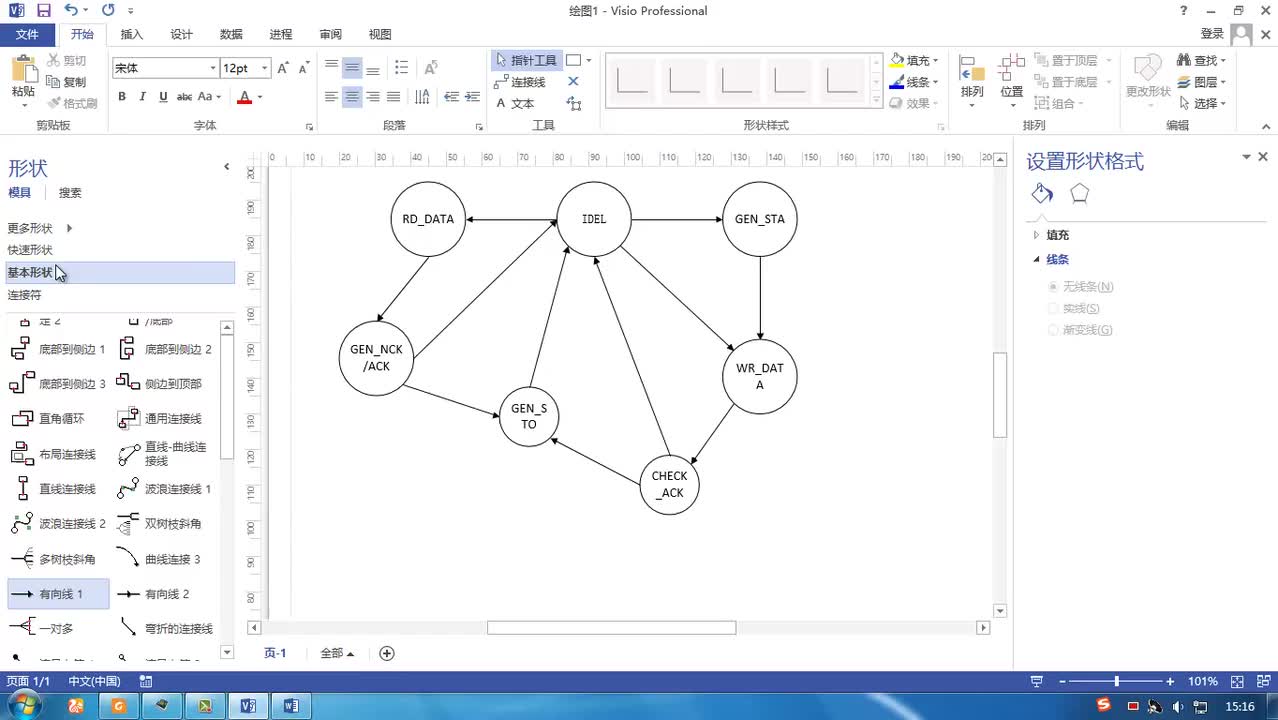

以NAND FALSH控制過(guò)程的狀態(tài)機(jī)為例,NAND FALSH操作通常需要按順序依次執(zhí)行擦除、壞塊檢測(cè)和讀寫(xiě)操作:NAND FLASH在系統(tǒng)復(fù)位信號(hào)rst = 1后進(jìn)入空閑狀態(tài)IDLE;當(dāng)指令使能信號(hào)i_cmd_en = 1且指令選擇信號(hào)i_cmd_sel = h18時(shí),NAND FLASH 進(jìn)入擦除狀態(tài)ERASE;當(dāng)指令結(jié)束信號(hào)i_cmd_finish = 1時(shí),NAND FLASH進(jìn)入擦除狀態(tài)讀取狀態(tài)......NAND FLASH根據(jù)不同的輸入條件和當(dāng)前狀態(tài)實(shí)現(xiàn)狀態(tài)跳轉(zhuǎn),通過(guò)在不同狀態(tài)實(shí)現(xiàn)不同功能,完成NAND FLASH讀寫(xiě)等操作。

狀態(tài)機(jī)設(shè)計(jì)按照不同的標(biāo)準(zhǔn)分類(lèi):

1. 輸出與輸入是否相關(guān):

Moore型狀態(tài)機(jī):輸出只與狀態(tài)相關(guān),與輸入無(wú)關(guān);

Mealy型狀態(tài)機(jī):輸出與狀態(tài)和輸入都相關(guān)。

2. 狀態(tài)轉(zhuǎn)移與輸出是否依賴(lài)時(shí)鐘信號(hào):

同步狀態(tài)機(jī):狀態(tài)轉(zhuǎn)移和輸出都發(fā)生在時(shí)鐘沿;

異步狀態(tài)機(jī):狀態(tài)轉(zhuǎn)移和輸出不依賴(lài)時(shí)鐘信號(hào),而是依賴(lài)于輸入信號(hào)的變化。

3. 輸出與狀態(tài)是否相關(guān):

順序邏輯狀態(tài)機(jī):輸出與輸入和狀態(tài)都相關(guān),當(dāng)前時(shí)刻的輸出會(huì)影響下一個(gè)時(shí)刻的狀態(tài);

組合邏輯狀態(tài)機(jī):輸出只與輸入相關(guān),與狀態(tài)無(wú)關(guān),當(dāng)前時(shí)刻的輸出不會(huì)影響下一個(gè)時(shí)刻的狀態(tài)。

4. 狀態(tài)數(shù)目是否有限:

有限狀態(tài)機(jī):狀態(tài)數(shù)目是有限的,可以用狀態(tài)轉(zhuǎn)移圖來(lái)表示狀態(tài)和狀態(tài)之間的轉(zhuǎn)移關(guān)系;

無(wú)限狀態(tài)機(jī):狀態(tài)數(shù)目是無(wú)限的,一般用差分方程或狀態(tài)轉(zhuǎn)移函數(shù)來(lái)表示狀態(tài)轉(zhuǎn)移關(guān)系。

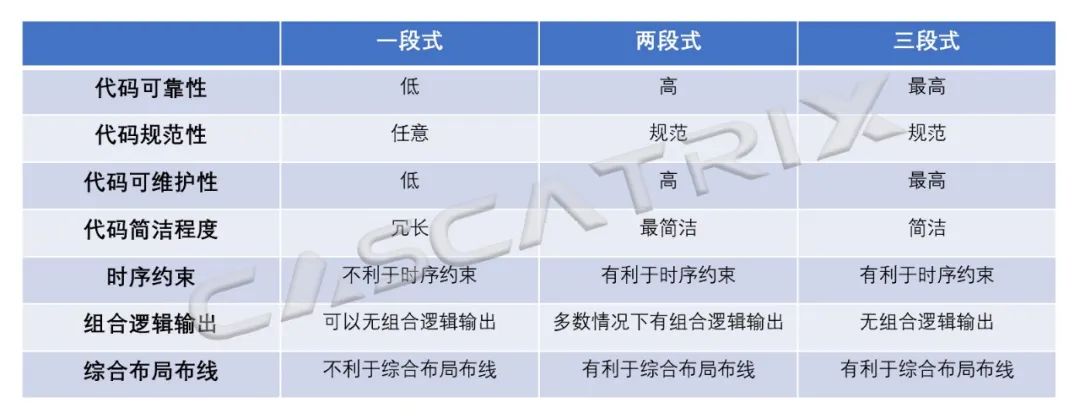

在FPGA設(shè)計(jì)過(guò)程中,通常考慮的狀態(tài)機(jī)是有限狀態(tài)機(jī)(FSM, Finite State Machine)。FPGA有限狀態(tài)機(jī)根據(jù)寫(xiě)法不同可以分為一段式、兩段式和三段式,不同狀態(tài)機(jī)寫(xiě)法在代碼可讀性和速度面積平衡性方面有所優(yōu)劣,本文將以不同寫(xiě)法下?tīng)顟B(tài)機(jī)的Verilog代碼為例,對(duì)三種狀態(tài)機(jī)寫(xiě)法的效果進(jìn)行對(duì)比分析。

02

一段式狀態(tài)機(jī)設(shè)計(jì)分析

一段式狀態(tài)機(jī)將狀態(tài)機(jī)的三要素(輸入、輸出和狀態(tài))邏輯實(shí)現(xiàn)在同一個(gè)always內(nèi),示例代碼如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Cascatrix

// Engineer: Carson

//?

// Create Date: 2023/07/16

// Design Name: FSM

// Module Name: FSM

// Tool Versions: v1.0

// Description: Finite State Machine?

//////////////////////////////////////////////////////////////////////////////////

module FSM(

? ? clk,

? ? rst_n,

? ? condition1,

? ? condition2,

? ? result

? ? );

? ? input? ? ? ? ? ?clk;

? ? input? ? ? ? ? ?rst_n;

? ? input? ? ? ? ? ?condition1;

? ? input? ? ? ? ? ?condition2;

? ? output? [3:0]? ?result;

? ? wire? ? ? ? ? ? clk;

? ? wire? ? ? ? ? ? rst_n;

? ? wire? ? ? ? ? ? condition1;

? ? wire? ? ? ? ? ? condition2;

? ? reg? ? ?[3:0]? ?result;

? ? parameter IDLE = 1;

? ? parameter STATE_S11 = 2;

? ? parameter STATE_S12 = 3;

? ? parameter STATE_S21 = 4;

? ? parameter STATE_S22 = 4;

? ? reg [3:0] current_state;? ?

? ? always@(posedge clk or negedge rst_n)

? ? begin

? ? ? ? if(!rst_n)

? ? ? ? begin

? ? ? ? ? ? current_state <= IDLE;

? ? ? ? ? ? result <= 4'b0101;

? ? ? ? end

? ? ? ? else

? ? ? ? begin

? ? ? ? ? ? case(current_state)

? ? ? ? ? ? IDLE:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? if(condition1)

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? current_state <= STATE_S11;

? ? ? ? ? ? ? ? ? ? result <= 4'b1110;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? ? else if(condition2)

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? current_state <= STATE_S21;

? ? ? ? ? ? ? ? ? ? result <= 4'b1111;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? ? else

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? current_state <= IDLE;

? ? ? ? ? ? ? ? ? ? result <= 4'b0101;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S11:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? current_state <= STATE_S12;

? ? ? ? ? ? ? ? result <= 4'b0010;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S12:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? current_state <= IDLE;

? ? ? ? ? ? ? ? result <= 4'b0101;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S21:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? current_state <= STATE_S22;

? ? ? ? ? ? ? ? result <= 4'b1000;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S22:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? current_state <= IDLE;

? ? ? ? ? ? ? ? result <= 4'b0101;

? ? ? ? ? ? end

? ? ? ? ? ? default:current_state <= IDLE;

? ? ? ? ? ? endcase

? ? ? ? end

? ? end

endmodule

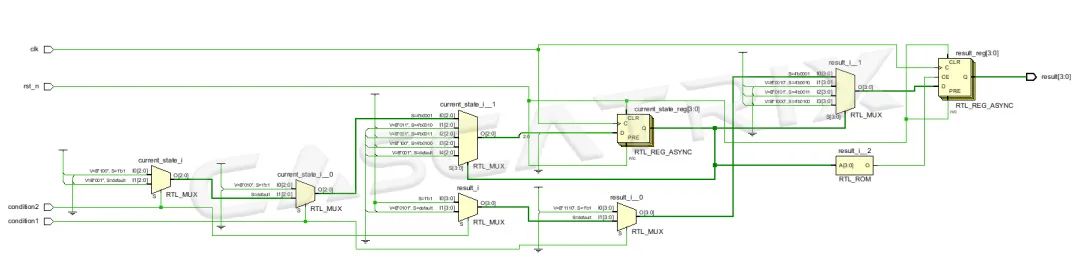

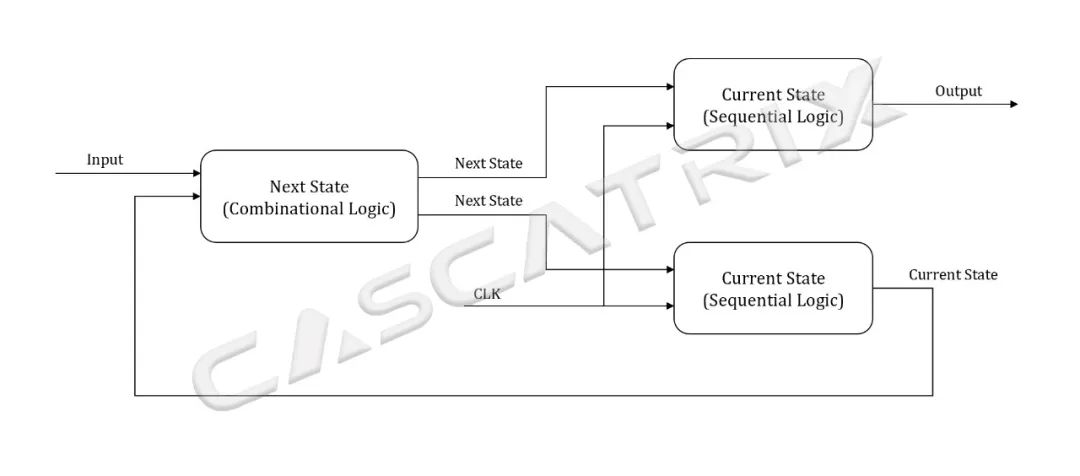

上述代碼所實(shí)現(xiàn)的一段式狀態(tài)機(jī)RTL視圖如下:?

通過(guò)分析一段式狀態(tài)機(jī)代碼可以發(fā)現(xiàn),狀態(tài)current_state、輸入condition1/2和輸出result在同一個(gè)always內(nèi),整體而言代碼編寫(xiě)較為簡(jiǎn)單。然而,從代碼可讀性和可維護(hù)性的角度而言,一段式狀態(tài)機(jī)的這種代碼格式并不利于后期的閱讀與維護(hù),當(dāng)狀態(tài)機(jī)較為復(fù)雜時(shí),一段式狀態(tài)機(jī)更容易出現(xiàn)錯(cuò)誤。

03

兩段式狀態(tài)機(jī)設(shè)計(jì)分析

兩段式狀態(tài)機(jī)將狀態(tài)機(jī)的時(shí)序邏輯和組合邏輯劃分為兩個(gè)always,時(shí)序邏輯內(nèi)進(jìn)行當(dāng)前狀態(tài)和下一狀態(tài)的切換,組合邏輯里實(shí)現(xiàn)各個(gè)輸入、輸出和狀態(tài)的判斷,示例代碼如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Cascatrix

// Engineer: Carson

//?

// Create Date: 2023/07/16

// Design Name: FSM

// Module Name: FSM

// Tool Versions: v1.0

// Description: Finite State Machine?

//////////////////////////////////////////////////////////////////////////////////

module FSM(

? ? clk,

? ? rst_n,

? ? condition1,

? ? condition2,

? ? result

? ? );

? ? input? ? ? ? ? ?clk;

? ? input? ? ? ? ? ?rst_n;

? ? input? ? ? ? ? ?condition1;

? ? input? ? ? ? ? ?condition2;

? ? output? [3:0]? ?result;

? ? wire? ? ? ? ? ? clk;

? ? wire? ? ? ? ? ? rst_n;

? ? wire? ? ? ? ? ? condition1;

? ? wire? ? ? ? ? ? condition2;

? ? reg? ? ?[3:0]? ?result;

? ? parameter IDLE = 1;

? ? parameter STATE_S11 = 2;

? ? parameter STATE_S12 = 3;

? ? parameter STATE_S21 = 4;

? ? parameter STATE_S22 = 4;

? ? reg [3:0] next_state;? ?

? ? reg [3:0] current_state;? ?

? ? always@(posedge clk or negedge rst_n)

? ? begin

? ? ? ? if(!rst_n)

? ? ? ? ? ? current_state <= IDLE;

? ? ? ? else

? ? ? ? ? ? current_state <= next_state;

? ? end

? ? always@(current_state or condition1 or condition2)

? ? begin

? ? ? ? if(!rst_n)

? ? ? ? begin

? ? ? ? ? ? next_state = IDLE;

? ? ? ? ? ? result = 4'b0101;

? ? ? ? end

? ? ? ? else

? ? ? ? begin

? ? ? ? ? ? case(next_state)

? ? ? ? ? ? IDLE:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? if(condition1)

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? next_state = STATE_S11;

? ? ? ? ? ? ? ? ? ? result = 4'b1110;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? ? else if(condition2)

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? next_state = STATE_S21;

? ? ? ? ? ? ? ? ? ? result = 4'b1111;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? ? ? else

? ? ? ? ? ? ? ? begin

? ? ? ? ? ? ? ? ? ? next_state = IDLE;

? ? ? ? ? ? ? ? ? ? result = 4'b0101;

? ? ? ? ? ? ? ? end

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S11:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? next_state = STATE_S12;

? ? ? ? ? ? ? ? result = 4'b0010;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S12:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? next_state = IDLE;

? ? ? ? ? ? ? ? result = 4'b0101;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S21:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? next_state = STATE_S22;

? ? ? ? ? ? ? ? result = 4'b1000;

? ? ? ? ? ? end

? ? ? ? ? ? STATE_S22:

? ? ? ? ? ? begin

? ? ? ? ? ? ? ? next_state = IDLE;

? ? ? ? ? ? ? ? result = 4'b0101;

? ? ? ? ? ? end

? ? ? ? ? ? default:next_state = IDLE;

? ? ? ? ? ? endcase

? ? ? ? end

? ? end

endmodule

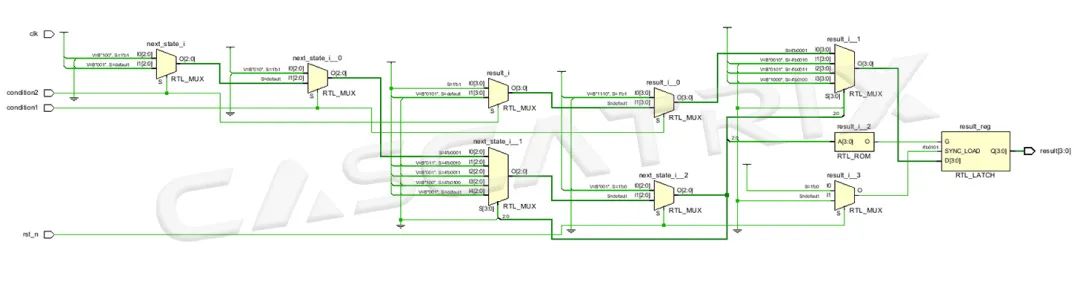

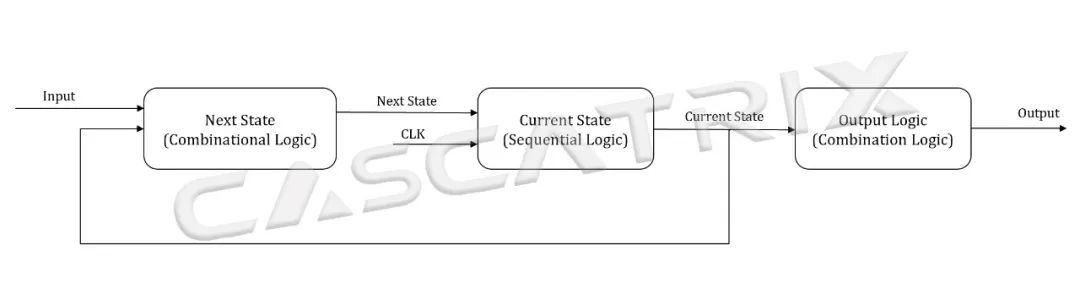

上述代碼所實(shí)現(xiàn)的兩段式狀態(tài)機(jī)RTL視圖如下:?

相比于一段式狀態(tài)機(jī),兩段式狀態(tài)機(jī)通過(guò)劃分組合邏輯和時(shí)序邏輯提高代碼的可讀性和可維護(hù)性,對(duì)組合邏輯內(nèi)容更改即可提高。然而,兩段式狀態(tài)機(jī)的組合邏輯輸出在同一個(gè)模塊中可能會(huì)出現(xiàn)競(jìng)爭(zhēng)冒險(xiǎn),因此較為容易出現(xiàn)毛刺等問(wèn)題。

04

三段式狀態(tài)機(jī)設(shè)計(jì)分析

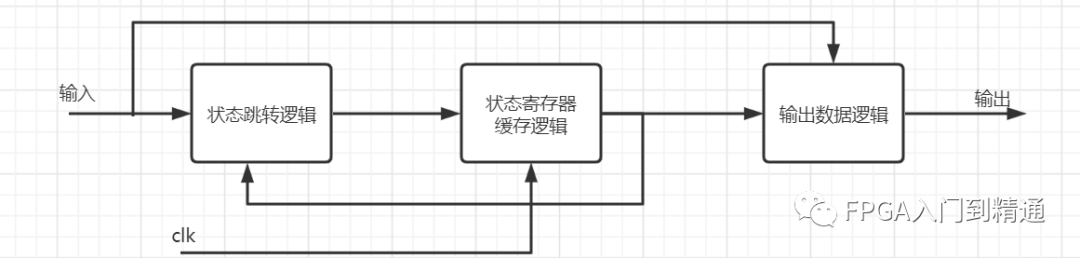

三段式狀態(tài)機(jī)將兩段式狀態(tài)機(jī)組合邏輯的狀態(tài)和輸出劃分為兩部分,狀態(tài)轉(zhuǎn)換使用組合邏輯、邏輯輸出使用時(shí)序邏輯,示例代碼如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Cascatrix

// Engineer: Carson

//?

// Create Date: 2023/07/16

// Design Name: FSM

// Module Name: FSM

// Tool Versions: v1.0

// Description: Finite State Machine?

//////////////////////////////////////////////////////////////////////////////////

module FSM(

? ? clk,

? ? rst_n,

? ? condition1,

? ? condition2,

? ? result

? ? );

? ? input? ? ? ? ? ?clk;

? ? input? ? ? ? ? ?rst_n;

? ? input? ? ? ? ? ?condition1;

? ? input? ? ? ? ? ?condition2;

? ? output? [3:0]? ?result;

? ? wire? ? ? ? ? ? clk;

? ? wire? ? ? ? ? ? rst_n;

? ? wire? ? ? ? ? ? condition1;

? ? wire? ? ? ? ? ? condition2;

? ? reg? ? ?[3:0]? ?result;

? ? parameter IDLE = 1;

? ? parameter STATE_S11 = 2;

? ? parameter STATE_S12 = 3;

? ? parameter STATE_S21 = 4;

? ? parameter STATE_S22 = 4;

? ? reg [3:0] next_state;? ?

? ? reg [3:0] current_state;? ?

? ? always@(posedge clk or negedge rst_n)

? ? begin

? ? ? ? if(!rst_n)

? ? ? ? ? ? current_state <= IDLE;

? ? ? ? else

? ? ? ? ? ? current_state <= next_state;

? ? end

? ? always@(current_state or condition1 or condition2)

? ? begin

? ? ? ? case(current_state)

? ? ? ? IDLE:

? ? ? ? begin

? ? ? ? ? ? if(condition1)

? ? ? ? ? ? ? ? next_state = STATE_S11;

? ? ? ? ? ? else if(condition2)

? ? ? ? ? ? ? ? next_state = STATE_S21;

? ? ? ? ? ? else

? ? ? ? ? ? ? ? next_state = IDLE;

? ? ? ? end

? ? ? ? STATE_S11: next_state = STATE_S12;

? ? ? ? STATE_S12: next_state = IDLE;

? ? ? ? STATE_S21: next_state = STATE_S22;

? ? ? ? STATE_S22: next_state = IDLE;

? ? ? ? default:next_state = IDLE;

? ? ? ? endcase

? ? end

? ? always@(posedge clk or negedge rst_n)

? ? begin

? ? ? ? if(!rst_n)

? ? ? ? ? ? result <= 4'b0101;

? ? ? ? else

? ? ? ? case(current_state)

? ? ? ? IDLE:

? ? ? ? begin

? ? ? ? ? ? if(condition1)

? ? ? ? ? ? ? ? result <= 4'b1110;

? ? ? ? ? ? else if(condition2)

? ? ? ? ? ? ? ? result <= 4'b1111;

? ? ? ? ? ? else

? ? ? ? ? ? ? ? result <= 4'b0101;

? ? ? ? end

? ? ? ? STATE_S11: result <= 4'b0010;

? ? ? ? STATE_S12: result <= 4'b0101;

? ? ? ? STATE_S21: result <= 4'b1000;

? ? ? ? STATE_S22: result <= 4'b0101;

? ? ? ? default:result <= 4'b0101;

? ? ? ? endcase

? ? end

endmodule

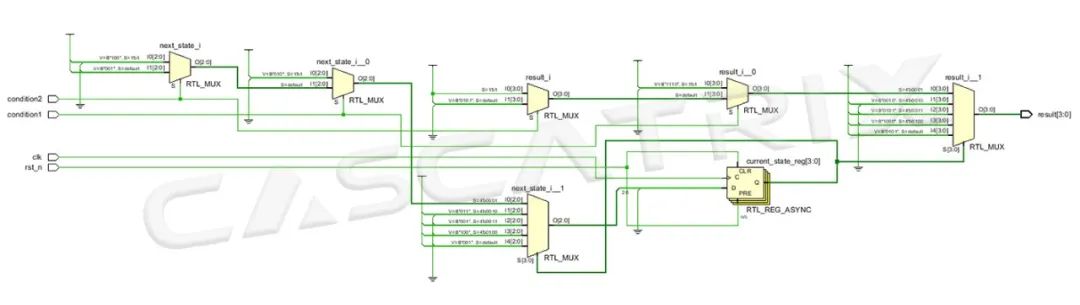

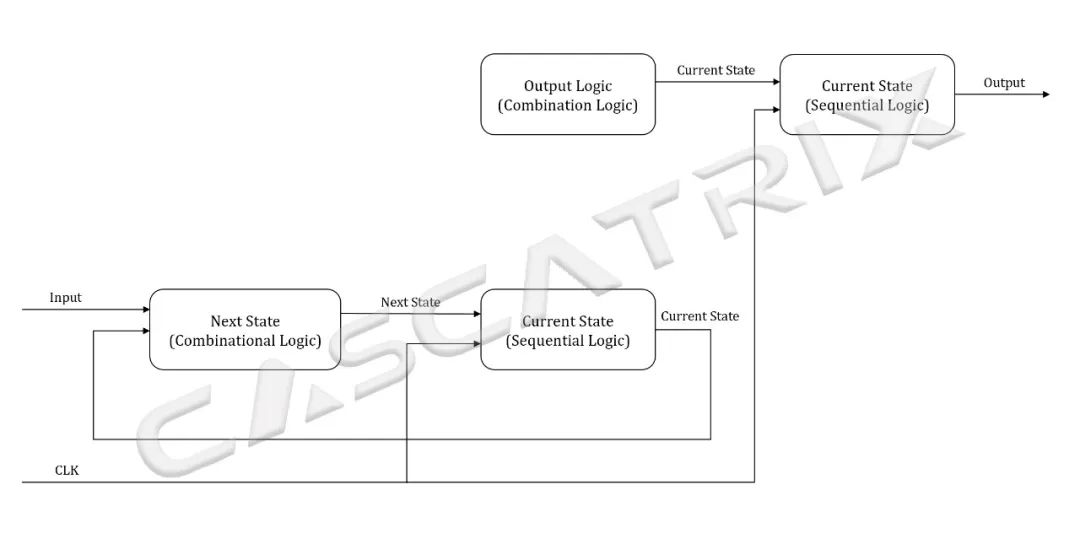

上述代碼所實(shí)現(xiàn)的三段式狀態(tài)機(jī)RTL視圖如下:?

三段式狀態(tài)機(jī)通過(guò)時(shí)序邏輯解決了兩段式寫(xiě)法中組合邏輯產(chǎn)生毛刺的問(wèn)題,同時(shí)保證代碼的可讀性和可維護(hù)性。從資源消耗方面而言,相比于一段式和兩段式狀態(tài)機(jī),三段式狀態(tài)機(jī)會(huì)占用更多資源,同時(shí)從輸入到輸出會(huì)延遲一個(gè)時(shí)鐘周期。

05

狀態(tài)機(jī)設(shè)計(jì)總結(jié)

狀態(tài)機(jī)三種寫(xiě)法可以總結(jié)如下:

一段式狀態(tài)機(jī):一個(gè)always塊,既描述狀態(tài)轉(zhuǎn)移,又描述狀態(tài)的輸入輸出,當(dāng)前狀態(tài)用寄存器輸出;

二段式:兩個(gè)always塊,時(shí)序邏輯與組合邏輯分開(kāi),一個(gè)always塊采用同步時(shí)序描述狀態(tài)轉(zhuǎn)移;另一個(gè)always塊采用組合邏輯判斷狀態(tài)轉(zhuǎn)移條件,描述狀態(tài)轉(zhuǎn)移規(guī)律以及輸出,當(dāng)前狀態(tài)用組合邏輯輸出,可能出現(xiàn)競(jìng)爭(zhēng)冒險(xiǎn),產(chǎn)生毛刺,而且不利于約束,不利于綜合器和布局布線器實(shí)現(xiàn)高性能的設(shè)計(jì);

三段式:三個(gè)always塊,一個(gè)always模塊采用同步時(shí)序描述狀態(tài)轉(zhuǎn)移;一個(gè)always采用組合邏輯判斷狀態(tài)轉(zhuǎn)移條件,描述狀態(tài)轉(zhuǎn)移規(guī)律;第三個(gè)always塊使用同步時(shí)序描述狀態(tài)輸出,寄存器輸出。

注:需要注意的是,狀態(tài)機(jī)三種不同寫(xiě)法的本質(zhì)區(qū)別是狀態(tài)機(jī)三要素(狀態(tài)、輸入和輸出)的邏輯功能,而非always塊的數(shù)量。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論