今天給大俠帶來基于FPGA的 模擬 I2C 協議設計,由于篇幅較長,分三篇。今天帶來第一篇,上篇,?I2C 總線解析以及模擬?I2C 接口程序的基本框架。話不多說,上貨。

導讀

I2C(Inter-Integrated Circuit),其實是 I2C Bus簡稱,中文就是集成電路總線,它是一種串行通信總線,使用多主從架構,由飛利浦公司在1980年代為了讓主板、嵌入式系統或手機用以連接低速周邊設備而發展。I2C的正確讀法為“I平方C”("I-squared-C"),而“I二C”("I-two-C")則是另一種錯誤但被廣泛使用的讀法。自2006年10月1日起,使用 I2C 協議已經不需要支付專利費,但制造商仍然需要付費以獲取 I2C 從屬設備地址。

I2C?簡單來說,就是一種串行通信協議,I2C的通信協議和通信接口在很多工程中有廣泛的應用,如數據采集領域的串行 AD,圖像處理領域的攝像頭配置,工業控制領域的 X 射線管配置等等。除此之外,由于 I2C 協議占用的 IO 資源特別少,連接方便,所以工程中也常選用 I2C 接口做為不同芯片間的通信協議。I2C 串行總線一般有兩根信號線,一根是雙向的數據線SDA,另一根是時鐘線SCL。所有接到?I2C 總線設備上的串行數據SDA都接到總線的SDA上,各設備的時鐘線SCL接到總線的SCL上。

在現代電子系統中,有為數眾多的 IC 需要進行相互之間以及與外界的通信。為了簡化電路的設計,Philips 公司開發了一種用于內部 IC 控制的簡單的雙向兩線串行總線 I2C(Intel-Integrated Circuit bus)。1998 年當推出?I2C?總線協議 2.0 版本時,I2C 協議實際上已經成為一個國際標準。

在進行 FPGA 設計時,經常需要和外圍提供?I2C?接口的芯片通信。例如低功耗的 CMOS 實時時鐘/日歷芯片 PCF8563、LCD 驅動芯片 PCF8562、并行口擴展芯片 PCF8574、鍵盤/LED 驅動器 ZLG7290 等都提供?I2C?接口。因此在 FPGA 中模擬?I2C?接口已成為 FPGA 開發必要的步驟。

本篇將詳細講解在 FPGA 芯片中使用 VHDL/Verilog HDL 模擬?I2C?協議,以及編寫 TestBench仿真和測試程序的方法。

第一篇內容摘要:本篇會介紹?I2C 總線解析,包括?I2C 總線概述、I2C 協議的基本概念、I2C協議的時序要求,還會介紹模擬 I2C 接口程序的基本框架等相關內容。

?

一、I2C?總線概述

?

下面先對 I2C 協議中有關數據格式和時序的內容進行介紹,這里沒有涉及的地方請參考《THE I2C-BUS SPECIFICATION VERSION 2.1 JANUARY 2000》。

1.1?I2C?總線概述

I2C 協議作為一個串行總線標準盡管沒有并行總線的數據吞吐能力,但是它的以下特點使其有著廣泛的應用:

? 只需要兩條總線—串行數據線 SDA 和串行時鐘線 SCL;

? 每個連接到總線的器件都可以通過惟一的地址和一直存在的簡單的主/從節點關系軟件設定地址,主節點可以發送數據或接收數據;

? 是真正的多主總線,當兩個或更多主節點同時初始化數據傳輸時,可以通過沖突檢測和仲裁防止數據被破壞;

? 串行的 8 位雙向數據傳輸位速率在標準模式下可達 100kbit/s,快速模式下可達400kbit/s,高速模式下可達 3.4Mbit/s;

? 片上的濾波器可以濾去總線數據線上的毛刺波,保證數據完整;

? 連接到相同總線的 IC 數量只受到總線的最大電容(400pF)限制。

總線不僅僅是互連的線,還包含系統通信的所有格式和過程。I2C 總線結構上的特點保證了其應用時的簡潔,另外其完備的協議避免了所有混亂、數據丟失和妨礙信息的可能性。

1.2 I2C?協議的基本概念

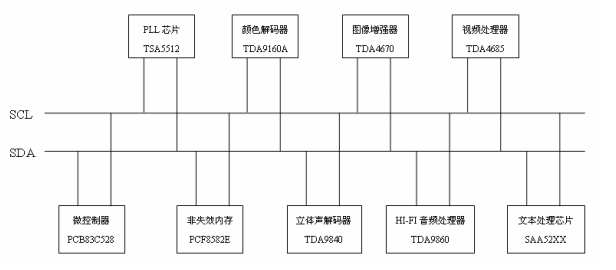

I2C 總線支持任何 IC 生產過程(NMOS、CMOS 和雙極性)。串行數據線 SDA 和串行時鐘線 SCL在連接到總線的器件間傳遞信息。每個器件都有一個惟一的地址作為識別的標志(無論是微控制器、LCD 驅動器存儲器還是鍵盤接口),并且都可以發送數據和接收數據。很明顯 LCD 驅動器只需要接收數據,而存儲器需要接收和發送數據。圖 1 所示的是一個高性能集成電視的例子。

圖 1 高性能集成電視

從圖 1 可以看到,應用?I2C 總線是非常方便的。用通俗的話講 I2C 總線的硬件設計工作就是連接 SDA 和 SCL 兩條線,依靠 I2C 協議完成軟件工作。在 I2C 協議中應理解如下的概念。

1)主/從節點

主節點負責初始化總線的數據傳輸,并產生允許傳輸的時鐘信號。此時任何被尋址的器件都被認為是從節點。當有多個主節點在總線上傳輸數據時,每個主節點產生自己的時鐘信號。掛接到總線上的所有外圍器件、外設接口都是總線上的節點。

2)總線上節點的尋址方式

在任何時刻總線上只有一個主控器件(主節點)實現總線的控制操作,對總線上的其他節點尋址,可分時實現點-點的數據傳送。因此總線上每個節點都有一個固定的節點地址。

I2C 總線上主節點的地址由軟件給定,此地址存放在 I2C 總線的地址寄存器中。I2C 總線上所有的外圍器件都有規范的器件地址。器件地址由 7 位數字組成,它和 1 位方向位構成了 I2C 總線器件的尋址字節 SLA(Slave address)。

器件地址是 I2C 總線外圍接口器件固有的地址編碼,器件出廠時就已給定。數據方向位規定了總線上主節點對從節點的數據傳送方向。

1.3 I2C協議的時序要求

1)總線上的數據傳遞時序

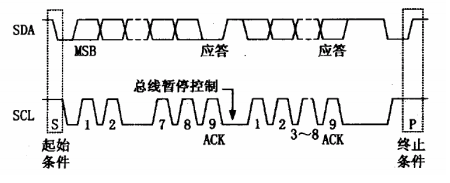

I2C 總線上數據傳遞時序如圖 2 所示,具體步驟如下。

圖 2 I2C 總線的數據傳遞時序

? 首先主節點器件發送一個起始信號。

? 接下來主節點器件發送從節點地址和讀寫方式,一共 8 位。其中從節點地址 7 位,讀寫方式 1 位。

? 與傳輸地址一致的從節點器件應答(即 ACK)。

? 開始數據傳輸,傳輸數據數量不限。每個字節(八位)后面跟接收數據方的應答位。例如主節點器件讀取從節點數據,從節點發送數據,主節點應答;主節點器件寫數據到從節點,主節點發送數據,從節點應答。

? 數據傳輸結束,主節點器件發送一個終止信號結束整個過程。

采用 I2C 總線后對傳送的字節數沒有限制,只要求每傳送一個字節后對方回應一個應答位。在發送時首先發送的是數據的最高位(MSB,Most Significant Bit)。每次傳送開始有起始信號,結束時有停止信號。在總線傳送完一個字節后,可以通過對時鐘線(SCL)的控制使傳送暫停。例如當某個外圍器件接收 N 個字節數據后需要一段處理時間以便繼續接收以后的字節數據,這時可在應答信號后使 SCL 變為低電平控制總線暫停。如果主節點要求總線暫停也可使時鐘線保持低電平控制總線暫停。

2)總線上的時序信號

I2C 總線為同步傳輸總線,總線信號完全與時鐘同步。I2C 總線上與數據傳送有關的信號有起始信號 S、終止信號 P、應答信號 A 以及位傳送信號。下面將對這些信號一一介紹。

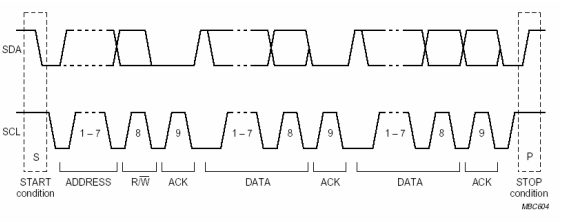

(1)起始信號

起始信號(Start Condition)如圖 3 所示。當時鐘線 SCL 為高電平時,數據線 SDA 從高電平向低電平變化將形成起始信號,啟動 I2C 總線。

(2)終止信號

終止信號(Stop Condition)如圖 3 所示。當時鐘線 SCL 為高電平時,數據線 SDA 從低電平向高電平變化將形成終止信號,停止 I2C 總線。

(3)應答信號

如圖 3 所中 ACK 第 9 個時鐘脈沖對應應答位,相應數據線上低電平時為應答信號,高電平時為非應答信號。

圖 3 起始信號和終止信號

(4)位傳送信號

在 I2C 總線啟動后或應答信號后的第 1~8 個時鐘脈沖對應于一個字節的 8 位數據傳送。脈沖高電平期間,數據串行傳送;低電平期間為數據準備,允許總線上數據電平變換。

?

二、模擬?I2C?接口程序的基本框架

?

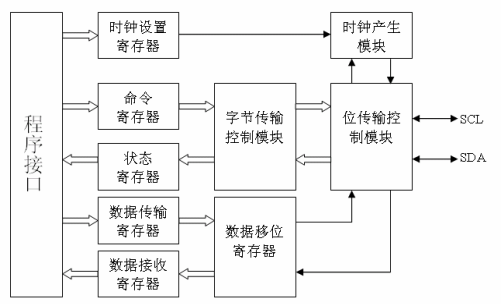

模擬 I2C 接口程序的基本框架如圖 4 所示。

圖 4 模擬 I2C 接口程序的基本框架

1)程序接口

用于和應用程序連接的接口,將應用程序的數據按照 I2C 協議的方式通過 SDA 傳遞給外部器件。包括下列內容:

? clk_I FPGA 外部時鐘信號。

? rst_I 同步重起信號。

? arst_I 異步重起信號。

? adr_I 從節點地址。

? dat_I 輸入數據。

? dat_o 輸出數據。

? we_I 寫有效信號。

? stb_I 接口有效信號。

? cyc_I 有效總線周期輸入。

? ack_o 應答信號輸出。

? inta_o 中斷信號輸出。

2)時鐘設置寄存器

I2C 協議提供了 3 種速度模式:正常速度模式 100kbit/s、快速模式 400kbit/s、高速模式3.5Mbit/s。SCL 輸出的時鐘信號頻率和速度模式一致。程序內部使用 5 倍 SCL 信號作為時鐘,而 FPGA 外部時鐘需要經過分頻得到程序內部使用的時鐘。

例如:采用正常速度 100kbit/s,FPGA 外部時鐘為 50MHz,則時鐘設置寄存器需要設置為(50MHz/5*100kHz – 1=99)。

3)時鐘產生模塊

時鐘產生模塊產生 4 倍 SCL 頻率的時鐘信號,它為位傳輸控制模塊中所有同步動作提供觸發信號。

4)命令寄存器

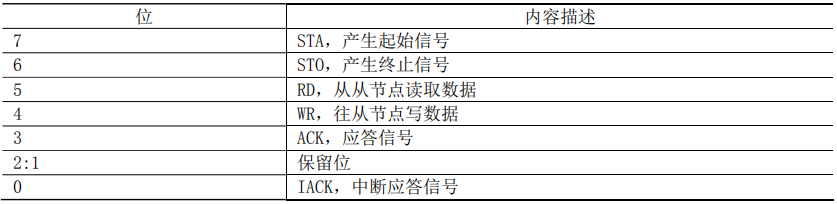

命令寄存器共 8 位,它決定是否在總線上產生各種時序信號、是否讀/寫數據,各位表示的含義如表 1 所示。

表 1 命令寄存器內容

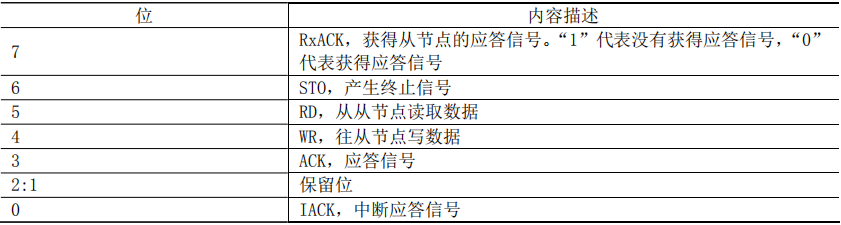

5)狀態寄存器

狀態寄存器用來顯示當前總線的狀態,例如是否接收到從節點的應答信號、是否忙、是否在傳遞數據等,具體內容如表 2 所示。

表 2 狀態寄存器內容

6)數據傳輸寄存器

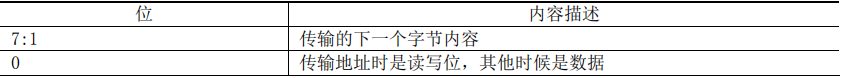

數據傳輸寄存器用于保存等待傳輸的數據。當傳遞從節點地址信息時,前 7 位保存從節點地址,最后一位保存讀寫命令;當傳遞普通數據時,8 位保存一個字節數據。數據傳輸寄存器具體內容如表 3 所示。

表 3 數據傳輸寄存器內容

7)數據接收寄存器

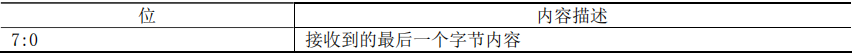

數據接收寄存器用于保存通過 I2C 總線接收到的最后一個字節內容,具體內容如表4所示。

表 4 數據接收寄存器內容

8)字節傳輸控制模塊

字節傳輸控制模塊以字節為單位控制 I2C 總線的數據傳輸。這個模塊按照命令寄存器設置的內容將數據傳輸寄存器內容傳遞到 I2C 總線的接收端,或者從 I2C 總線發送端接收數據并保存到數據接收寄存器中。

9)位傳輸控制模塊

位傳輸控制模塊以位為單位進行 I2C 總線的數據傳輸和產生各個 I2C 協議命令(如開始、停止、重復開始等)。字節傳輸控制模塊控制位傳輸控制模塊的各種動作。例如讀取一個字節數據,位傳輸控制模塊需要執行 8 個讀的命令。

10)數據移位寄存器

數據移位寄存器保存的數據總是和當前的數據傳輸相關的。例如在進行讀操作時,主節點通過移位寄存器依次通過 SDA 獲得來自 I2C 發送端的數據,完成后數據拷貝到數據接收寄存器中。在寫操作時,數據傳輸寄存器中的數據拷貝到數據移位寄存器中,然后依次通過 SDA 將數據傳輸到 I2C 總線的接收端。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論