時鐘是整個電路最重要、最特殊的信號,系統內大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時序邏輯狀態出錯。

2020-06-26 10:37:00 4550

4550

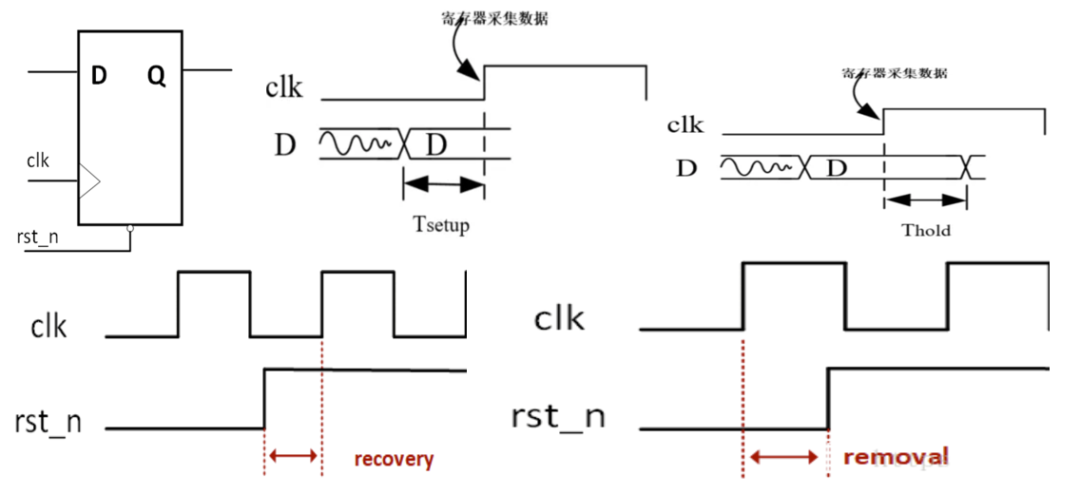

靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持時間設置不正確芯片無法正常工作。

2022-08-22 10:38:24 3289

3289 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

在FPGA設計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1230

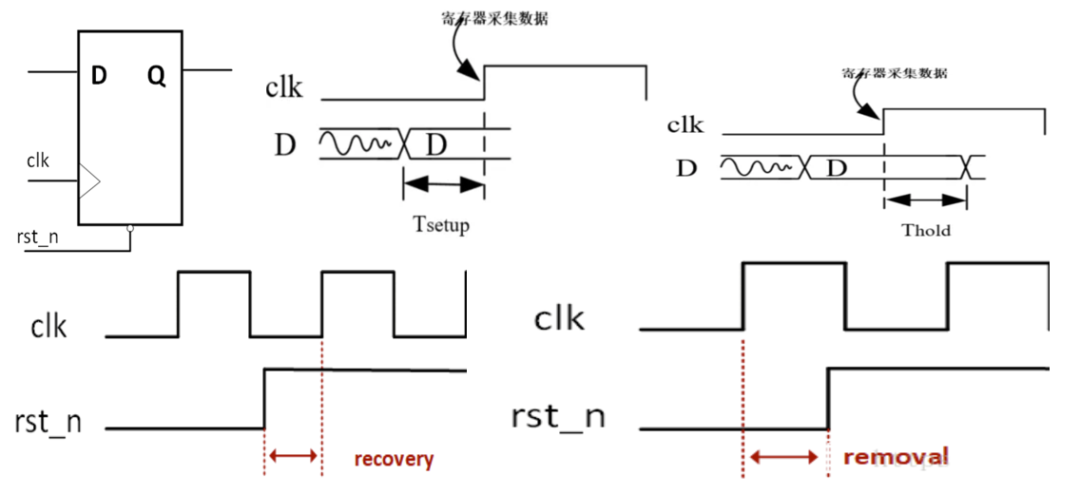

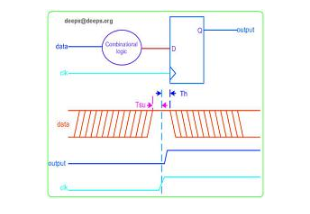

1230 建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

2023-06-21 10:44:01 884

884

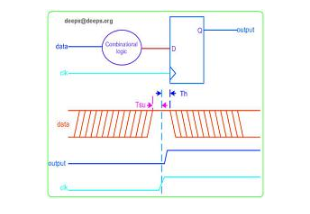

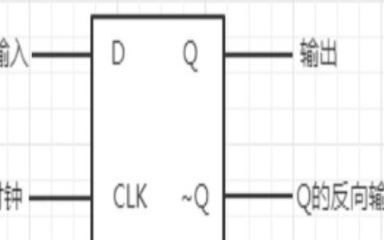

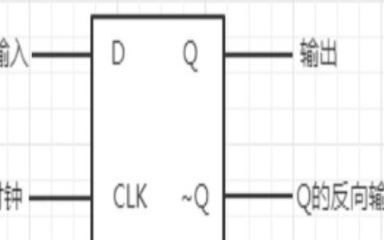

時序分析本質上就是一種時序檢查,目的是檢查設計中所有的D觸發器是否能夠正常工作,也就是檢查D觸發器的同步端口(數據輸入端口)的變化是否滿足建立時間要求(Setup)和保持時間要求(Hold);檢查

2023-07-14 10:48:19 1326

1326

今天有個小伙伴遇到一個問題,就是在vivado里面綜合后看到的建立時間和保持時間裕量都是inf,我們來看看怎么解決這個問題。

2023-07-30 10:26:02 649

649

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

我理解這個D觸發正常運轉要滿足四個約束,第一個是建立時間,第二個是保持時間,第三個是對于最后一個傳輸門的關斷時間的控制,第四個是[時鐘周期]() 約束。

2023-12-04 15:44:02 352

352

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

FPGA時序分析與約束(2)——與門電路代碼對應電路模型的時序分本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:InterQuartesⅡ時序分析中常見的時間參數:Tclk1:時鐘從時鐘

2021-07-26 08:00:03

的幾個基本的重要的時序分析參數:fMAX(最大時鐘頻率):在不違背內部建立時間tsu和保持時間th要求下可以達到的最大時鐘頻率;tSU(時鐘建立時間):在寄存器的時鐘信號已經在時鐘引腳建立之前,經由數據或者使能輸入而進入寄存器的數據必須在輸入引腳出現的時間長度;(equation:tsu

2012-04-09 09:41:41

后期頂層模塊集成占用大資源時爆發出來。 下面介紹主要面對的兩個時序問題的處理技巧。 1)setup time 建立時間問題 建立時間是工程設計中最常遇到的問題了。一般說來,導致建立時間違例主要有

2020-12-23 17:42:10

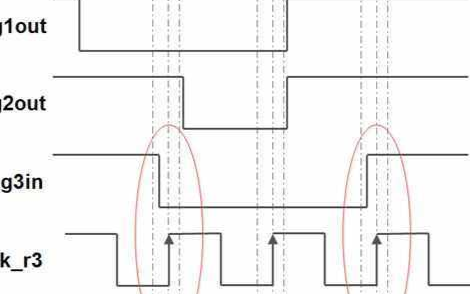

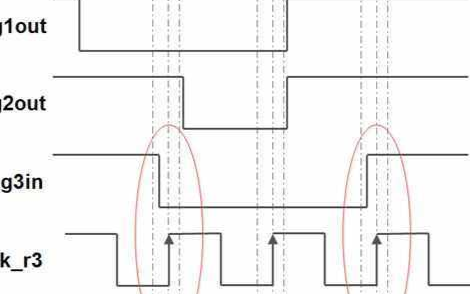

建立時間和保持時間本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 在這個波形中,我們看到clk_r3的前后

2015-07-17 12:02:10

),即pin2pin前面三類是和FPGA內部的寄存器相關的,也是和時鐘相關的,所以我們關注的重點還是數據信號和時鐘鎖存沿之間的建立時間和保持時間關系。而最后一類信號的傳輸通常不通過時鐘,因此它的時序

2015-07-20 14:52:19

對應的時序表中,我們找到了t1>0.2ns,t2>1.5ns這樣的信息。表8.1 ADV7123時序參數表參數名稱最小值 標準值 最大值單位 數據和控制信號建立時間t1 0.2ns 數據和控制信號保持時間t2 1.5ns

2015-07-26 21:56:45

,最后在計算ADV7123的時序時,我們必須將數據的建立時間Tsu和保持時間Th考慮在內。(特權同學,版權所有)圖8.30 時序路徑模型

2015-07-30 22:07:42

VGA驅動接口時序設計之4建立和保持時間分析本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt下面我們可以簡單

2015-08-02 19:26:19

VGA驅動接口時序設計之6建立和保持時間約束本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 接著,我們可以

2015-08-06 21:49:33

8.42 hold時間時序分析報告為了幫助大家進一步的理解時序的概念,這里可以找一條路徑,將他們的建立時間和保持時間波形圖同時拉出來,如圖8.43所示,大家便可一目了然。建立時間和保持時間會分別使用他

2015-08-10 15:03:08

約束,就是設計者告訴時序設計工具FPGA外部的路徑上占用了4ns時間,時序設計工具自己有一套運算機制,它也能運算出FPGA內部的pin2reg時間是6ns。而我們這個模型和所使用的約束方式,是間接方式

2015-08-12 12:42:14

所示,在報告中,數據的建立時間有9~13ns的余量,而保持時間也都有7~11ns的余量,可謂余量充足。(特權同學,版權所有)圖8.57 setup時序報告圖8.58 hold時序報告另外,我們也可以

2015-08-19 21:58:55

FPGA設計中的時序分析及異步設計注意事項建立時間(setup time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保持

2009-12-07 10:14:33

整個系統進行時序分析,所以FPGA需要作為一個整體分析,其中包括FPGA的建立時間、保持時間以及傳輸延時。傳統的建立時間、保持時間以及傳輸延時都是針對寄存器形式的分析。但是針對整個系統FPGA的建立時間

2012-04-25 15:42:03

的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為FPGA設計的主要驗證手段之一,不需要設計者編寫測試向量,由軟件自動

2012-01-11 11:43:06

如圖,建立時間和保持時間都是針對的時鐘沿,如圖所示,時鐘沿有一個上升的過程,圖中虛線與clk上升沿的交點是什么?幅值的50%?還是低電平(低于2.5V)往高電平(高于2.5V)跳轉的那個點?

2018-11-29 00:20:02

本帖最后由 虎子哥 于 2015-3-12 21:24 編輯

建立時間(Setup Time):是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘

2015-03-10 23:19:03

工作時鐘卻只有100MHz,查資料這款FPGA最快可跑四五百M,時序約束也沒有不滿足建立時間和保持時間的報錯,本身整個系統就用了一個時鐘,同步設計請教一下,為什么只能跑100MHz?是什么原因限制了呢

2017-08-14 15:07:05

約束中的注意事項。 一、時序分析中的重要概念 在數字系統中有兩個非常重要的概念:建立時間和保持時間,其示意圖如圖1所示。一個數字系統能否正常工作跟這兩個概念密切相關。只有建立時間和保持時間都同時得到

2020-08-16 07:25:02

時序約束可以很復雜,這里我們先介紹基本的時序路徑約束,復雜的時序約束我們將在后面進行介紹。在本節的主要內容如下所示:·時序路徑和關鍵路徑的介紹 ·建立時間、保持時間簡述 ·時鐘的約束(寄存器-寄存器之間的路徑約束) ·輸入延時的約束 ·輸出延...

2021-07-26 08:11:30

Hi,All AD7195數據手冊中講,當選擇Sinc(4)濾波(禁用斬波,禁用零延時),在通道切換或單個通道上進行轉換且輸入發生階躍變化時,ADC建立時間為4/fadc。 我的問題時,如果使用了

2018-11-06 09:08:07

ADC時延和建立時間的區別是什么?以及ADC時延和建立時間將會如何影響您的應用電路?

2021-04-12 07:19:18

有沒有人遇到在DC綜合后分析建立時間時序,關鍵路徑時序違例是因為起始點是在時鐘的下降沿開始驅動的,但是設計中都是時鐘上升沿觸發的。在線等待各位大牛解惑!很急 求大神幫忙!

2015-01-04 15:17:16

PLL jitter 對建立時間和保持時間有什么樣的影響?哪位大神給解答下

2015-10-30 11:16:30

VGA驅動接口時序設計之4建立和保持時間分析本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們可以

2019-04-10 06:33:34

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?

2021-09-28 08:51:33

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

什么叫建立時間,保持時間,和恢復時間

2017-04-08 16:52:35

1、FPGA中的時序約束--從原理到實例 基本概念 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。 電路中的建立時間和保持時間其實跟生活中的紅綠燈很像

2022-11-15 15:19:27

。這種方法把準確性和精確度建立在波形生成器和采樣保持電路的相對速度上。 受測器件的步進輸入 本文中,建立時間是指使用某個理想步進輸入,到受測器件(DUT)進入并維持在某個規定誤差范圍(終值對稱)內

2012-07-30 17:36:20

的工作時鐘,通過調整sdram_clk的相位就能調整時序,從而滿足建立時間和保持時間的要求。那么sdram_clk如何產生呢?可以通過PLL來產生,PLL可以保證頻率相同、相位偏移量,所以該系統的結構

2016-09-13 21:58:50

關于數字IC的建立時間以及保持時間你想知道的都在這

2021-09-18 07:24:40

接口的光以太網數據通信就正常了。 這里闡述了時序分析基礎,說明概念的同時進行了時序分析,通過時序分析理解建立時間和保持時間。希望大家閱讀本文之后可以對FPGA時序分析有進一步的了解。

2018-04-03 11:19:08

建立時間測量的采樣保持方法測試裝置存在哪些局限性?

2021-04-09 06:08:05

建立時間(Setup Time)是指觸發器的時鐘信號上升沿到來之前,數據保持穩定不變的時間。 輸入信號應該提前時鐘上升沿(如上升沿有效)Tsu時間到達芯片,這個 Tsu就是建立時間。如果不滿足建立時間

2021-07-26 07:36:01

請問,對于觸發器的時鐘信號,建立時間和保持時間有要求嗎?剛看到一個門控時鐘產生毛刺的反例,(如下圖)想到了這個問題。若此時鐘信號毛刺極小,有沒有可能被觸發器忽略呢?為什么呢?如果有可能小到什么程度會被忽略呢?

2012-01-27 18:44:58

建立時間是什么意思?精確測量ADC驅動電路建立時間

2021-04-14 06:29:09

一般運算放大器的datasheet都會給出0.01%建立時間(有的給出0.1%建立時間),比如ADA4897,給出2V階躍測試時0.01%建立時間為90 ns。因此對于單運放電路來說,建立時間可以

2018-11-13 15:08:15

16444_[。只有降低SPI頻率到20MHz才ok。(2)問題分析:通過示波器測量,發現DM9051的cs建立時間和保持時間很緊張,其它信號質量和時序ok,需要增加cs的建立時間和保持時間來試試。(3

2023-02-15 06:55:16

T2max,最小為T2min。問,觸發器D2的建立時間T3和保持時間應滿足什么條件

2019-09-09 17:19:55

在PCB走線的延時,因此上圖只是一個理想過程,即沒有考慮PCB走線的延時,而我們的時序分析工具確實將其考慮在內了,所以,我們的FPGA建立時間,除了包括數據保持穩定的時間外,還應加上這段走線延時的時間

2015-03-31 10:35:18

FPGA內部的走線延遲,時鐘延遲等等,這里我們添加的時序約束,就相當于我們在沒有下板之前,通過計算,來模擬仿真下板后的延遲情況,并通過時序報告查看有哪些違規路徑,以及建立保持時間不平衡的情況,通過時序

2015-03-31 10:20:00

該文簡要討論了環路性能(建立時間,相位噪聲和雜散信號)和環路參數(帶寬,相位裕度等)的相互關系。提出并分析了一種自適應的具有快速建立時間的鎖相環結構及其關鍵模塊(鑒相

2010-04-23 08:33:53 20

20 該文提出一種基于時間約束的FPGA數字水印技術,其基本思想是將準備好的水印標記嵌人非關鍵路徑上的時間約束來定制最終的下載比特流文件,同時并不改變設計的原始性能.這一方

2010-06-09 07:45:49 7

7 基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

基本概念:線與邏輯、鎖存器、緩沖器、建立時間、緩沖時間

標簽/分類:

2007-08-21 15:17:27 1169

1169 時延和建立時間setup在ADC電路中的區別:對于大多數 ADC 用戶來說,“時延”和“建立時間”這兩個術語有時可以互換。但對于 ADC 設計人員而言,他們非常清楚

2007-11-22 23:33:07 1430

1430 為實現高速DAC的最佳性能,必須滿足一定的建立和保持時間要求。在200 MSPS至250 MSPS的時鐘速率下,FPGA/ASIC/DAC的全部時序預算并不是一件小事。客戶若要完成時序驗證,必須清楚列出并

2011-11-24 14:20:35 33

33 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 建立時間和保持時間貫穿了整個時序分析過程。只要涉及到同步時序電路,那么必然有上升沿、下降沿采樣,那么無法避免setup-time 和 hold-time這兩個概念。 1. 什么是setup-time

2017-02-08 14:48:11 4928

4928 今天,我們將介紹兩種相關的動態參數 — 壓擺率與建立時間。如欲了解更多有關靜態和動態參數的不同之處,敬請參閱本文。

2018-07-10 16:14:00 5294

5294

,您經常需要定義時序和布局約束。我們了解一下在基于賽靈思 FPGA 和 SoC 設計系統時如何創建和使用這兩種約束。 時序約束 最基本的時序約束定義了系統時鐘的工作頻率。然而,更高級的約束能建立時鐘路徑之間

2017-11-17 05:23:01 2417

2417

和底層工具Planahead實現高速串并轉換中數據建立時間和保持時間的要求,實現并行數據的正確輸出。最后通過功能測試和時序測試,驗證了設計的正確性。此方法可適用于高端和低端FPGA,提高了系統設計的靈活性,降低了系統的成本。

2017-11-17 12:27:01 6488

6488

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:02:00 4100

4100

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 1894

1894

時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-06-19 15:04:17 5601

5601

首先來看什么是時序約束,泛泛來說,就是我們告訴軟件(Vivado、ISE等)從哪個pin輸入信號,輸入信號要延遲多長時間,時鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠

2020-01-28 17:34:00 3077

3077

本篇仿真介紹放大器的建立時間,也稱為上升時間。它是高速放大電路、或在SARADC驅動電路設計時,需要謹慎評估的參數。

2021-02-15 16:37:00 5258

5258

AN-359:運算放大器的建立時間

2021-04-29 15:28:46 3

3 約束條件可以使綜合布線工具調整映射和布局布線過程,使設計達到時序要求。例如用OFFSET_IN_BEFORE約束可以告訴綜合布線工具輸入信號在時鐘之前什么時候準備好,綜合布線工具就可以根據這個約束調整與IPAD相連的Logic Circuitry的綜合實現過程,使結果滿足FFS的建立時間要求。 附加時序

2021-09-30 15:17:46 4401

4401 約束條件可以使綜合布線工具調整映射和布局布線過程,使設計達到時序要求。例如用OFFSET_IN_BEFORE約束可以告訴綜合布線工具輸入信號在時鐘之前什么時候準備好,綜合布線工具就可以根據這個約束調整與IPAD相連的Logic Circuitry的綜合實現過程,使結果滿足FFS的建立時間要求。 附加時序

2021-10-11 10:23:09 4861

4861

同步電路系統設計將系統狀態的變化與時鐘信號同步,并通過這種理想化的方式降低電路設計難度。同步電路設計是FPGA設計的基礎。

2022-02-26 16:59:44 2590

2590

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立時間或保持時間所多出的時間,那么“裕量”越多,意味著時序約束越寬松。

2022-08-04 17:45:04 657

657 對于建立時間和保持時間本文就不再過多敘述,可參考【FPGA】幾種時序問題的常見解決方法-------3,可以說在數字高速信號處理中最基本的概念就是建立時間和保持時間,而我們要做的就是解決亞穩態問題和傳輸穩定問題。

2022-12-13 11:03:58 225

225 時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。

2023-02-06 11:06:03 256

256 一個風險(時序報告是按照工藝、電壓以及溫度的上下限給出的結果)。當違例數較多,也就意味著設計在實際環境中出現問題的概率也會越大。? ? ? 時間裕量包括建立時間裕量和保持時間裕量(setup slack和hold slack)。從字面上理解,所謂“裕量”即富余的、多出的。什

2023-03-17 03:25:03 426

426 運算放大器建立時間是保證數據采集系統性能的關鍵參數。為了實現精確的數據采集,運算放大器輸出必須在A/D轉換器能夠準確數字化數據之前建立。然而,建立時間通常不是一個容易測量的參數。

2023-06-17 10:37:54 368

368

??本文主要介紹了建立時間和保持時間。

2023-06-21 14:38:26 1081

1081

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

在時序電路設計中,建立時間/保持時間可以說是出現頻率最高的幾個詞之一了,人們對其定義已經耳熟能詳,對涉及其的計算(比如檢查時序是否正確,計算最大頻率等)網上也有很多。

2023-06-27 15:43:55 4597

4597

建立時間和保持時間是SOC設計中的兩個重要概念。它們都與時序分析有關,是確保芯片正常工作的關鍵因素。

2023-08-23 09:44:55 390

390 信號經過傳輸線到達接收端之后,就牽涉到建立時間和保持時間這兩個時序參數,它們表征了時鐘邊沿觸發前后數據需要在鎖存器的輸入持續時間,是接收器本身的特性。簡而言之,時鐘邊沿觸發前,要求數據必須存在一段時間,這就是器件需要的建立時間;

2023-09-04 15:16:19 392

392

文件提到兩種setup/hold測量方式:10% push-up和pass/fail,按照TSMC說法,前者會更樂觀一些,因此如果是采用前者(10% push-up)的測量方式得到建立時間和保持時間,需要十份小心時序裕量是否足夠,最好人為添加margin。

2023-12-05 11:19:38 696

696

電子發燒友App

電子發燒友App

評論