什么是FPGA?

現(xiàn)場可編程門陣列 (FPGA) 是可以在制造后進行編程和重新編程以實現(xiàn)數(shù)字邏輯功能的半導(dǎo)體器件。FPGA 通過提供可配置為執(zhí)行各種任務(wù)的可編程硬件塊和互連,提供了實現(xiàn)數(shù)字電路的獨特方法。

FPGA 的組件

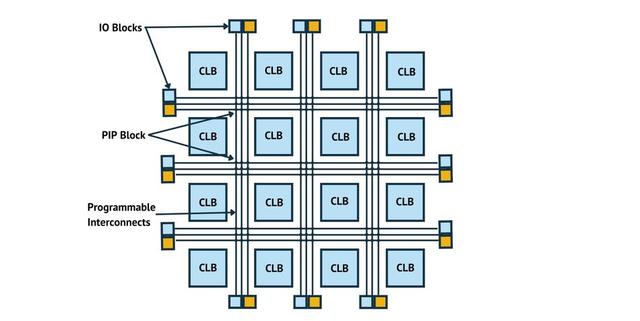

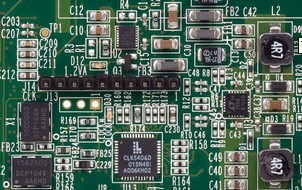

FPGA(現(xiàn)場可編程門陣列)由多個關(guān)鍵組件組成,這些組件協(xié)同工作以實現(xiàn)定制數(shù)字電路的實現(xiàn)和配置。FPGA 的主要組件有:

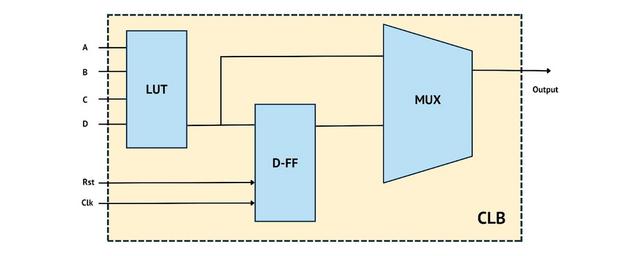

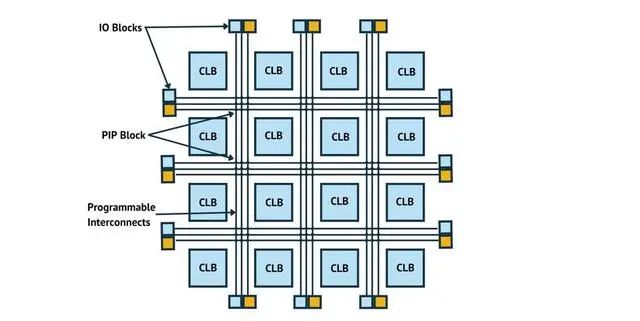

- 可配置邏輯塊 (CLB): 這些是 FPGA 的基本構(gòu)建塊,包含查找表 (LUT)、觸發(fā)器,有時還包含專用算術(shù)單元。CLB 可配置為執(zhí)行各種組合和順序邏輯功能。

- **可編程互連點 (PIP): **這些是連接 CLB 和 FPGA 內(nèi)其他組件的可編程開關(guān)和接線資源。PIP 允許芯片上不同元件之間的信號靈活路由和互連。從本質(zhì)上講,晶體管是 FPGA 的基本構(gòu)建模塊,形成 CLB 和 PIP。

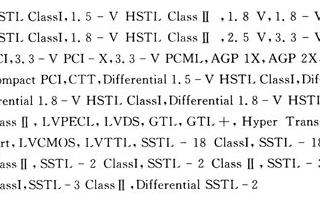

- **輸入/輸出塊 (IOB): **這些是 FPGA 與外部設(shè)備或板上其他組件之間的接口點。IOB 可配置為支持各種信號標(biāo)準(zhǔn)和協(xié)議,使 FPGA 能夠與各種外設(shè)進行通信。

- **Block RAM (BRAM): **這是 FPGA 上可用的片上存儲器,用于存儲數(shù)據(jù)和實現(xiàn)存儲器功能。BRAM 比片外存儲器更快,并且可以以更低的延遲進行訪問。

- **數(shù)字信號處理 (DSP) 塊: **這些是專門用于高速執(zhí)行算術(shù)運算(例如乘法和累加)的專用硬件塊。DSP 模塊通常用于信號處理和濾波應(yīng)用。

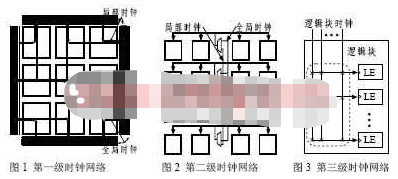

- **時鐘管理資源: **包括鎖相環(huán) (PLL) 和數(shù)字時鐘管理器 (DCM),用于在 FPGA 內(nèi)生成、分配和管理時鐘信號。這些資源有助于保持整個設(shè)備的精確定時和同步。

- **配置存儲器: **這是存儲配置比特流的閃存,它對FPGA進行編程以實現(xiàn)所需的數(shù)字電路。比特流在啟動時或需要重新編程時加載到 FPGA 中。

傳統(tǒng)上,代碼被編寫并編譯成在處理器上運行的指令。然而,對于 FPGA,可以使用硬件描述語言 (HDL) 以不同的方式編寫代碼。然后,該代碼被合成到物理硬件模塊中,可以將其配置為直接在 FPGA 上執(zhí)行所需的邏輯功能。FPGA 中的硬件模塊由寄存器和各種類型的邏輯門組成,例如 AND、OR、NOR、NOT、XOR 和 XNOR 門。這些門可以組合起來創(chuàng)建復(fù)雜的數(shù)字電路。

FPGA 靈活性的關(guān)鍵在于使用查找表 (LUT) 來實現(xiàn)邏輯門。這些邏輯塊之間的互連也是可編程的,允許靈活的信號布線和路由。通過使這些 LUT 可編程并使用可重新配置的交換結(jié)構(gòu)連接它們,F(xiàn)PGA 可以定制來執(zhí)行各種任務(wù)。通過提供可以運行用戶所需的任何代碼的單一設(shè)備,F(xiàn)PGA 已在從原型設(shè)計到高性能計算的各種應(yīng)用中變得流行。

HDL 語言:VHDL 和 Verilog

硬件描述語言 (HDL) 用于描述高抽象級別的數(shù)字電路。FPGA 設(shè)計中使用的兩種主要 HDL 是 VHDL 和 Verilog。

- **VHDL: **VHDL(VHSIC 硬件描述語言)是一種強類型、詳細(xì)的語言,提供高級抽象,使編寫復(fù)雜設(shè)計變得更加容易。它廣泛應(yīng)用于歐洲以及航空航天和國防等行業(yè)。

- Verilog: Verilog 是一種更簡潔的、類似 C 的語言,在美國和商業(yè)領(lǐng)域很流行。與 VHDL 相比,它的抽象級別較低,這使得復(fù)雜設(shè)計更具挑戰(zhàn)性,但也可以更好地控制設(shè)計。

這兩種語言都有其優(yōu)點和缺點,VHDL 和 Verilog 之間的選擇通常取決于個人喜好或行業(yè)標(biāo)準(zhǔn)。

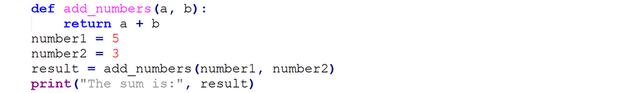

為了更好地理解其中的差異,讓我們看一下將兩個數(shù)字相加的 Python 代碼:

在Python中,代碼是用高級語言編寫的,該語言抽象了底層硬件的細(xì)節(jié)。函數(shù) add_numbers 接受兩個輸入參數(shù) a 和 b,并返回它們的和。該代碼由處理加法運算的處理器執(zhí)行。

現(xiàn)在,讓我們看一下將兩個數(shù)字相加的簡單 Verilog 代碼:

在此 Verilog 代碼中,我們定義了一個名為 Adder 的模塊,該模塊具有兩條 4 位輸入線 A 和 B,以及一條 4 位輸出線 Sum。該代碼描述了使用分配語句將兩個數(shù)字相加的數(shù)字電路的行為,該分配語句利用 FPGA 的可編程邏輯資源直接在硬件中執(zhí)行。結(jié)果是設(shè)計用于將兩個 4 位數(shù)字相加的定制電路。

兩種方法之間的主要區(qū)別在于,Python 代碼由處理器順序執(zhí)行,而 Verilog 代碼描述了使用 FPGA 直接在硬件中實現(xiàn)的數(shù)字電路。這意味著基于 FPGA 的加法器可以并行執(zhí)行加法運算,并且與執(zhí)行 Python 代碼的處理器相比,速度通常更快。然而,Python提供了更多的靈活性和易用性,而Verilog則需要對數(shù)字電路設(shè)計和FPGA資源有更深入的了解。

FPGA的優(yōu)點

與其他技術(shù)相比,F(xiàn)PGA 具有多項優(yōu)勢,包括:

- 靈活性: FPGA可以重新編程以實現(xiàn)不同的功能,使其適合廣泛的應(yīng)用。

- **快速原型設(shè)計: **FPGA 允許設(shè)計人員快速測試和迭代其設(shè)計,從而縮短上市時間。

- 并行性: FPGA 可以同時執(zhí)行多個任務(wù),這可以提高某些應(yīng)用的性能。

- **定制: **FPGA 可以創(chuàng)建滿足特定要求的專用硬件,通常可以優(yōu)化性能并降低功耗。

- **可重新配置性: **FPGA 可以在現(xiàn)場重新配置,從而無需更換整個硬件即可進行更新、錯誤修復(fù)或功能添加。

- **更低的 NRE 成本: **FPGA 開發(fā)不需要與定制 ASIC 設(shè)計相關(guān)的高額一次性工程 (NRE) 成本,這使得它們更適合小規(guī)模生產(chǎn)或概念驗證項目。

- **可擴展性: **FPGA 設(shè)計可以根據(jù)要求輕松擴展或縮小,從而實現(xiàn)高效的資源利用和經(jīng)濟高效的解決方案。

- **安全性: **FPGA 可以通過基于硬件的加密和安全啟動功能提供更高的安全性,與基于軟件的實現(xiàn)相比,這些功能更難以篡改。

- **模擬和數(shù)字接口: **FPGA 可以與各種模擬和數(shù)字外設(shè)連接,從而簡化系統(tǒng)集成并允許不同組件之間的無縫通信。

- **壽命長: **基于 FPGA 的設(shè)計通常比 ASIC 具有更長的壽命,因為它們可以更新和重新編程以適應(yīng)不斷發(fā)展的標(biāo)準(zhǔn)和技術(shù)。

- 設(shè)計重用: IP 核和之前開發(fā)的 FPGA 設(shè)計可以輕松重用并集成到新項目中,從而減少開發(fā)時間和工作量。

FPGA的缺點

與 ASIC 和微控制器等其他技術(shù)相比,F(xiàn)PGA 有一些缺點。一些缺點包括:

- 成本: FPGA 可能比微控制器或 ASIC 更昂貴,特別是對于大批量生產(chǎn)。對于大批量來說,F(xiàn)PGA 的單位成本通常高于 ASIC 或微控制器。

- **功耗: **FPGA 通常比 ASIC 和微控制器消耗更多的功耗,這可能是功耗敏感應(yīng)用中的一個問題。

- 設(shè)計復(fù)雜性: FPGA 的設(shè)計過程可能比微控制器更復(fù)雜,需要硬件設(shè)計、HDL、綜合和布局布線工具方面的專業(yè)知識。

- **性能限制: **雖然 FPGA 提供并行性并且可以為某些任務(wù)提供高性能,但對于某些應(yīng)用,它們可能不如 ASIC 快,因為 ASIC 是針對特定用途定制設(shè)計的,并且可以針對性能進行高度優(yōu)化。

- **尺寸: **FPGA 可能比同等的 ASIC 或微控制器更大,因為它們包含用于可編程性和重新配置的額外資源。

- **配置時間: **FPGA 需要在啟動時進行配置,這可能會導(dǎo)致啟動時間比 ASIC 和微控制器更長。

FPGA、ASIC、PLD、微控制器

FPGA、專用集成電路(ASIC)、可編程邏輯器件(PLD)和微控制器都是用于實現(xiàn)數(shù)字邏輯功能的技術(shù),但它們在各個方面有所不同。讓我們對這些技術(shù)進行比較和對比:

- **FPGA: **如前所述,F(xiàn)PGA 是可重新編程的,因此適合廣泛的應(yīng)用。它們提供高性能和并行性,但與 ASIC、PLD 和微控制器相比更昂貴且耗電。

- **ASIC: **ASIC 是針對特定應(yīng)用定制的,可優(yōu)化性能和功耗。然而,它們的前期成本高、開發(fā)時間長,并且缺乏 FPGA 和 PLD 的靈活性,因此適合大批量生產(chǎn)。

- **PLD: **PLD包括復(fù)雜可編程邏輯器件(CPLD)和簡單可編程邏輯器件(SPLD),是類似于FPGA的可重構(gòu)硬件,但復(fù)雜性較低,資源較少。它們非常適合更簡單的數(shù)字設(shè)計,并且可以提供比 FPGA 更低的成本和功耗,但可能缺乏 FPGA 對于更復(fù)雜應(yīng)用的性能和靈活性。

- **微控制器: **微控制器是具有集成內(nèi)存、處理和輸入/輸出功能的通用計算設(shè)備。它們通常比 FPGA 和 PLD 速度慢且并行性較差,但更便宜、功耗更低并且更易于開發(fā)。

總之,F(xiàn)PGA 提供靈活性和并行性,ASIC 提供優(yōu)化的性能和功耗,PLD 提供簡單性和成本效益,而微控制器經(jīng)濟高效且易于開發(fā)。技術(shù)的選擇取決于應(yīng)用的具體要求以及性能、功耗、開發(fā)時間和成本之間所需的權(quán)衡。

FPGA 設(shè)計流程和方法

在本節(jié)中,我們將探討 FPGA 設(shè)計流程,包括設(shè)計流程、硬件描述語言、寄存器傳輸級 (RTL) 設(shè)計、綜合、實現(xiàn)以及測試和調(diào)試。

設(shè)計流程概述

FPGA 設(shè)計流程由幾個步驟組成,指導(dǎo)設(shè)計人員從概念到功能齊全的 FPGA 實現(xiàn)。這些步驟包括:

- 設(shè)計輸入: 設(shè)計人員使用 VHDL 或 Verilog 等 HDL 創(chuàng)建所需數(shù)字電路的高級表示。

- **RTL 設(shè)計和仿真: **HDL 代碼被轉(zhuǎn)換為 RTL 表示,然后進行仿真以驗證功能和性能。

- 綜合: RTL 設(shè)計被轉(zhuǎn)換為門級網(wǎng)表,即使用門和觸發(fā)器的數(shù)字電路的表示。

- **實現(xiàn): **門級網(wǎng)表映射到 FPGA 的資源,包括 CLB、DSP 切片和可編程互連。此步驟包括布局布線和比特流生成。

- **測試和調(diào)試: **使用仿真工具、測試平臺或目標(biāo)硬件對 FPGA 器件進行測試和調(diào)試,以確保正確的功能和性能。

在整個設(shè)計流程中,使用各種工具和軟件來促進 FPGA 設(shè)計的設(shè)計、仿真、綜合和實現(xiàn)。

RTL 設(shè)計與仿真

RTL 設(shè)計是數(shù)字電路的中間表示形式,重點關(guān)注寄存器之間的數(shù)據(jù)流以及對該數(shù)據(jù)執(zhí)行的操作。RTL 仿真用于在進入綜合和實現(xiàn)階段之前驗證設(shè)計的功能和性能。

常見的RTL仿真工具包括ModelSim、XSIM和VCS。這些工具允許設(shè)計人員執(zhí)行功能和時序仿真,這有助于在設(shè)計過程的早期識別和修復(fù)設(shè)計錯誤和性能瓶頸。

綜合與實施

在綜合階段,RTL 設(shè)計被轉(zhuǎn)換為門級網(wǎng)表,它代表使用門和觸發(fā)器的數(shù)字電路。此過程涉及優(yōu)化面積、速度和功耗的設(shè)計。常見的綜合工具包括 Xilinx Vivado、Intel Quartus 和 Synopsys Design Compiler。

實現(xiàn)階段涉及將門級網(wǎng)表映射到 FPGA 的資源,例如 CLB、DSP 切片和可編程互連。此步驟包括布局布線(確定 FPGA 上設(shè)計元素的物理位置)和比特流生成(創(chuàng)建配置 FPGA 的二進制文件)。實現(xiàn)工具包括 Xilinx Vivado 和 Intel Quartus。EDA(電子設(shè)計自動化)工具在 FPGA 設(shè)計流程中發(fā)揮著關(guān)鍵作用,可協(xié)助設(shè)計人員完成所有任務(wù),包括綜合、布局、布線和驗證。

測試和調(diào)試 FPGA 設(shè)計

測試和調(diào)試是 FPGA 設(shè)計過程中的關(guān)鍵步驟,確保設(shè)計正確運行并滿足性能要求。常見的測試方法包括:

- **仿真: **使用仿真工具在虛擬環(huán)境中測試設(shè)計,從而實現(xiàn)更快、更可控的測試。

- **在線測試: **在測試平臺或目標(biāo)硬件上測試 FPGA 設(shè)計,通常使用邏輯分析儀或示波器來監(jiān)控信號并識別問題。

調(diào)試 FPGA 設(shè)計涉及識別和修復(fù)與功能、性能和資源使用相關(guān)的問題。調(diào)試的最佳實踐包括:

- 使用描述性信號和變量名稱來提高代碼可讀性。

- 采用模塊化設(shè)計方法,將設(shè)計分解為更小、更易于管理的組件。

- 利用仿真工具和在線測試來識別和隔離問題。

通過遵循 FPGA 設(shè)計流程并采用測試和調(diào)試的最佳實踐,設(shè)計人員可以創(chuàng)建滿足其特定應(yīng)用要求的高質(zhì)量 FPGA 設(shè)計。

FPGA 設(shè)計實例和應(yīng)用

在本節(jié)中,我們將探討 FPGA 設(shè)計的各種示例和應(yīng)用。

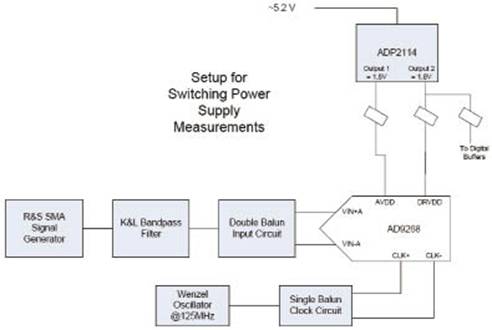

使用 FPGA 的數(shù)字信號處理 (DSP)

DSP 是對數(shù)字信號(例如音頻、視頻或傳感器數(shù)據(jù))的處理和分析。由于其并行性和靈活性,F(xiàn)PGA 非常適合 DSP 任務(wù)。基于 FPGA 的 DSP 應(yīng)用的一些示例包括:

- **音頻處理: **FPGA 可用于音頻效果、均衡、降噪和壓縮。

- **圖像處理: **FPGA 可以執(zhí)行實時圖像處理任務(wù),例如邊緣檢測、濾波和對象識別。

- **軟件定義無線電 (SDR): **FPGA 可用于實現(xiàn)各種無線電通信協(xié)議,從而實現(xiàn)高度可定制和適應(yīng)性強的無線電系統(tǒng)。

基于 FPGA 的人工智能 (AI) 機器學(xué)習(xí) (ML)

FPGA 在 AI 和 ML 應(yīng)用中發(fā)揮著重要作用,具有低延遲、高吞吐量和能源效率等優(yōu)勢。基于 FPGA 的機器學(xué)習(xí)和人工智能項目的一些示例包括:

- 深度學(xué)習(xí)加速器: 與傳統(tǒng)的基于CPU和GPU的解決方案相比,F(xiàn)PGA可用于加速深度神經(jīng)網(wǎng)絡(luò)的訓(xùn)練和推理,提高性能并降低功耗。

- 邊緣人工智能: FPGA 支持邊緣人工智能處理,減少數(shù)據(jù)傳輸?shù)皆贫说男枨螅⑻岣唠[私性和安全性。

- **定制 AI 硬件: **FPGA 允許實施針對特定應(yīng)用量身定制的定制 AI 算法,從而優(yōu)化性能和功效。

網(wǎng)絡(luò)和通信中的 FPGA

FPGA 廣泛應(yīng)用于網(wǎng)絡(luò)和通信系統(tǒng),具有高性能、靈活性和適應(yīng)性。基于 FPGA 的網(wǎng)絡(luò)和通信項目的一些示例包括:

- **網(wǎng)絡(luò)交換機和路由器: **FPGA可用于實現(xiàn)高性能、低延遲的以太網(wǎng)交換機和路由器,實現(xiàn)更快、更高效的數(shù)據(jù)傳輸。

- **光通信: **FPGA可用于光通信系統(tǒng),例如密集波分復(fù)用(DWDM),以實現(xiàn)高速數(shù)據(jù)傳輸和信號處理。

- **無線通信:**FPGA可用于實現(xiàn)各種無線通信協(xié)議,例如5G、Wi-Fi和藍(lán)牙,從而實現(xiàn)可定制和適應(yīng)性強的通信系統(tǒng)。

總之,F(xiàn)PGA 是多功能且功能強大的設(shè)備,可用于從數(shù)字信號處理到機器學(xué)習(xí)和網(wǎng)絡(luò)的廣泛應(yīng)用,其中微處理器的功能可能超出所需。通過利用 FPGA 的獨特功能,設(shè)計人員可以為各種行業(yè)和用例創(chuàng)建創(chuàng)新的高性能解決方案。

FPGA 設(shè)計最佳實踐

在本節(jié)中,我們將討論 FPGA 設(shè)計的一般最佳實踐,重點關(guān)注代碼可讀性、模塊化以及優(yōu)化性能、功耗和資源使用設(shè)計的技術(shù)。

代碼可讀性和模塊化

保持代碼可讀性和模塊化對于高效 FPGA 設(shè)計至關(guān)重要。通過遵循這些實踐,您可以提高設(shè)計的可維護性和可擴展性:

- **描述性命名: **為信號、變量和模塊使用有意義的名稱,使代碼更易于理解。

- **注釋: **包括注釋來解釋代碼的目的和功能,特別是對于復(fù)雜或不明顯的操作。

- 模塊化: 將您的設(shè)計分解為更小、更易于管理的模塊或組件。這種方法使調(diào)試、維護和重用代碼變得更加容易。

優(yōu)化 FPGA 設(shè)計的性能、功耗和資源使用

優(yōu)化 FPGA 設(shè)計可以幫助您在性能、功耗和資源使用之間實現(xiàn)所需的平衡。一些優(yōu)化技術(shù)包括:

- **流水線: **將復(fù)雜的操作分解為較小的階段并并行處理它們,以提高吞吐量并減少延遲。

- **資源共享: **重復(fù)使用硬件資源(例如乘法器、轉(zhuǎn)換器或內(nèi)存塊)進行多個操作,以節(jié)省面積和功耗。

- **時鐘門控: **禁用設(shè)計中未使用或空閑部分的時鐘域信號,以降低動態(tài)功耗。

除了這些技術(shù)之外,請務(wù)必利用綜合和實現(xiàn)工具(例如 Xilinx Vivado 和 Intel Quartus)提供的優(yōu)化功能。這些工具可以幫助您根據(jù)特定的設(shè)計要求和限制獲得最佳的結(jié)果。

通過遵循 FPGA 設(shè)計的最佳實踐并采用優(yōu)化技術(shù),您可以創(chuàng)建滿足特定應(yīng)用需求的高質(zhì)量、高效的設(shè)計。

常見問題 (FAQ)

- 使用 FPGA 的主要優(yōu)點是什么?

FPGA 提供靈活性、可重編程性、并行性和快速原型設(shè)計功能,使其適合廣泛的應(yīng)用。 - 如何為我的項目選擇合適的 FPGA?

為您的項目選擇 FPGA 時,請考慮 FPGA 系列、FPGA 供應(yīng)商、資源要求、性能需求和成本等因素。 - 我可以將 FPGA 用于機器學(xué)習(xí)和 AI 應(yīng)用嗎?

是的,F(xiàn)PGA 可用于機器學(xué)習(xí)和人工智能應(yīng)用,提供低延遲、高吞吐量和能源效率。 - VHDL 和 Verilog 之間有什么區(qū)別?

VHDL 是一種強類型、冗長的語言,具有較高的抽象級別,而 Verilog 是一種更簡潔、類似 C 的語言,具有較低的抽象級別。VHDL 和 Verilog 之間的選擇通常取決于個人喜好或行業(yè)標(biāo)準(zhǔn)。 - 開始 FPGA 設(shè)計需要哪些工具和軟件?

要開始 FPGA 設(shè)計,您需要 HDL 編輯器、仿真工具(例如 ModelSim、XSIM)、綜合工具(例如 Xilinx Vivado、Intel Quartus)和實現(xiàn)工具(例如 Xilinx Vivado、Intel Quartus)。

結(jié)論

在這本綜合指南中,我們探討了 FPGA 設(shè)計的基礎(chǔ)知識、設(shè)計流程、各種應(yīng)用以及創(chuàng)建高效、高質(zhì)量設(shè)計的最佳實踐。通過了解 FPGA 的工作原理并利用其提供的獨特功能,設(shè)計人員可以為各種行業(yè)和用例創(chuàng)建創(chuàng)新的解決方案。

電子發(fā)燒友App

電子發(fā)燒友App

評論