數字電路分為組合( combinational)電路和時序(sequential)電路。組合電路的輸出僅取決于它的輸入,時序電路的輸出取決于當前的輸入和之前的輸入。組合電路是不需要記憶的,但時序電路有記憶功能。

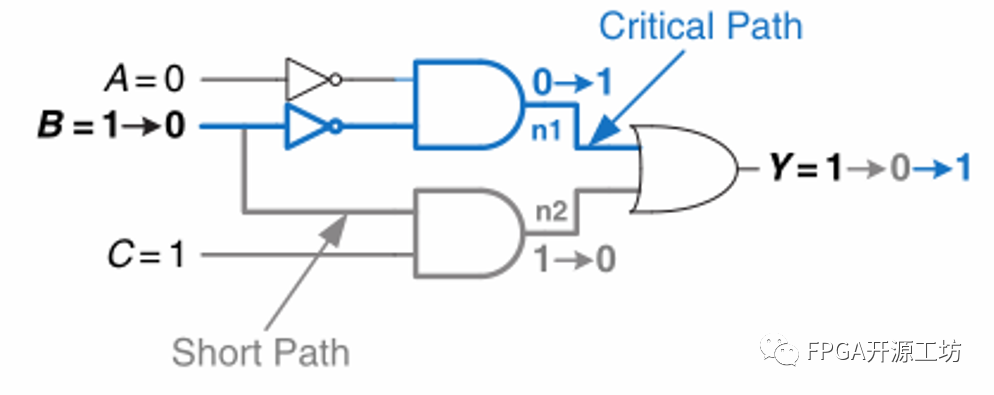

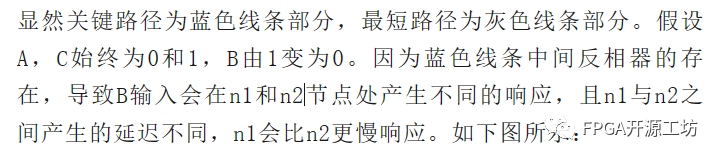

在紅色方框處會因為n1n2響應時間的延遲不同導致 OR門產生一個本不期望出現的低電平。盡管很短暫,但在復雜電路中該現象還是會影響某些破壞性的效果。

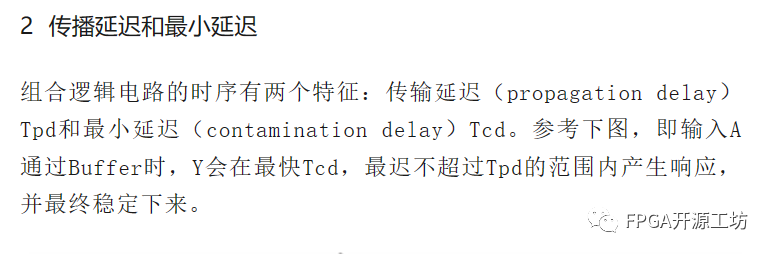

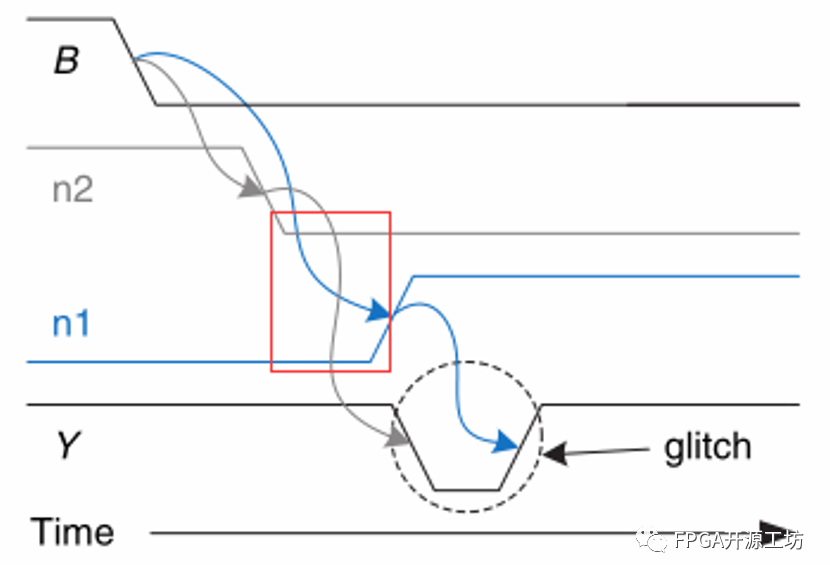

為了防止毛刺出現我們可以修改電路,原因與本節內容無關,所以不展開:

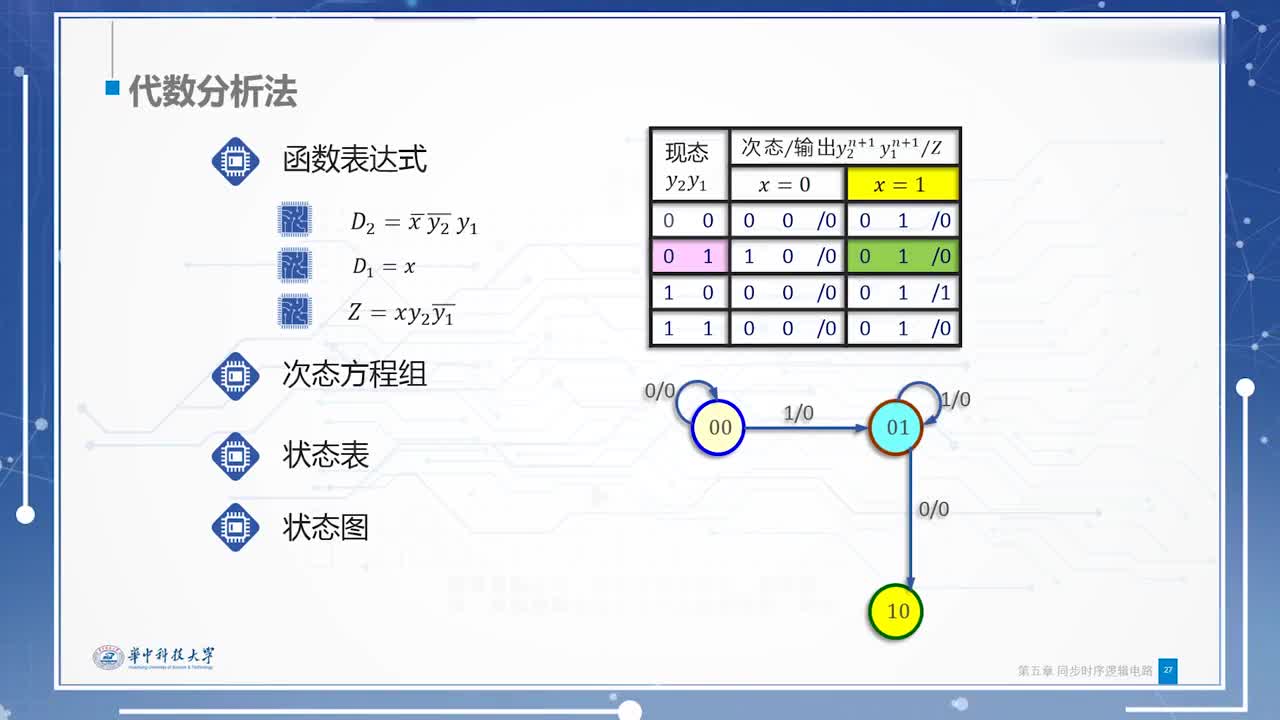

(二)??時序邏輯電路

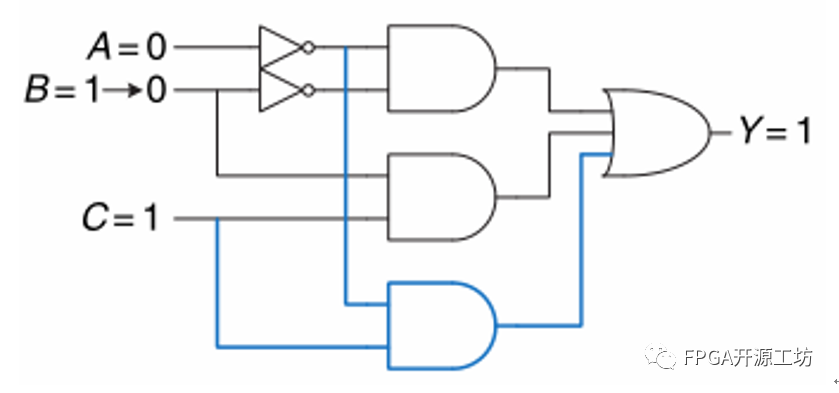

前面提過,時序邏輯電路的輸出響應同時取決于當前的輸入與之前的輸入狀態,所以需要一個存儲器件保存之前的出入狀態。存儲元器件的基本模塊為一個雙穩態(bistable)的元件。該元件需要有兩種穩定的狀態,即0和1。我們首先可以想到將兩個反相器(非門)交叉耦合(cross coupled),即可形成一個最簡單的雙穩態電路。

我們可以假設Q為0或1,都可以發現輸出始終保持穩定。但是該器件有兩個問題:

無法確定Q和~Q的初始值;

沒有出入信號。

我們在此基礎上需要逐步修改出有實際意義的存儲器件。本節關注點在時序分析,所以不做詳細分析,只需要抽象化知道功能即可。

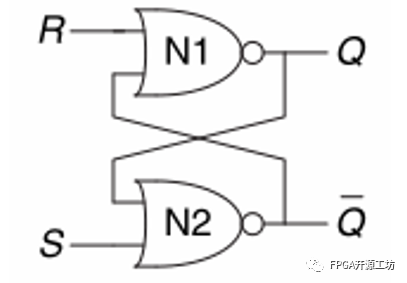

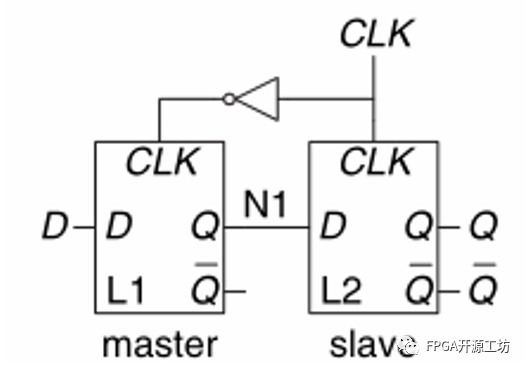

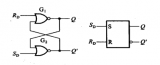

1.????SR鎖存器

將非門改為或非門,即SR鎖存器。

它有置位(SET)和復位(RESET)兩個輸入信號,以此控制Q的輸出。真值表如下:

當S和R均為0時,Q可以保存之前的狀態。Q也可以通過S和R來控制。但是SR鎖存器并沒有引入時鐘的概念,即它無法決定什么時間來控制Q的狀態。

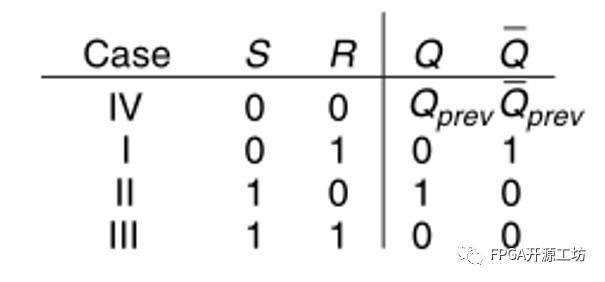

2.????D鎖存器

引入CLK,和D信號來決定在何時根據D的狀態來控制輸出Q電路和真值表如下圖:

由真值表可知D鎖存器(Latch)是電平敏感的,當CLK=1時,Q=D,當CLK=0時,Q保持之前的狀態,無視D的變化。

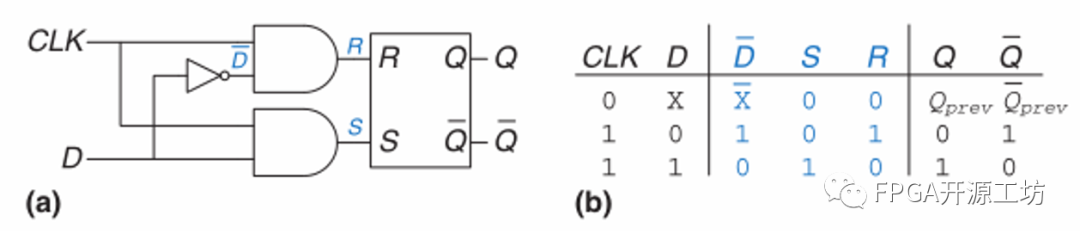

3.????D觸發器(filpflop)

我們使用兩個由反向時鐘控制的D Latch級聯(背靠背,back to back)組成DFF,因為反向時鐘的作用可以使時鐘電平敏感變為邊沿敏感,電路如下圖:

DFF在時鐘的上升沿將D賦值給Q,在其它時刻Q保持不變。DFF也常常被稱為主從觸發器,邊沿觸發器,正邊沿觸發器。

4.????寄存器

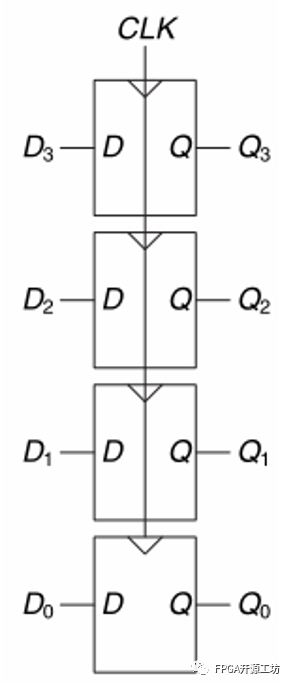

將N個共享同一時鐘的DFF并聯即為N位寄存器,如圖:

5.????時序邏輯電路的時序

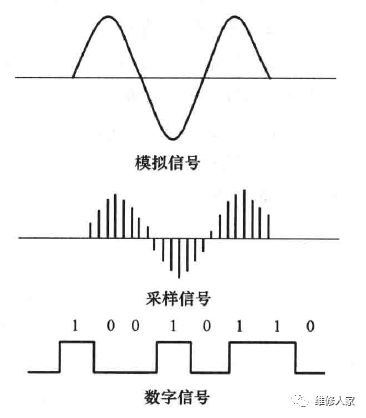

當觸發器或寄存器在時鐘上升沿到達時將D的值賦給Q,這個過程稱之為采樣(sampling)。當時鐘上升沿時,如果D是0或者1的穩定狀態,那么Q也會輸出一個穩定的對應值。但如果運氣不好,在時鐘上升沿,輸入D正處于變化狀態(比如一個0-1上升的過程中),那么Q的值將不確定。所以對于Latch和FF我們都有一個約束,即建立時間(setup time)和保持時間(hold time)。

即在時鐘上升沿到來之前Tsetup,輸入信號必須穩定,且保持到上升沿到來之后Thold時刻。也就是在Tsetup和Thold時刻之間,必須確保輸入D保持穩定,才能使Q采樣成功。

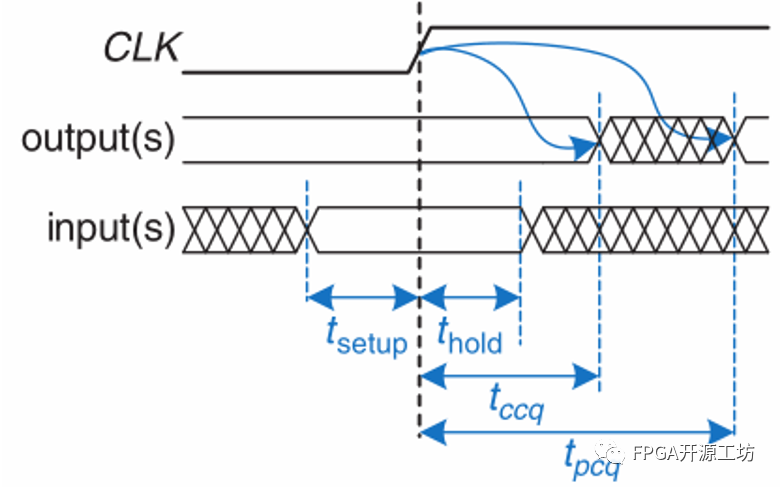

a)???觸發器的動態規范(dynamic discipline)

同組合邏輯一樣,電子在任何電路元器件傳播均需要時間,在latch和FF中也不例外,如下圖所示。當時鐘上升沿到來,采樣輸入值后,會經過最短延遲Tccq(Time for ff Contamination Clk-to-Q delay),輸出才會發生變化,最遲在Tpcq(flip-flop PropagationClk-to-Q delay)之前穩定下來。

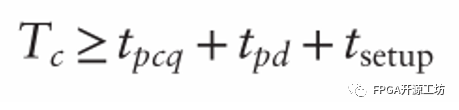

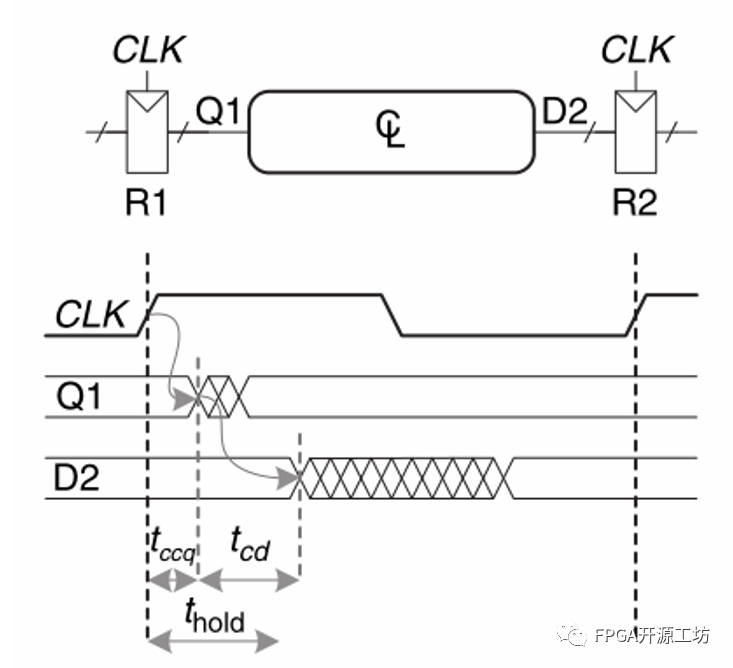

b)???建立時間約束

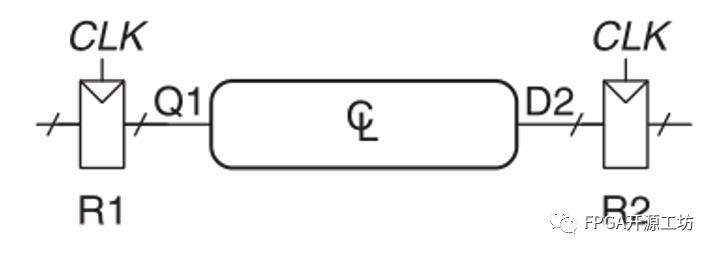

以一個簡單的時序邏輯電路(reg to reg)為例,如下圖所示:

數據從R1輸出的Q1開始,經過一個未知的組合邏輯電路并輸出D2,進入R2,其中R1和R2的CLK為同一時鐘且不考慮布線差異。

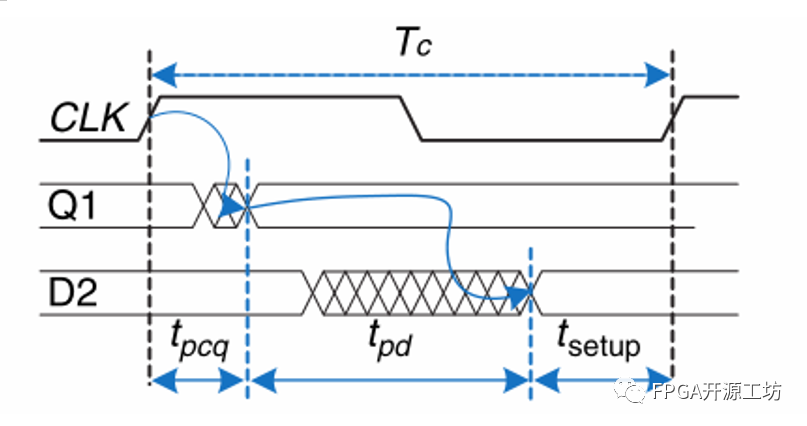

如以上時序圖所示,時鐘周期為Tc,在一個Cycle內,

我們首先看Q1:

Q1來自寄存器R1的輸出,所以Q1必定是不穩定的,看5.a那張時序圖,Q1會在第一個CLK的上升沿到來后Tccq和Tpcq之間的某個時間穩定下來,具體時間不知道也不重要,反正我們可以確定最遲Tpcq肯定是穩定的。

隨后穩定的Q1會進入組合邏輯電路,最遲經過Tpd時刻穩定下來并輸出(不記得Tpd是什么的往前面翻翻,注意要區別于Tpcq),如果這個時刻處在第2個CLK上升沿Tsetup之前,那么第2個CLK就能夠順利采樣。

我們就稱這種情況為滿足建立時間約束。我們可以很容易得到一個等式:

在正常的數字電路系統設計中,系統時鐘周期通常由架構師、市場部門決定(以確保產品有足夠的性能和競爭力)。或者由設計者本人確定,反正鍵盤在你手里,你是老大你說了算。Tpcq和Tsetup這是由制造工藝決定的,越先進的制程則延遲越小(或者你是用fpga做產品,那么fpga的型號決定了這兩個時鐘參數)。所以通常對于設計者來說,為了滿足建立時間,你能修改的或者說決定的只有Tpd,即組合邏輯電路的傳播延遲。所以我們可以將上述公式變換為:

括號內的項Tpcq+Tsetup我們稱之為時序開銷,反正這是一個由制造工藝或者芯片型號決定的固定值。我們想要Tc更短(時鐘頻率更快),就要確保組合邏輯的傳播延遲不能太大。如果代碼是固定的(比如用的ip),組合邏輯的傳播延遲沒辦法縮減,那么就只能降低時鐘頻率(增大Tc)。

減少組合邏輯的傳播延遲主要辦法就是減少邏輯的關鍵路徑上的門電路的數量,如果是fpga的話就是減少lut的級聯級數。

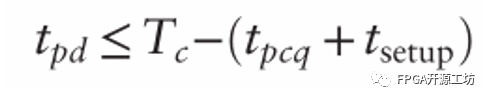

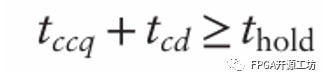

c)???保持時間約束

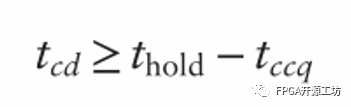

同樣關注目的寄存器(destination)R2,R2采樣的輸入信號是D2,D2來自于經過組合邏輯電路的Q1,Q1來自R1的輸出,且在Tccq之前都是穩定的(即使R1的輸入變化導致Q1變化,最快也要等到Tccq之后,沒想明白的看5.a),在經過組合邏輯電路之后,同理也會在Tcd之前保持穩定,為了確保在Thold之間D2都是穩定的, 會得到下列公式:

同樣Tccq和Thold都是由觸發器的制造工藝決定的,所以我們可以變化等式得到:

也就是組合邏輯的最小延遲Tcd的值。我們從公式可以發現,滿足保持時間約束與系統時鐘周期無關,僅與組合邏輯的最小延遲有關。

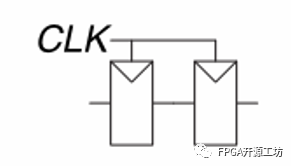

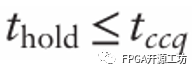

在實際電路中,我們有一種情況是2個觸發器直接級聯,中間不經過任何組合邏輯電路:

也就是Tcd=0,所以

換句話說就是一個可靠觸發器的保持時間必定要小于它的最小延遲時間。在實際的數字IC設計中,因為Tcd=0這種情況都能滿足,那加了組合邏輯電路Tcd>0必定不會出現不滿足的情況。但是因為我們的例子中沒有考慮CLK的時鐘抖動,以及CLK時鐘同源但是布線長度不同而導致的偏移,所以實際也會出現Tcd<0的情況。但是作為前端設計不會關注保持時中違例,而是在用工具生成時序分析報告后由后端通過插入Buffer來處理。在在FPGA設計中,時序分析會在綜合和實現兩個步驟分別產生,如果綜合的時序報告中有保持時間違例一般不做處理(如果違例太大就需要考慮提前進行處理了),工具會在實現的布局布線階段自動fix違例。如果布局布線后的時序報告依舊有保持時間違例,一般小于300ps的不做處理,因為工具計算的時候往往是用最差策略來計算的。如果違例數值過于大的話,就要考慮修改代碼,或者通過ECO的方式修改時鐘BUFF位置,減少時鐘偏移。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論