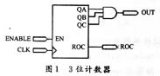

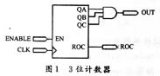

目前主流的FPGA仍是基于查找表技術(shù)的,已經(jīng)遠(yuǎn)遠(yuǎn)超出了先前版本的基本性能,并且整合了常用功能(如RAM、時鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個示意圖,實(shí)際上

2022-10-25 09:01:05 1822

1822 FPGA 設(shè)計的四種常用思想與技巧FPGA設(shè)計的四種常用思想與技巧 討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD 邏輯設(shè)計

2012-08-11 10:30:55

(18)FPGA串/并轉(zhuǎn)換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉(zhuǎn)換的思想5)結(jié)語1.2 FPGA簡介FPGA(Field

2022-02-23 07:38:28

FPGA重要的設(shè)計思想

2013-01-05 13:52:27

我想在fpga上做一個報文解析的功能,就是將一串01數(shù)據(jù)發(fā)送給FPGA,然后fpga對數(shù)據(jù)進(jìn)行報文解析,然后再將解析后的數(shù)據(jù)發(fā)送給電腦,想問各位大神解析模塊應(yīng)該怎么寫?有沒有相關(guān)的資料可以參考的???急求???

2017-11-13 16:04:16

FPGA基本原理及設(shè)計思想和驗證方法看完你就懂了

2021-09-18 07:08:52

本帖最后由 jiuri1989 于 2012-2-10 11:42 編輯

本系列討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA

2012-02-10 11:40:52

今天給大俠帶來FPGA設(shè)計基本原則及思想,話不多說,上貨。FPGA設(shè)計基本原則及思想一、硬件設(shè)計基本原則1、速度與面積平衡和互換原則:一個設(shè)計如果時序余量較大,所能跑的頻率遠(yuǎn)高于設(shè)計要求,能可以通過

2020-10-11 12:26:42

本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD

2011-10-20 09:12:36

FPGA設(shè)計的四種常用思想與技巧

2012-08-20 17:16:35

;

四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得

2010-11-01 13:17:36

FPGA設(shè)計重要思想個人感覺一般,是個培訓(xùn)ppt,但是思想還是要有的

2014-11-14 17:39:17

`FPGA設(shè)計(設(shè)計思想與技巧)經(jīng)典資料 免費(fèi)奉送<br/>`

2009-08-15 16:53:28

FPGA重要設(shè)計思想及工程應(yīng)用之時序及同步設(shè)計希望對大家有用

2016-04-24 22:31:46

fpga教程之FPGA設(shè)計流程《Verilog HDL 程序設(shè)計教程》fpga教程之FPGA 設(shè)計的四種常用思想與技巧QuartusII教程之QuartusII警告信息解析QuartusII教程之

2010-06-21 14:59:01

本帖最后由 lee_st 于 2018-3-4 01:08 編輯

深入解析WINDOWS操作系統(tǒng)(第4版)

2018-03-02 23:45:22

深入解析傳感器網(wǎng)絡(luò)中實(shí)時通信的研究

2021-05-26 06:00:09

深入了解LabVIEW FPGA

2015-05-27 08:35:11

深入淺出玩轉(zhuǎn)FPGA

2012-07-21 09:21:08

深入淺出玩轉(zhuǎn)FPGA,作者吳厚航,由北京航空航天大學(xué)出版社出版。本書收集整理了作者在FPGA學(xué)習(xí)和實(shí)踐中的經(jīng)驗點(diǎn)滴。書中既有日常的學(xué)習(xí)筆記,對一些常用設(shè)計技巧和方法進(jìn)行深入探討;也有很多生動的實(shí)例

2012-02-27 10:45:37

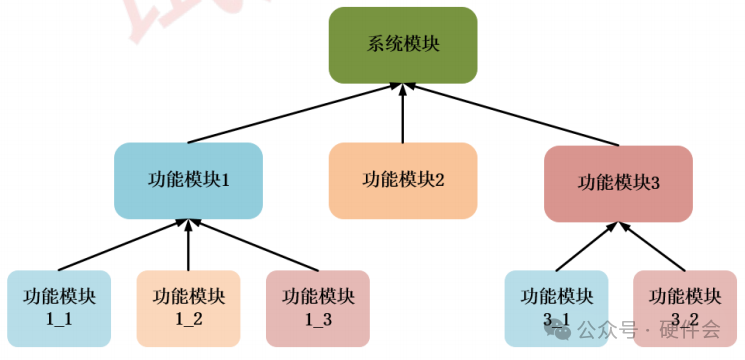

多頁原理圖繪制方法:采用垂直分割,而此處的模塊也可能是由幾個更基礎(chǔ)的模塊構(gòu)成,一路延續(xù)下去,就形成金字塔型的層次化結(jié)構(gòu)。如下圖: 在AltiumDesigner里面的形式如下圖: Sheet2

2019-09-06 15:48:55

本帖最后由 eehome 于 2013-1-5 10:03 編輯

NAND閃存深入解析

2012-08-09 14:20:47

使用labview設(shè)計模式深入解析ppt:[hide][/hide]labview設(shè)計模式深入解析DEMO:[hide] [/hide]

2011-12-28 16:10:21

、邏輯復(fù)制與模塊復(fù)用五、模塊化設(shè)計六、時鐘設(shè)計技巧筆記8 基于FPGA的跨時鐘域信號處理一、同步設(shè)計思想二、單向控制信號檢測三、專用握手信號四、搞定亞穩(wěn)態(tài)五、借助于存儲器第三部分仿真測試筆記9 簡單

2017-02-04 17:06:09

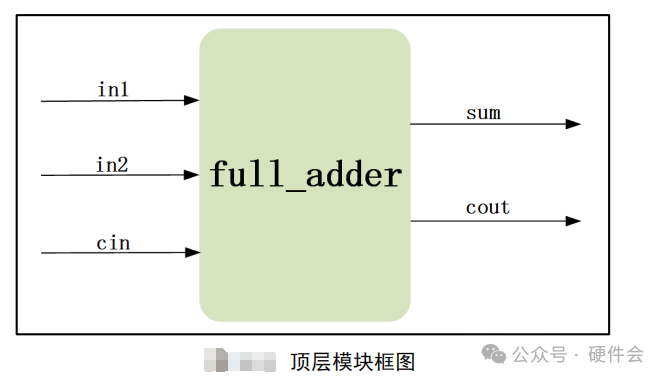

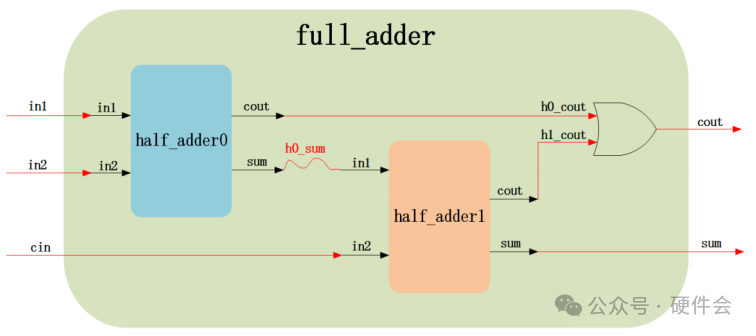

,力求深入淺出,簡單易懂涵蓋從基本邏輯電路設(shè)計到DSP模塊設(shè)計,再到基于軟核處理器的設(shè)計列舉大量實(shí)例講解難于理解的內(nèi)容,并給出詳細(xì)說明和實(shí)現(xiàn)步驟著力貫徹自頂向下的設(shè)計思路,培養(yǎng)層次化和模塊化的設(shè)計思想

2012-05-08 15:21:24

、乒乓操作及串/并轉(zhuǎn)換設(shè)計三、流水線設(shè)計四、邏輯復(fù)制與模塊復(fù)用五、模塊化設(shè)計六、時鐘設(shè)計技巧筆記8 基于FPGA的跨時鐘域信號處理一、同步設(shè)計思想二、單向控制信號檢測三、專用握手信號四、搞定亞穩(wěn)態(tài)五

2017-06-15 17:46:23

的衍生),一步一步帶領(lǐng)大家入門fpga開發(fā),為后續(xù)深入學(xué)習(xí)打下良好的基礎(chǔ)。希望大家觀看并積極提出建議和意見,小梅哥將評選出評論最有價值的前三名,每人獎勵20元話費(fèi),并隨機(jī)再抽取5名參與回復(fù)的筒子,獎勵20

2015-05-24 20:15:22

目推薦】小梅哥和你一起深入學(xué)習(xí)FPGA之DAC驅(qū)動眾籌相關(guān)內(nèi)容專區(qū):01【芯航線FPGA學(xué)習(xí)平臺眾籌進(jìn)度帖】小梅哥FPGA學(xué)習(xí)筆記之Verilog語法基礎(chǔ)講解之參數(shù)化設(shè)計02【芯航線FPGA學(xué)習(xí)平臺眾籌

2015-09-16 20:33:30

一個設(shè)計的時序要求很高,普通方法達(dá)不到設(shè)計頻率,那么可以通過數(shù)據(jù)流串并轉(zhuǎn)換,并行復(fù)制多個操作模塊,對整個設(shè)計采用“乒乓操作”和“串并轉(zhuǎn)換”的思想進(jìn)行處理,在芯片輸出模塊處再對數(shù)據(jù)進(jìn)行“并串轉(zhuǎn)換”。從而

2019-07-17 08:00:00

` 本帖最后由 小梅哥 于 2016-1-18 13:02 編輯

大家好,今天,小梅哥繼續(xù)連載本人精心錄制和編輯的FPGA學(xué)習(xí)系列教程——《小梅哥FPGA設(shè)計思想與驗證方法視頻教程

2015-12-28 17:11:57

本帖最后由 小梅哥 于 2016-1-18 13:00 編輯

大家好,今天,小梅哥繼續(xù)連載本人精心錄制和編輯的FPGA學(xué)習(xí)系列教程——《小梅哥FPGA設(shè)計思想與驗證方法視頻教程》。教程充分考慮

2015-11-11 09:15:48

` 本帖最后由 小梅哥 于 2016-1-18 13:02 編輯

大家好,今天,小梅哥繼續(xù)連載本人精心錄制和編輯的FPGA學(xué)習(xí)系列教程——《小梅哥FPGA設(shè)計思想與驗證方法視頻教程

2015-12-28 16:57:49

` 本帖最后由 小梅哥 于 2016-1-18 13:01 編輯

大家好,今天,小梅哥繼續(xù)連載本人精心錄制和編輯的FPGA學(xué)習(xí)系列教程——《小梅哥FPGA設(shè)計思想與驗證方法視頻教程

2015-12-16 09:11:00

`小梅哥和你一起深入學(xué)習(xí)FPGA高手問答第17期小編導(dǎo)讀: 本期高手問答(11.21~12.5)邀請到了《FPGA與大學(xué)EDA教學(xué)》、《FPGA在電子設(shè)計大賽中的應(yīng)用》的作者小梅哥, 梅工,論壇

2014-11-21 14:47:53

`例說FPGA連載44:DDR控制器集成與讀寫測試之Verilog代碼解析特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實(shí)例有8個

2016-11-08 18:18:29

`例說FPGA連載96:基于HDMI的AV采集顯示之Verilog代碼解析特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 本實(shí)例分為4個

2017-04-30 10:12:01

用PADS Logic畫原理圖的時候,創(chuàng)建了一個MCU模塊的層次化符號,如下圖。我想把P46連接到鍵盤模塊的PS2_DAT管腳上,于是把與P46連接的網(wǎng)絡(luò)改成PS2_DAT,結(jié)果奇怪的事出來了,層次

2014-03-08 12:22:26

單片機(jī) C語言 深入解析含一些優(yōu)化問題

2012-11-26 21:36:58

/u/97edd21e88 本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD 邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想

2019-07-03 08:30:00

四種常用的FPGA設(shè)計思想與技巧

2017-11-05 15:03:29

四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得

2020-05-01 07:00:00

本節(jié)我們通過驅(qū)動流水燈的不同方式來體現(xiàn)Fpga中的一個重要思想—層次化設(shè)計。首先介紹一下我所使用開發(fā)板的硬件資源,50MHZ時鐘輸入、4個低電平點(diǎn)亮的流水燈。然后通過兩種不同驅(qū)動方式的對比使讀者更加深層次

2015-06-18 10:20:24

本帖最后由 小梅哥 于 2015-6-15 22:18 編輯

各位喜愛FPGA技術(shù)的小伙伴。小梅哥FPGA設(shè)計思想與驗證方法視頻教程的課程大綱已經(jīng)出爐,歡迎大家根據(jù)自己的實(shí)際感受,提出各種批評

2015-06-15 22:01:45

看了《小梅哥和你一起深入學(xué)習(xí)FPGA之FPGA設(shè)計流程》受益匪淺,所以做個pdf方便大家。

2015-02-04 09:39:22

嵌入式系統(tǒng)硬件抽象層(HAL & BSP)的設(shè)計思想1 前言1.1 層次化思想1.2 模塊化思想1.3 對象化思想2 板級支持包(BSP)3 嵌入式系統(tǒng)硬件抽象層的原理3.1 硬件抽象層

2022-02-11 07:49:54

本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD 邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得事半功倍的效果。

2021-04-29 06:04:14

的體系結(jié)構(gòu)非常重要。將CPU、GPU、FPGA和專門的加速器結(jié)合在一起,可以讓Intel和它的客戶聰明而高效地解決問題。 第三個層次 軟件同質(zhì)化 第三種異構(gòu)集成是在軟件級別。這個很難。英特爾的方法

2020-07-07 11:44:05

。很欣賞Altium安裝目錄下給的例子,層次化設(shè)計十分美觀大方。比如這樣:搜索了很久,沒有搜索到滿意的回答,關(guān)于怎么在Cadence中實(shí)現(xiàn)層次化設(shè)計。然后花了一天摸索,并總結(jié)如下:...

2021-11-12 08:55:01

模塊化編程思想

2014-06-24 10:09:57

自動化測試一般是指軟件測試的自動化,軟件測試就是在預(yù)設(shè)條件下運(yùn)行系統(tǒng)或應(yīng)用程序,評估運(yùn)行結(jié)果,預(yù)先條件應(yīng)包括正常條件和異常條件。本文介紹的是自動化測試框架思想與構(gòu)建,一起來看。

2019-07-18 06:52:46

本帖最后由 eehome 于 2013-1-5 10:05 編輯

《深入淺出玩轉(zhuǎn)FPGA》有書,有視頻,有開發(fā)板,非常適合自學(xué)。而且作者根據(jù)自己的實(shí)踐經(jīng)驗寫出來的書,很實(shí)在。初學(xué)者建議看

2012-02-03 11:11:35

至芯科技之a(chǎn)ltera 系列FPGA教程 第三篇 數(shù)字系統(tǒng)設(shè)計思想方法

2016-08-11 03:16:17

ROM實(shí)例8.2.1功能概述8.2.2代碼解析8.2.3ROM初始化文檔創(chuàng)建8.2.4新建源文件8.2.5IP選擇8.2.6ROM配置8.2.7Xilinx庫設(shè)置8.2.8功能仿真8.2.9FPGA在線

2017-11-27 12:23:53

跪求《深入淺出玩轉(zhuǎn)FPGA(第2版)》這本書電子版

2015-10-08 07:44:27

說起阻抗控制,很多人都是一臉的輕描淡寫:這么簡單,我剛?cè)胄芯蜁恕T?b class="flag-6" style="color: red">深入了解行業(yè)在設(shè)計中進(jìn)行阻抗控制的方法之后,我總結(jié)了4個層次。第0層次,不進(jìn)行阻抗控制。也分兩種,一種是設(shè)計不屬于高速范疇,不需要

2016-07-25 18:33:34

對于大規(guī)模分布式數(shù)據(jù)挖掘問題,提出一種基于移動代理的層次結(jié)構(gòu)挖掘模型,該模型對OIKI DDM模型進(jìn)行擴(kuò)展,利用層次設(shè)計思想,基于移動代理和增量優(yōu)化技術(shù)進(jìn)行挖掘和增量集

2009-05-11 20:28:38 19

19 本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)

2009-10-29 21:55:44 55

55 本文摒棄了以往利用斷點(diǎn)集來進(jìn)行離散化的算法思想,提出了一種新的基于粗糙集和分裂的層次聚類的全局離散化算法。本算法在層次聚類的基礎(chǔ)上考慮不同連續(xù)屬性離散化結(jié)果

2009-12-29 17:15:00 3

3 FPGA設(shè)計思想與技巧:這一部分主要介紹FPGA/CPLD設(shè)計的指導(dǎo)性原則,如FPGA 設(shè)計的基本原則、基本設(shè)計:思想、基本操作技巧、常用模塊等。FPGA/CPLD設(shè)計的基本原則、思想、技巧和常用模

2010-01-11 09:00:37 34

34 FPGA重要設(shè)計思想及工程應(yīng)用之時序及同

在FPGA設(shè)計中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設(shè)計項目中的每一個觸發(fā) 器

2010-02-09 10:29:36 51

51 FPGA重要設(shè)計思想及工程應(yīng)用之乒乓操作

“ 乒乓操作” 是一個常常應(yīng)用于數(shù)據(jù)流控制的處理技巧,典型的乒乓操作的處理技巧。

2010-02-09 10:51:52 44

44 FPGA重要設(shè)計思想及工程應(yīng)用之流水線設(shè)

流水線設(shè)計是高速電路設(shè)計中的一 個常用設(shè)計手段。如果某個設(shè)計的處理流程分為若干步驟,而且整個數(shù)據(jù)處理 流程分

2010-02-09 11:02:20 52

52 “Diebold XFS服務(wù)”源代碼級深入解析

這篇文章的目的是記錄一下我分析“Diebold XFS服務(wù)”軟件是怎樣實(shí)現(xiàn)的過程。當(dāng)然,我是沒有Diebold軟件的源代碼的,也沒看

2010-02-09 14:50:12 16

16 存儲器的層次結(jié)構(gòu)原理圖解分析

學(xué)習(xí)目錄:

理解多級存儲層次的思想及其作用;

掌

2010-04-13 16:16:12 12759

12759 本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的

2010-11-04 10:11:28 627

627

本文從FPGA的原理結(jié)構(gòu)的角度探討了產(chǎn)生毛刺的原因及產(chǎn)生的條件,在此基礎(chǔ)上,總結(jié)了多種不同的消除方法,在最后結(jié)合具體的應(yīng)用對解決方案進(jìn)行深入的分析。

2011-08-03 11:48:15 1942

1942

電子發(fā)燒友提供了電視發(fā)射機(jī)原理深入解析教材,本PPT介紹了電視發(fā)射機(jī)原理圖,電視發(fā)射機(jī)工作原理,數(shù)字電視發(fā)射機(jī)工作指標(biāo)等信息。

2011-12-09 11:01:33 0

0 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進(jìn)行 FPGA 設(shè)計的簡介

2016-01-06 11:32:55 65

65 FPGA開發(fā)流程及編程思想,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-01-18 15:17:27 31

31 FPGA和CPLD的區(qū)別,以及設(shè)計思路思想

2016-02-17 11:20:56 38

38 FPGA重要設(shè)計思想及工程應(yīng)用之時序及同步設(shè)計

2016-05-10 11:24:33 16

16 FPGA學(xué)習(xí)資料教程——深入淺出玩轉(zhuǎn)FPGA 第二版,資源過大,共分為4部分上傳。感興趣的小伙伴們可以去我上傳的資源里一起下載解壓打開。

2016-09-06 16:52:29 0

0 FPGA學(xué)習(xí)資料教程——深入淺出玩轉(zhuǎn)FPGA 第二版,資源過大,共分為4部分上傳。感興趣的小伙伴們可以去我上傳的資源里一起下載解壓打開。

2016-09-06 16:52:29 0

0 FPGA學(xué)習(xí)資料教程——深入淺出玩轉(zhuǎn)FPGA 第二版,資源過大,共分為4部分上傳。感興趣的小伙伴們可以去我上傳的資源里一起下載解壓打開。

2016-09-06 16:52:29 0

0 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-myosctest

2016-10-27 18:20:05 5

5 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-uartverilog

2016-10-27 18:20:05 6

6 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-UFTtest

2016-10-27 18:20:05 4

4 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-keyscanverilog

2016-10-27 18:20:05 8

8 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-johnsonverilog

2016-10-27 18:20:05 8

8 《深入淺出玩轉(zhuǎn)FPGA》基于EPM240的入門實(shí)驗-clkdivverilog

2016-10-27 18:20:05 4

4 《深入淺出玩轉(zhuǎn)FPGA》光盤資料-項目應(yīng)用logic_analysis

2016-10-27 18:07:54 8

8 FPGA_設(shè)計的四種常用思想與技巧,下來看看

2016-12-17 21:16:26 17

17 深入解析ARM Cortex-A12架構(gòu)

2017-01-14 12:31:49 21

21 無線充電相關(guān)原理的深層次解析

2017-01-12 22:05:28 30

30 STM32的USB庫深入解析

2017-10-15 09:21:33 87

87 Vivado HLS配合C語言等高級語言能幫助您在FPGA上快速實(shí)現(xiàn)算法。 高層次綜合(HLS)是指自動綜合最初用C、C++或SystemC語言描述的數(shù)字設(shè)計。工程師之所以對高層次綜合如此感興趣,不僅是因為它能讓工程師在較高的抽象層面上工作,而且還因為它能方便地生成多種設(shè)計解決方案。

2019-10-06 10:44:00 1180

1180

本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工

2017-12-02 11:30:04 7155

7155

FPGA設(shè)計中,層次結(jié)構(gòu)設(shè)計和復(fù)位策略影響著FPGA的時序。在高速設(shè)計時,合理的層次結(jié)構(gòu)設(shè)計與正確的復(fù)位策略可以優(yōu)化時序,提高運(yùn)行頻率。

2019-02-15 15:15:53 849

849 FPGA/CPLD 的設(shè)計思想與技巧是一個非常大的話題,由于篇幅所限,本文僅介紹一些常用的設(shè)計思想與技巧, 包括乒乓球操作、串并轉(zhuǎn)換、流水線操作和數(shù)據(jù)接口的同步方法。希望本文能引起工程師們的注意, 如果能有意識地利用這些原則指導(dǎo)日后的設(shè)計工作,將取得事半功倍的效果!

2020-10-22 17:57:29 9

9 ARM與FPGA的接口實(shí)現(xiàn)的解析(應(yīng)廣單片機(jī))-該文檔為ARM與FPGA的接口實(shí)現(xiàn)的解析詳述資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-22 09:47:55 14

14 (18)FPGA串/并轉(zhuǎn)換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉(zhuǎn)換的思想5)結(jié)語1.2 FPGA簡介FPGA(Field

2021-12-29 19:40:56 2

2 都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得事半功倍的效果。

2023-05-18 08:56:57 352

352

電子發(fā)燒友網(wǎng)站提供《使用Vivado高層次綜合(HLS)進(jìn)行FPGA設(shè)計的簡介.pdf》資料免費(fèi)下載

2023-11-16 09:33:36 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論