開發方面的能力,每一個章節中都有針對性的代碼書寫以及代碼的講解,可作為讀者參考。 第一章:模塊書寫 Verilog HDL 語言的基本語法與 C語言相似,因此與 VHDL 相比較更容易上手。本章將會在實際小項目的基礎上,以 Verilog HDL 語言為主, 教讀者怎么更方便、更高效的

2020-11-13 16:02:12 3510

3510

優秀的 Verilog/FPGA開源項目介紹(三十四)- PDM音頻接口設計及信號處理 ? 緒論 今天介紹幾個與PDM接口相關的開源項目。 FPGA使用Delta-sigma ADC實現PDM音頻

2022-10-17 09:10:33 2241

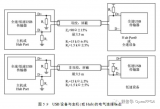

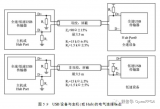

2241 本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 886

886

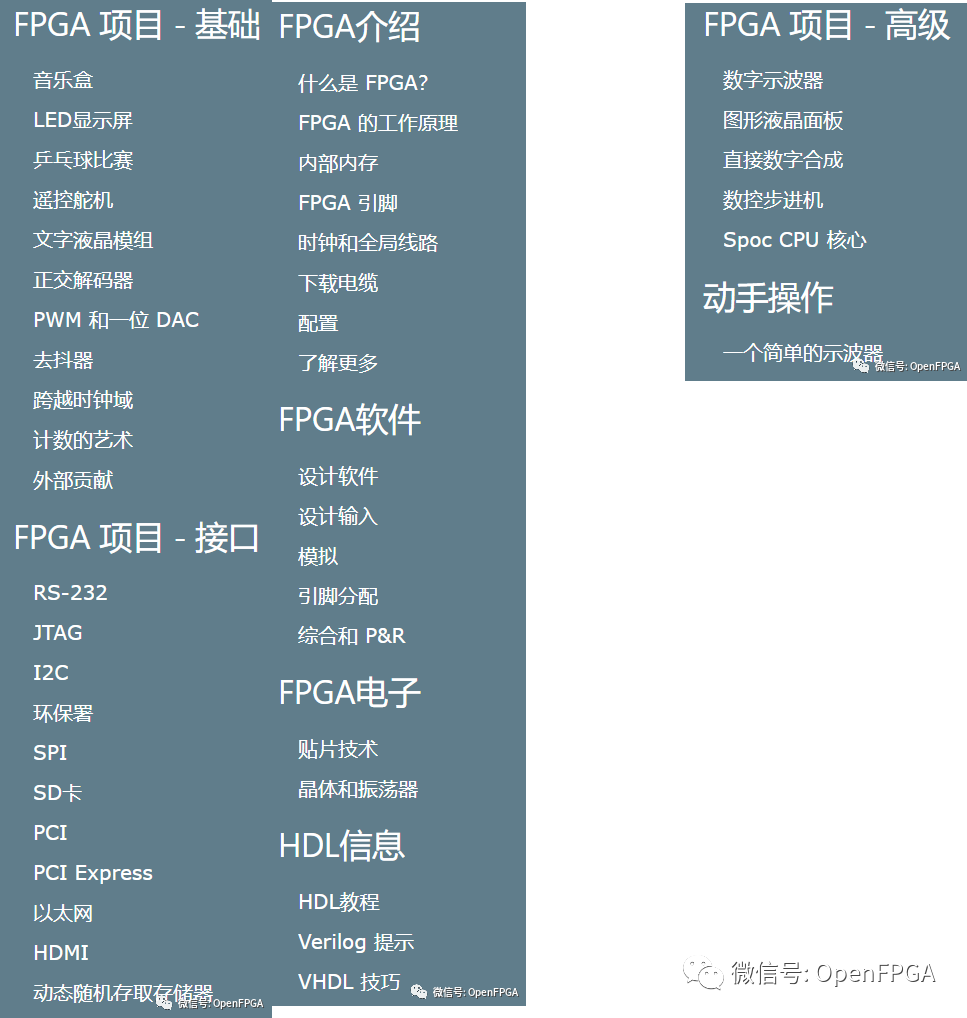

websitehttp://www.opencores.org - 中文2. FPGAs are fun提供了大量的關于FPGA應用的文章,項目實際例子。強烈推薦http://www.fpga

2015-11-20 12:35:44

FPGA、CPLD常用protel庫FPGA&CPLD_LIB.ddb

2012-08-11 10:32:00

FPGA、CPLD常用protel庫(密碼:allyoudianzi )

2012-08-20 18:03:32

FPGA上對OC8051IP核的修改與測試FPGA上對OC8051IP核的修改與測試單片機與嵌入式系統 解放軍信息工程大學 楊先文 李崢引 言20世紀80年代初,Intel公司推出了MCS-51

2012-08-11 11:41:47

學習。catena-riscv32-fpgaRISC-V這么火,怎么能沒有音頻,這個項目就是用在RISC-V系統里的音頻IP,詳細的地址如下:總結今天介紹的基于PDM項目,分為實現和處理兩部分。原作者:碎碎思

2022-10-17 15:20:28

商店的IP核庫中索取組件進行配置,最后像搭積木一樣完成一個項目,或者整個設計都不需要見到一句代碼。當然了,未來什么情況都有可能發生,但是底層的代碼邏輯編寫方式無論如何還是有其生存空間的,畢竟一個個IP

2015-01-29 09:20:41

可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節課程學習,學員可以設計一些簡單的FPGA程序,掌握組合邏輯和時序邏輯電路的設計方法

2014-11-30 17:38:06

。筆者基于實際項目中所涉及到的技術點,一步一步指導初學者學會FPGA設計,要想學會FPGA,必須經歷一下幾個關鍵點:1:對一個中等規模的模塊(500-1000行代碼)必須敢于下手,在綜合的過程中

2014-12-12 09:38:19

語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數據流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法,什么樣的代碼風格

2015-06-12 10:59:24

的邏輯電路。模塊四 FPGA設計常用IP模塊使用[size=12.0000pt]FPGA設計常用IP模塊使用課程主要內容為FPGA設計中常用IP模塊的使用(單/雙口RAM、DPRAM、FIFO、ROM及串行

2015-09-29 16:33:54

的邏輯電路。模塊四 FPGA設計常用IP模塊使用[size=12.0000pt]FPGA設計常用IP模塊使用課程主要內容為FPGA設計中常用IP模塊的使用(單/雙口RAM、DPRAM、FIFO、ROM及串行

2015-09-30 10:36:41

處理器的數字鐘設計 第9章 FPGA系統設計原則和技巧 9.1 FPGA系統設計的3個基本原則 9.2 FPGA系統設計的3種常用技巧 9.3 FPGA系統設計的3種常用IP模塊 第10章 利用

2012-02-09 15:45:32

apex20ke_atoms.v編譯到其中。2:在圖形界面中的Load Design對話框中裝入仿真設計時,在Verilog 標簽下指定預編譯庫的完整路徑。(見下圖)邏輯綜合目前可用的FPGA綜合工具

2020-05-15 07:00:00

FPGA系統設計原則和技巧之:FPGA系統設計的3種常用IP模塊.pdf(1012.86 KB)

2019-04-24 13:33:04

語言(Verilog HDL)是FPGA工程師的基本要求。通過本節課程的學習,學員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節課程學習,學員可以

2014-04-23 15:28:29

17日獲得技能:1、掌握FPGA結構和實現可編程開發原理;2、掌握FPGA設計流程,掌握modelsim、Quartus/ISE的使用;3、掌握Verilog HDL語法結構,可綜合與不可綜合編程;4

2012-10-12 09:29:00

22日獲得技能:1、掌握FPGA結構和實現可編程開發原理;2、掌握FPGA設計流程,掌握modelsim、Quartus/ISE的使用;3、掌握Verilog HDL語法結構,可綜合與不可綜合編程;4

2012-09-07 14:19:38

1. 目的本規范的目的是提高書寫代碼的可讀性、可修改性、可重用性,優化代碼綜合和仿真的結果,指導設計工程師使用VerilogHDL規范代碼和優化電路,規范化可編程技術部的FPGA設計輸入,從而做到

2017-12-08 14:36:30

關鍵字:Altera 、FPGA、軟硬件協調設計(Verilog & C)、CPU、總線、外設FPGA硬件結構知識Verilog HDL語言編程基礎FPGA常用開發工具 SOPC硬件系統開發SOPC軟件系統開發Avalon總線規范Nios II外設及其編程 七段數碼管時鐘...

2021-12-22 08:06:06

Verilog可綜合子集

2013-04-01 12:44:46

這里在網上找到一個fpga/cpld常用protel庫,傳上來給大家一起分享,好動西就是要大家一起,[hide][/hide]

2012-01-09 10:57:07

語句在用綜合工具綜合時將被忽略或者報錯。作為設計者,應該對可綜合模型的結構有所了解。 雖然不同的綜合工具對Verilog HDL語法結構的支持不盡相同,但Verilog HDL中某些典型的結構是很

2012-10-20 08:10:13

1,在一個verilog程序里,如果循環是一個循環次數不可定的循環,那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個能被綜合嗎

2015-02-03 15:29:11

,若不是,則只能用于仿真),while, 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

的編程風格SYSTEM VERILOG是VERILOG的一種延伸15.IP核的應用:軟核soft core: 功能經過驗證的、可綜合的、實現后門數在5K以上的HDL代碼固核firm core: 功能經過

2012-01-12 15:15:21

VERILOG是VERILOG的一種延伸15.IP核的應用:軟核soft core: 功能經過驗證的、可綜合的、實現后門數在5K以上的HDL代碼固核firm core: 功能經過驗證的、可綜合的、實現

2017-11-30 09:01:53

可綜合的Verilog語法和語義(劍橋大學,影印)

2012-08-06 13:03:57

可綜合的VerilogHDL設計實例在前面七章里我們已經學習了VerilogHDL的基本語法、簡單組合邏輯和簡單時序邏輯模塊的編寫、Top-Down設計方法、還學習了可綜合風格的有限狀態機

2009-11-23 16:01:33

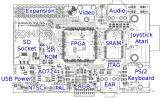

請問開源FPGA項目有哪些?

2023-12-26 12:09:06

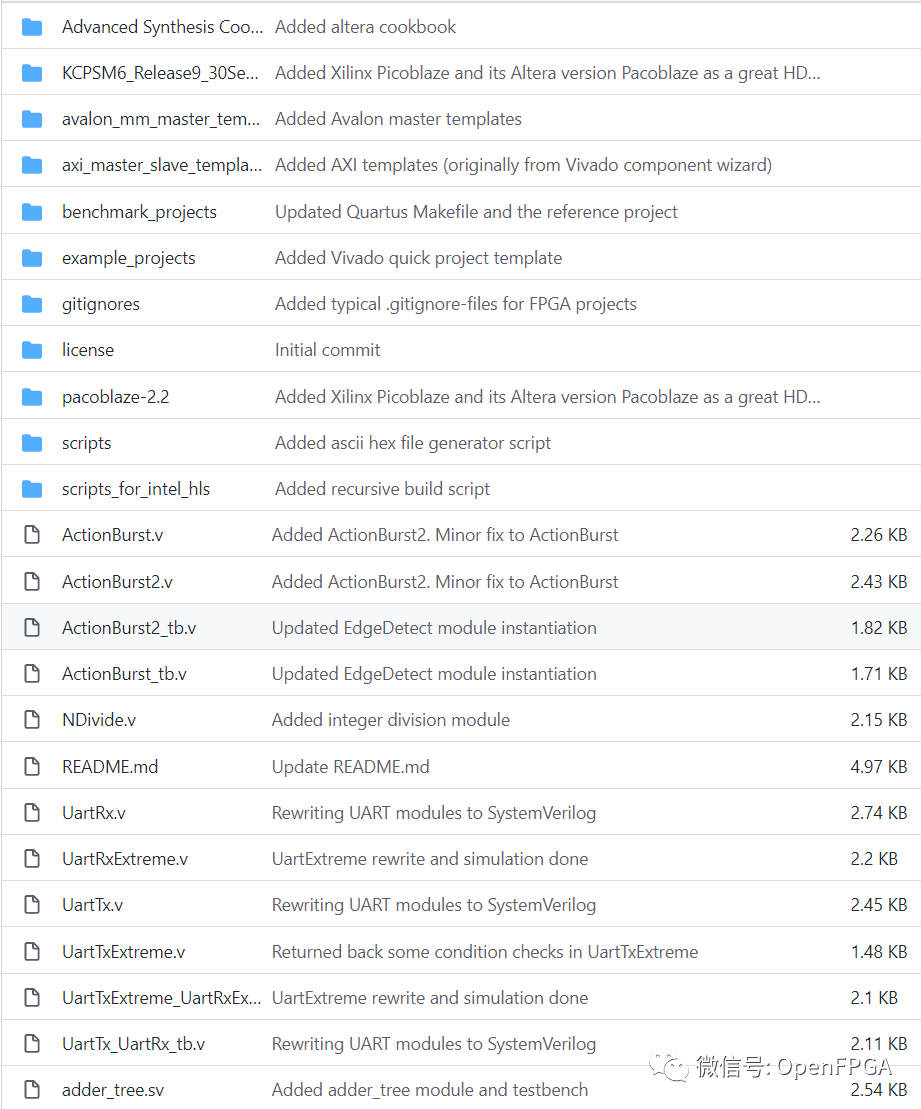

導入外部模塊,但是這個功能很有用的,比如我們引入一個開源組件,又想在工程里面直接包含該組件的源代碼并且還可以修改該組件的代碼。引入方式如下:(1)將外部的模塊的代碼目錄手動復制到自己的項目中,如下

2022-05-24 15:39:44

,都有Xilinx公司自己寫好的可綜合的模塊,想請教一下為什么要分成這樣兩項?它們里面的模塊有區別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區別呢?

2013-09-28 18:17:54

,都有Xilinx公司自己寫好的可綜合的模塊,想請教一下為什么要分成這樣兩項?它們里面的模塊有區別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區別呢?

2013-09-28 18:20:29

7.2設計入門(視頻)第8講:NIOSII 7.2 設計入門(視頻)第9講:FPGA系統設計技巧-乒乓操作(視頻)第10講:FPGA設計常用IP核-鎖相環(視頻)地址:http

2009-03-26 16:37:40

:從零開始設計FPGA最小系統一: 核心電路(PDF、視頻)第3講:從零開始設計FPGA最小系統二: 外圍電路(PDF、視頻)第4講:Verilog HDL語法一:常用語句(視頻)第5講

2009-03-09 22:56:25

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

方式;固核則通常介于上面兩者之間,它已經通過功能驗證、時序分析等過程,設計人員可以以邏輯門級網表的形式獲取。FPGA的開發方式分為三種,分別是:原理圖、Verilog HDL以及IP核。其中原理圖方式

2016-12-22 23:37:00

II、ISE等一種以上開發工具進行綜合布局布線,熟悉顯示行業常用的相關接口;能獨立承擔硬件FPGA設計項目,按照項目計劃要求完成任務,能夠獨立進行FPGA需求分析、芯片評估、器件選型,并完成相關硬件系統

2017-06-29 13:47:39

講,主要通過演示FPGA數字邏輯設計中除Verilog代碼方式設計外另外一種最常用的設計方式——使用IP核進行系統設計。本教程講解了如何在Quartus II軟件中調用一個基本的免費IP核——計數器IP核

2015-09-22 14:06:56

的 Verilog/FPGA開源項目》內容介紹更加詳細,包括但不限于綜合、上板測試等。兩者相輔相成,互補互充~

這幾年DPU的概念越來越火,有和CPU、GPU并駕齊驅的勢頭,通俗的講DPU分擔的工作

2023-11-01 16:27:44

XST支持哪些語言?VHDL, Verilog-2002, 以及Mixed Language of VHDL and Verilog。所支持的可綜合的VHDL和Verilog的子集可以查看XST

2018-08-08 10:31:27

的基本要求。通過本節課程的學習,學員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節課程學習,學員可以設計一些簡單的FPGA程序

2018-09-19 11:34:03

。比如:怎么創建工程,怎么添加文件,怎么跑一系列編譯的流程,怎么加入時序約束,怎么分配管腳,然后怎么把生成的FPGA映像加載到開發板上運行。

第二,就是熟悉一些常用的IP的用法

。在FPGA項目中,我們

2024-01-02 23:03:31

,是指硬件能夠實現的一些語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數據流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法

2017-12-06 19:50:25

`勇敢的芯伴你玩轉Altera FPGA連載33:可綜合的語法子集4特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 連續賦值

2017-12-19 21:36:24

及說明–介紹Verilog testbench?激勵和控制和描述?結果的產生及驗證–任務task及函數function–用戶定義的基本單元(primitive)–可綜合的Verilog描述風格介紹

2012-08-03 00:23:48

工程師的基本要求。通過本節課程的學習,學員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節課程學習,學員可以設計一些簡單的FPGA

2015-10-27 17:57:38

1 背景知識采用基于FPGA的方式進行系統設計,具備運行傳輸速度快、并行處理內部程序、有大量開發好的IP核、引腳眾多、設計靈活等優點。針對被測樣機的功能模式和受控電路模塊眾多,對控制器I/O引腳資源

2018-08-07 10:08:19

的挑戰。本文采用RFC815中的重組算法實現的基于FPGA的IP碎片重組模塊能夠提供對OC-48接口流量的支持,具有硬件開銷小,可擴展性好的特點,并提供了一種針對IP碎片攻擊的預警機制,能夠抵抗常見

2008-10-07 11:00:19

作為我項目的一部分,我需要將ADC與7系列FPGA接口,我有一個SelectIO?接口向導的IP核。但是,我的整個項目都在VHDL中,IPi得到的是Verilog。請指出我如何在我的VHDL頂級模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

學習fpga我用的verilog語言,怎么模塊化呢????

2013-11-21 23:11:32

閱讀目錄 linux/嵌入式常用開源庫列表其他資料參考資料linux下/嵌入式常用的開源庫名字及簡介,使用文檔和教程可以自己百度 (自己整理,不定時完善) linux/嵌入式常用開源庫列表

2021-12-24 06:53:15

的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節課程學習,學員可以設計一 些簡單的FPGA程序,掌握組合邏輯和時序邏輯電路的設計方法。通過實戰訓練,學員可以

2014-09-16 17:52:27

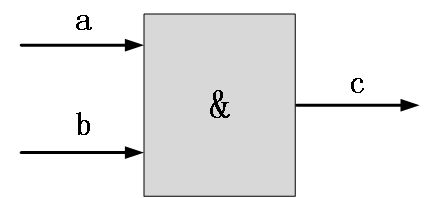

verilog代碼,該代碼描述了一個加法器功能。該代碼經過綜合器解釋后,轉化成一個加法器電路。QUARTUS、ISE和VIVADO都是綜合器,集成電路常用的綜合器是DC。我們在FPGA設計的過程中,不可避免

2018-10-08 15:19:23

是在描述硬件,即用代碼畫圖。在 Verilog 語言中,always 塊是一種常用的功能模塊,也是結構最復雜的部分。筆者初學時經常為 always 語句的編寫而苦惱.

2021-07-29 07:42:25

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎的函數庫以及常用的控制函數模塊,配合

2022-05-19 09:16:05

Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86 給出了一種基于FPGA的分頻電路的設計方法.根據FPGA器件的特點和應用范圍,提出了基于Verilog的分頻方法.該方法時于在FPGA硬件平臺上設計常用的任意偶數分頻、奇數分頻、半整數分頻

2011-11-09 09:49:33 355

355 《ARM嵌入式常用模塊與綜合系統設計實例精講》針對目前通用流行的ARM嵌入式處理器,通過實例精講的形式,詳細介紹了ARM嵌入式常用模塊與綜合應用系統設計的方法及技巧。

2012-03-05 15:53:58 0

0 可綜合的Verilog語法和語義(劍橋大學,影印):第七版

2012-05-21 14:50:14 27

27 文中在FPGA芯片中嵌入MC8051 IP Core,作為控制核心,利用Verilog HDL語言進行編程,設計了以MC8051 IPCore為核心的控制模塊、計數模塊、鎖存模塊和LCD顯示模塊等模塊電路,采用等精度測量法

2012-12-24 09:51:45 2017

2017 文中在FPGA芯片中嵌入MC8051 IP Core,作為控制核心,利用Verilog HDL語言進行編程,設計了以MC8051 IPCore為核心的控制模塊、計數模塊、鎖存模塊和LCD顯示模塊等模塊電路,采用等精度測量法

2013-01-07 11:17:31 4576

4576

Xilinx FPGA工程例子源碼:IP camera的開源系統

2016-06-07 14:13:43 13

13 MSP430單片機常用模塊與綜合系統實例精講

2017-05-14 08:00:00 89

89 FPGA verilog 相關設計實踐

2017-09-06 11:19:34 32

32 本文檔的主要內容詳細介紹的是常用模塊的Verilog HDL設計詳細資料免費下載。

2018-10-16 11:12:54 20

20 本文檔的主要內容詳細介紹的是FPGA視頻教程之Verilog基礎的詳細資料說明包括了:1.Verilog HDL簡介,2.Verilog HDL模型的基本結構,3.Verilog HDL模塊的組成

2019-03-21 15:02:49 37

37 在接觸Verilog 語法參考手冊的時候,我們發現其提供了一組非常豐富的功能來描述硬件。所以大家往往會疑惑那些Verilog語句是可綜合的,那些是只能用于寫Testbench的,其實,參考手冊中只有

2019-04-20 10:59:39 4049

4049 本文檔的主要內容詳細介紹的是FPGA的視頻教程之Verilog模塊的基本構成要素資料說明。

2019-03-26 16:55:21 13

13 本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-02 07:10:00 2926

2926

本文主要介紹verilog基礎模塊,夯實基礎,對深入學習FPGA會有很大幫助。

2022-02-08 15:04:08 1994

1994

本文主要介紹verilog基礎模塊,夯實基礎,對深入學習FPGA會有很大幫助。

2021-01-22 10:41:17 5

5 電路“胸有成竹”; 牢記可綜合Verilog HDL與電路結構一一對應的關系; 確認電路指標是什么:性能?面積? 硬件思維方式,代碼不再是一行行的代碼而是一塊一塊的硬件模塊; 達到以上幾點,就可以確保寫出行云流水般的高質量代碼。 關于代碼與硬件電路的對應關系,參見如下圖

2021-04-04 11:19:00 3847

3847

FPGA設計中DAC控制的Verilog實現(單片機電源維修)-該文檔為FPGA設計中DAC控制的Verilog實現資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-26 12:18:48 18

18 FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 該FPGA項目旨在詳細展示如何使用Verilog處理圖像,從Verilog中讀取輸入位圖圖像(.bmp),處理并將處理結果寫入Verilog中的輸出位圖圖像。提供了用于讀取圖像、圖像處理和寫入圖像

2021-09-23 15:50:21 5150

5150 優秀的 Verilog/FPGA開源項目介紹(一)-PCIe通信 今天開始會陸續介紹一些優秀的開源項目,項目基本都是和FPGA或HDL相關的。對于一些找工作或者急需項目經驗的人來說,這些項目都有一定

2021-10-11 15:31:47 8450

8450

今天介紹兩個(only two)網絡相關的開源項目。 Alex的verilog-ethernet之前在介紹PCIe項目時有介紹過Alex的項目,當時重點介紹了PCIe。今天主要介紹

2021-10-27 09:20:49 2278

2278

優秀的 Verilog/FPGA開源項目介紹(五)- USB通信 USB是我們生活中非常非常常見的接口,鼠標、鍵盤以及常見的U 盤等,可以說現在的USB設備已經滲透到生活中的方方面面,下面就介紹幾個

2021-11-02 14:54:15 7820

7820

優秀的 Verilog/FPGA開源項目介紹(七)- CAN0、CAN總線介紹《【科普】CAN總線介紹及FPGA實現方案簡介》 1、CAN權威文檔CAN總線有兩個ISO國際標準:ISO11898

2021-11-17 11:19:56 2730

2730 ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 12

12 電子發燒友網站提供《TTL FPGA開源項目.zip》資料免費下載

2022-07-28 10:18:33 3

3 電子發燒友網站提供《樹莓派計算模塊開源項目.zip》資料免費下載

2022-08-05 09:25:58 1

1 電子發燒友網站提供《FPGA與MCU單片機的綜合開發板開源.zip》資料免費下載

2022-08-09 09:41:41 2

2 電子發燒友網站提供《基于IP5306 3.7V升壓5V充電開源項目.zip》資料免費下載

2022-08-09 09:28:00 17

17 電子發燒友網站提供《快充模塊IP6505T開源分享.zip》資料免費下載

2022-08-10 14:33:38 5

5 Verilog 例化說明 1.什么是模塊例化?為什么要例化? 模塊例化可以理解成模塊調用。對于一個 FPGA 工程,通常是由一個頂層模塊與多個功能子模塊組成,為了實現頂層模塊與子模塊的連接,需要進行

2022-12-12 09:50:06 2700

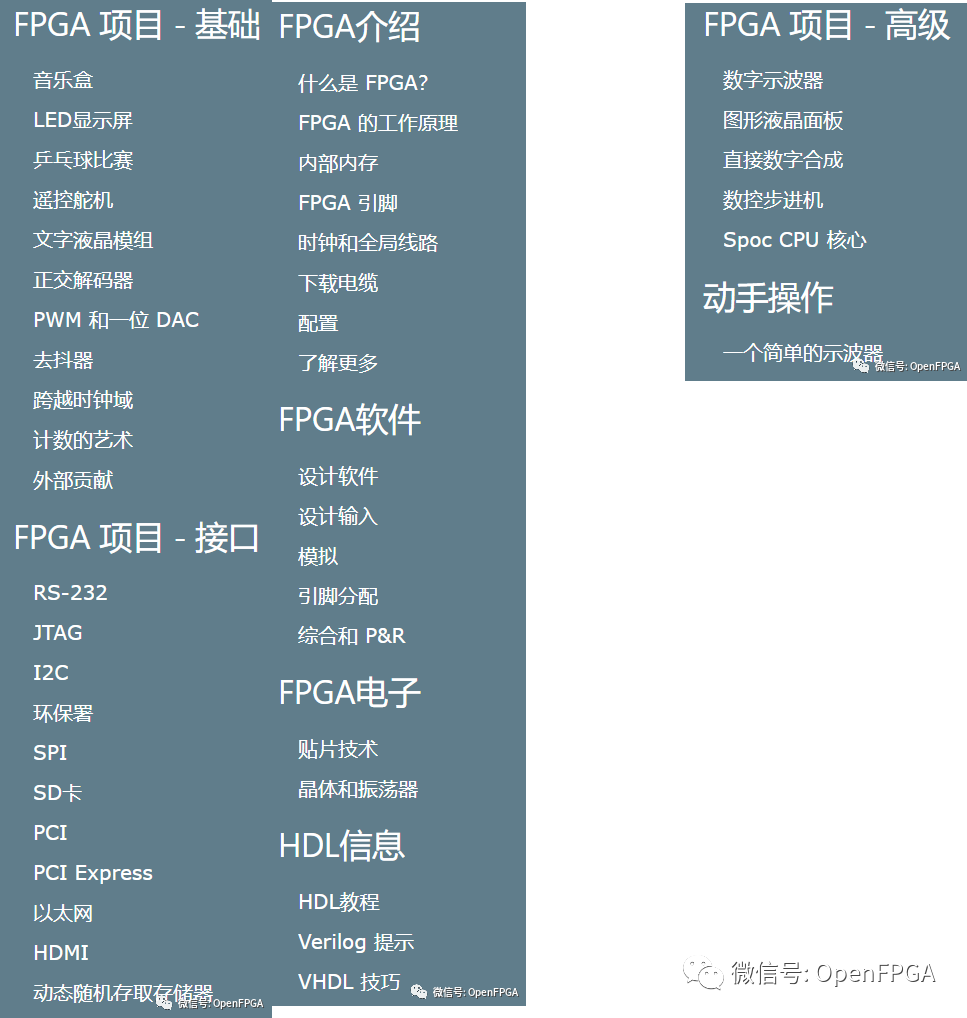

2700 FPGA 項目使用一種稱為 Verilog 的語言,您需要學習它才能理解項目。但是通過此處顯示的示例以及其他可用的在線資源,這并不太難。

2023-04-06 14:33:10 706

706

本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:17:12 924

924

本文是本系列的第四篇,本文主要介紹FPGA常用運算模塊-除法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:20:45 1936

1936

本文是本系列的第五篇,本文主要介紹FPGA常用運算模塊-復數乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:23:28 1244

1244

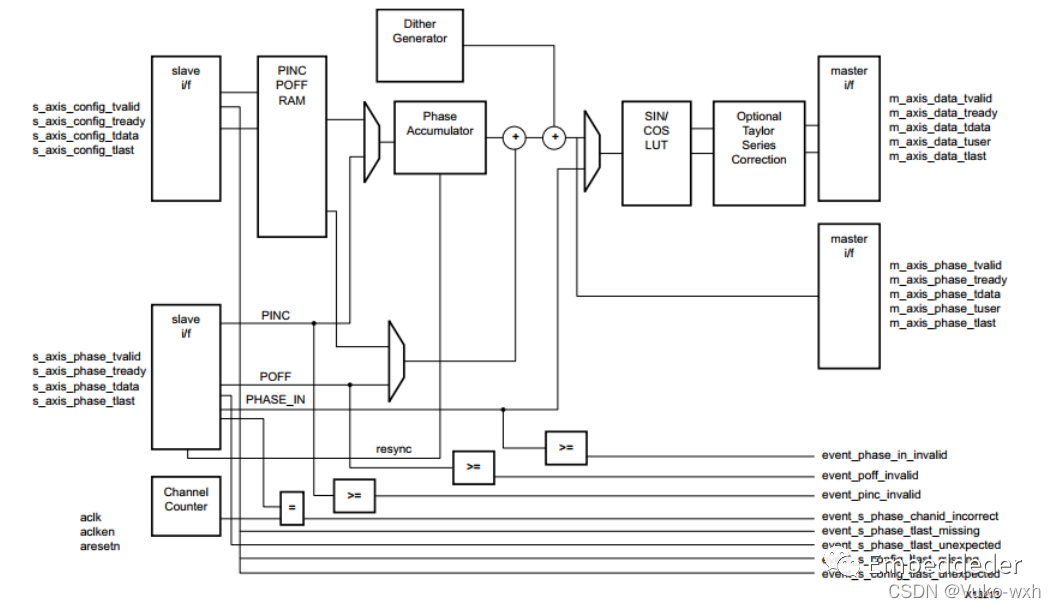

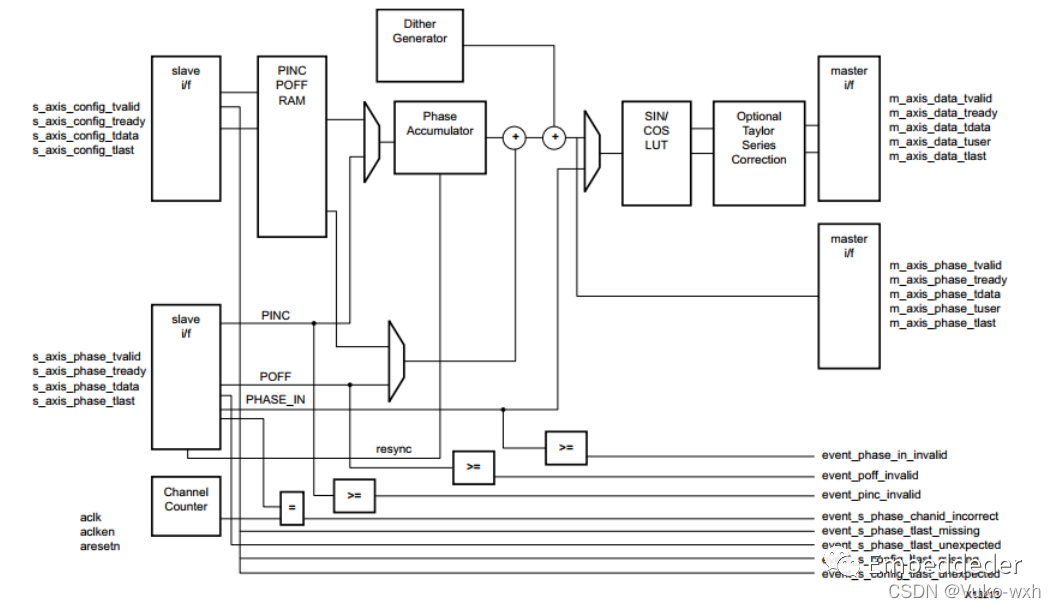

本文是本系列的第六篇,本文主要介紹FPGA常用運算模塊-DDS信號發生器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-24 10:37:18 3801

3801

《優秀的IC/FPGA開源項目》是新開的系列,旨在介紹單一項目,會比《優秀的 Verilog/FPGA開源項目》內容介紹更加詳細,包括但不限于綜合、上板測試等。兩者相輔相成,互補互充。

2023-06-09 09:42:41 1326

1326

FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復用的設計模塊或功能片段。它們是預先編寫好的硬件設計代碼,可以在FPGA芯片上實現特定的功能。

2023-07-03 17:13:28 4343

4343 Hello,大家好,之前給大家分享了大約一百多個關于FPGA的開源項目,涉及PCIe、網絡、RISC-V、視頻編碼等等,這次給大家帶來的是不枯燥的娛樂項目,主要偏向老的游戲內核使用FPGA進行硬解,涉及的內核數不勝數,主要目標是高的可實現性及復現性。

2024-01-10 10:54:24 393

393

FPGA(現場可編程邏輯門陣列)開發主要使用的編程語言是硬件描述語言(HDL),其中Verilog是最常用的編程語言之一。而C語言通常用于傳統的軟件編程,與FPGA的硬件編程有所區別。

2024-03-27 14:38:14 136

136

電子發燒友App

電子發燒友App

評論