韓國(guó)產(chǎn)“迷你”高速電動(dòng)汽車(chē)(Mini Eletronic Vehicle)以迷你電動(dòng)汽車(chē)為概念,可實(shí)現(xiàn)性能及價(jià)格的最優(yōu)化,是一款國(guó)民性電動(dòng)汽車(chē)。

2013-01-25 09:29:12 2047

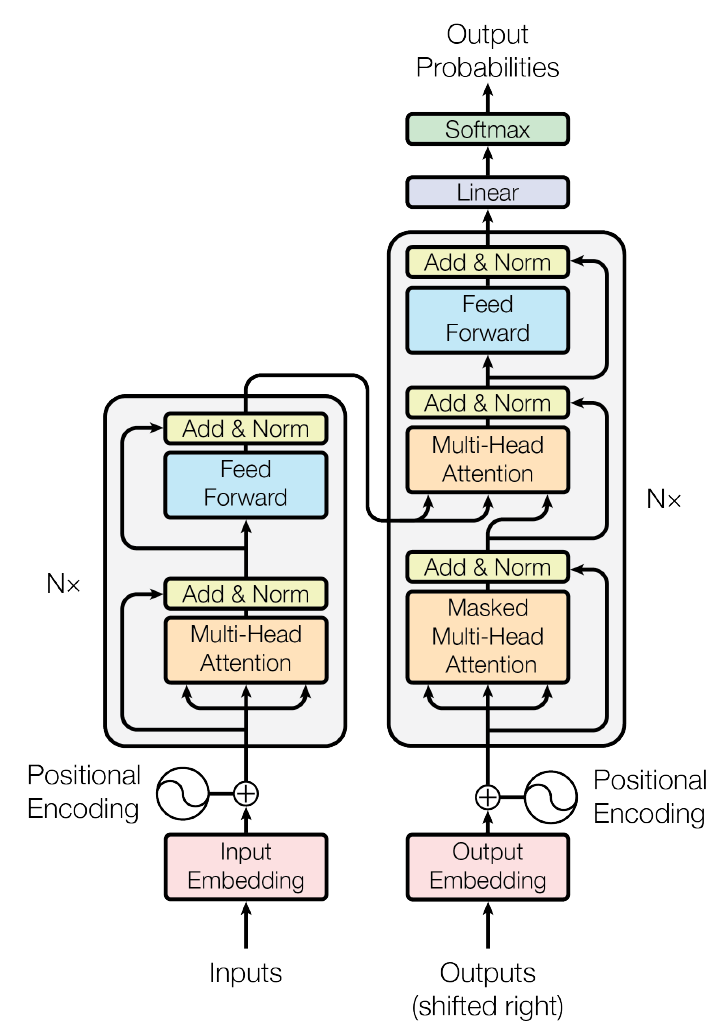

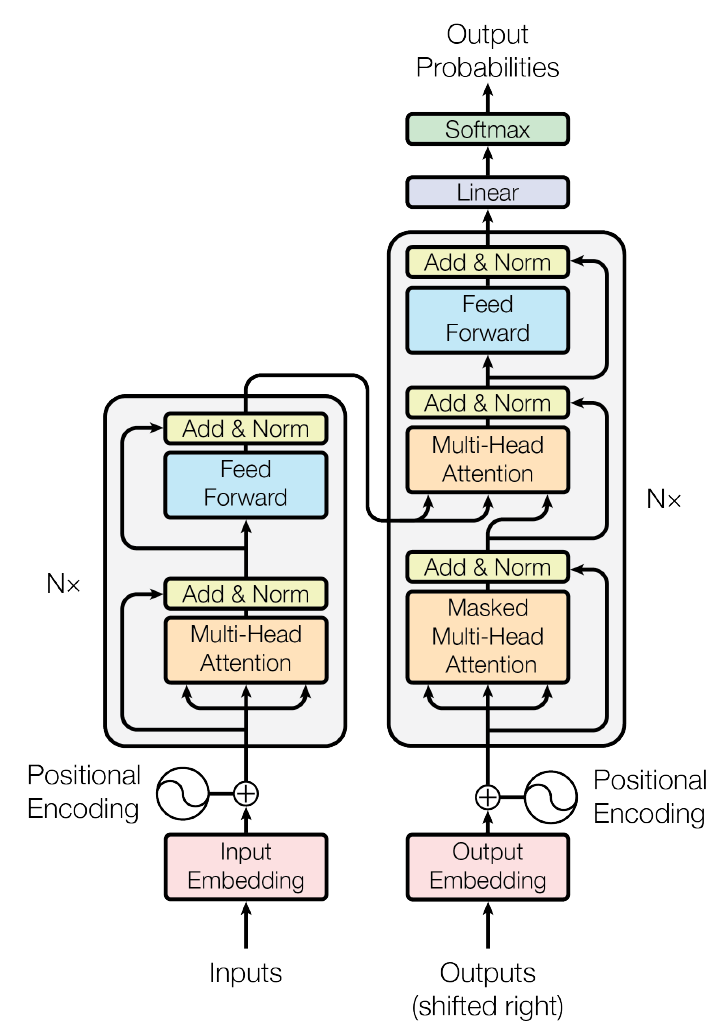

2047 前言 AI芯片(這里只談FPGA芯片用于神經(jīng)網(wǎng)絡(luò)加速)的優(yōu)化主要有三個(gè)方面:算法優(yōu)化,編譯器優(yōu)化以及硬件優(yōu)化。算法優(yōu)化減少的是神經(jīng)網(wǎng)絡(luò)的算力,它確定了神經(jīng)網(wǎng)絡(luò)部署實(shí)現(xiàn)效率的上限。編譯器優(yōu)化和硬件優(yōu)化

2020-09-29 11:36:09 4442

4442

供應(yīng)商不相關(guān)性使用戶(hù)可以輕松將任意 FPGA 器件重新作為目標(biāo)對(duì)象并分析結(jié)果,從而找到最適合您設(shè)計(jì)的 FPGA 器件。 在與供應(yīng)商無(wú)關(guān)的環(huán)境中使用高級(jí)合成技術(shù),針對(duì)每種 FPGA 器件實(shí)現(xiàn)特定的架構(gòu)優(yōu)化

2018-09-20 11:11:16

方案。實(shí)際上,在過(guò)去十年中,FPGA內(nèi)置嵌入式處理器的應(yīng)用在穩(wěn)步增長(zhǎng)(圖2)。但是,并不是所有基于FPGA的解決方案都能夠滿足目前苛刻的需求。傳統(tǒng)上,使用基于HDL的“軟核”ARM來(lái)實(shí)現(xiàn)基于FPGA

2021-07-14 08:00:00

FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法介紹了利用現(xiàn)場(chǎng)可編程邏輯門(mén)陣列FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化方法。重點(diǎn)介紹了DDS技術(shù)在FPGA中的實(shí)現(xiàn)

2012-08-11 18:10:11

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周?chē)缕瑢?duì)接,此時(shí)IPO接口的時(shí)序問(wèn)題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問(wèn)題。

2012-08-12 11:57:59

現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)作為專(zhuān)用集成電路(ASIC)領(lǐng)域的一種半定制電路,可以根據(jù)設(shè)計(jì)的需要靈活實(shí)現(xiàn)各種接口或者總線的輸出,在設(shè)備端的通信產(chǎn)品中已得到越來(lái)越廣泛的使用。FPGA

2019-06-14 06:00:00

資源情況了如指掌,并在編寫(xiě)代碼過(guò)程中結(jié)合器件結(jié)構(gòu)才有可能設(shè)計(jì)出最優(yōu)化的代碼風(fēng)格。(特權(quán)同學(xué),版權(quán)所有)這里我們將和大家一起探討在絕大多數(shù)FPGA設(shè)計(jì)中必定會(huì)而且可能是非常頻繁的涉及到的邏輯電路的設(shè)計(jì)原則、思想或代碼書(shū)寫(xiě)方式。(特權(quán)同學(xué),版權(quán)所有)

2015-06-25 09:41:55

的可編程性輕松實(shí)現(xiàn)設(shè)計(jì)修改。由于 EasyPath-6 FPGA 在架構(gòu)上與 Virtex-6 FPGA 完全相同,客戶(hù)可以放心地把整套Virtex-6FPGA嵌入式資源納入他們的量產(chǎn)設(shè)計(jì),包括千兆級(jí)串行

2012-08-11 18:17:16

了一系列優(yōu)化算法,但是用戶(hù)仍有必要遵循一定的編碼風(fēng)格去引導(dǎo) 綜合工具在特定 FPGA 架構(gòu)上達(dá)到最優(yōu)結(jié)果。 設(shè)計(jì)規(guī)劃用于指導(dǎo)用戶(hù)把設(shè)計(jì)更好地適配到所選用的 FPGA上并合理地 平衡面積和速度的要求,目的

2022-09-29 06:12:02

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級(jí)設(shè)計(jì)

2021-04-15 06:33:58

在28nmFPGA上實(shí)現(xiàn)100Gbit OTN復(fù)用轉(zhuǎn)發(fā)器解決方案(中文版和英文版)

2012-08-13 22:38:30

在FPGA上實(shí)現(xiàn)H 264 AVC視頻編碼標(biāo)準(zhǔn)盡管H.264/AVC承諾將比已有視頻編碼標(biāo)準(zhǔn)具有更高的編碼效率,它仍為系統(tǒng)架構(gòu)師、DSP 工程師和硬件設(shè)計(jì)人員帶來(lái)了巨大的工程設(shè)計(jì)挑戰(zhàn)。H.264

2008-06-25 11:33:26

FPGA原型的最佳方法。這些最佳方法包括:在設(shè)計(jì)過(guò)程初期分析定點(diǎn)量化的效應(yīng)并優(yōu)化字長(zhǎng),產(chǎn)生更 小、更高效的實(shí)現(xiàn)方案;利用自動(dòng)HDL代碼生成功能,更快生成FPGA原型;重用具有HDL協(xié)同仿真功能的系統(tǒng)級(jí)

2020-05-04 07:00:00

大家好,我想在Artix fpga上實(shí)現(xiàn)TMRmodule。經(jīng)過(guò)一番搜索,似乎隔離設(shè)計(jì)流程(IDF)是一種很好的方法。我是以正確的方式嗎?如果“是”,請(qǐng)幫我一個(gè)示例,告訴我如何為IDF準(zhǔn)備我的設(shè)計(jì)。如果“不”請(qǐng)給出一些想法。謝謝

2020-08-17 10:49:06

ESP32-CAM ArduinoIDE開(kāi)發(fā)系列文章目錄第一篇:ESP32-CAM高性?xún)r(jià)比WIFI圖傳方案快速入門(mén)教程第二篇:ESP32-CAM第一個(gè)無(wú)線點(diǎn)燈程序第三篇:ESP32-CAM智能網(wǎng)關(guān)

2021-12-16 07:01:15

你好,當(dāng)我在原理圖視圖中單擊LUT時(shí),它會(huì)按預(yù)期顯示逆變器。但我想知道它是通過(guò)逆變器在Xilinx FPGA上實(shí)現(xiàn)還是實(shí)際上原理圖不等同于FPGA的真相?謝謝,?以上來(lái)自于谷歌翻譯以下為原文Hi

2019-01-29 09:22:50

本章提要最優(yōu)化問(wèn)題廣泛存在于國(guó)民經(jīng)濟(jì)各部門(mén)和工程應(yīng)用各領(lǐng)域中。在所有可能的方案中搜索出最合理的、邊到事先預(yù)定的最優(yōu)目標(biāo)方案(即最優(yōu)方案〉的方法稱(chēng)為最優(yōu)化方法。本章簡(jiǎn)要介紹了優(yōu)化問(wèn)題的分類(lèi)及工程背景

2012-03-06 14:53:54

一、 概述: MSC8328P是高度集成的Car-cam. Sports-cam和IP-cam解決方案,主芯片為Dual 600MHz 32-bit RISC 處理器,內(nèi)置DDR

2020-07-03 15:09:31

路徑的優(yōu)化算法,并基于一種方法編程實(shí)現(xiàn)了基本方案。最后在HSP貼片系統(tǒng)上使用本解決方案,大幅度提高了生產(chǎn)效率,證明了本解決方案的優(yōu)越性和高效性,同時(shí)也為用其它算法解決SMT系統(tǒng)優(yōu)化問(wèn)題提供了一種可

2010-04-24 10:09:25

環(huán)節(jié)。讓模塊劃分最優(yōu)化是一個(gè)系統(tǒng)工程師必備的技能。模塊劃分最優(yōu)化有幾點(diǎn)建議:1)完全理解系統(tǒng)的需求和規(guī)格。2)對(duì)系統(tǒng)的實(shí)現(xiàn)要做到非常清楚。3)劃分的模塊需要和熟悉系統(tǒng)的人討論,大家都覺(jué)得是最優(yōu)的時(shí)候才

2013-09-11 23:10:21

寫(xiě)了一個(gè)labview數(shù)據(jù)的組合排序最優(yōu)化程序我們假設(shè)有不同數(shù)據(jù)的尺寸1000個(gè),現(xiàn)在給出假設(shè)1000mm長(zhǎng)度,怎樣用這1000個(gè)數(shù)據(jù)尺寸去排列組合得到一組數(shù)據(jù)是最化的,那么1000組數(shù)據(jù)1000*999*998....*2*1 種排序組合。附件程序就是實(shí)現(xiàn)排序最化的例子。

2019-08-13 20:25:44

【PDF】最優(yōu)化方法及MATLAB的實(shí)現(xiàn)附件:

2011-02-28 11:10:41

以及FPGA所實(shí)現(xiàn)的設(shè)計(jì)。完成對(duì)電源管理參考設(shè)計(jì)的修改之后,它看起來(lái)將與最初的參考設(shè)計(jì)不同。可能有人會(huì)辯稱(chēng),最好的解決方案是根本不用電源管理參考設(shè)計(jì),而是直接將所需的電壓軌和電流輸入到電源管理選型與優(yōu)化

2019-12-11 16:56:30

軌單個(gè)的高效率開(kāi)關(guān)穩(wěn)壓器和 LDO 在電路板上實(shí)現(xiàn)最佳布局和 IC 定位靈活性以及熱傳播所有開(kāi)關(guān)穩(wěn)壓器在 >2MHz 下工作,實(shí)現(xiàn)最優(yōu)尺寸和外部組件成本并降低 AM 無(wú)線波段的噪聲為電路板上的所有電源軌進(jìn)行電壓定序提供專(zhuān)用的 DDRx 內(nèi)存終端此電路經(jīng)過(guò)測(cè)試并包含設(shè)計(jì)注意事項(xiàng)

2018-08-09 07:58:16

本文闡述了Spartan-3 FPGA針對(duì)DSP而優(yōu)化的特性,并通過(guò)實(shí)現(xiàn)示例分析了它們在性能和成本上的優(yōu)勢(shì)。

2019-10-18 07:11:35

方案如圖4所示。這是一個(gè)功能正確的應(yīng)用實(shí)現(xiàn)方案,但沒(méi)有進(jìn)行任何性能優(yōu)化或?yàn)槌浞掷?b class="flag-6" style="color: red">FPGA架構(gòu)的功能進(jìn)行考慮。因此該代碼在SDAccel中編譯完成后,在Alpha Data卡上運(yùn)行得到的最大吞吐量?jī)H為

2019-06-19 07:27:40

耗時(shí),除非是基于FPGA進(jìn)行批量生產(chǎn)。通常,只有在應(yīng)用開(kāi)發(fā)的最后階段軟件才可以運(yùn)行于目標(biāo)硬件,并確定處理算法的實(shí)現(xiàn)是否為最佳。 CAP算法實(shí)現(xiàn)流程 CAP使應(yīng)用開(kāi)發(fā)工程師能獲得FPGA

2008-09-27 11:42:55

(FPGA as a Service) 彈性計(jì)算平臺(tái),形成了完整的阿里云 WebP 圖片解決方案。阿里云 WebP 圖片解決方案在 ECS 產(chǎn)品可靠、安全、便利的基礎(chǔ)上,進(jìn)一步發(fā)揮了 FPGA 在數(shù)

2018-01-11 15:36:31

2 示出了一款典型的多通道復(fù)位IC。采用復(fù)位IC 來(lái)實(shí)現(xiàn)上電排序的優(yōu)點(diǎn)是解決方案處于受監(jiān)視的狀態(tài)。必須在確認(rèn)每個(gè)電源軌都處在穩(wěn)壓范圍內(nèi)之后再釋放下一個(gè)電源軌,而且無(wú)需在電源轉(zhuǎn)換器上提供一個(gè)PGOOD

2019-09-17 14:22:00

方案。實(shí)際上,在過(guò)去十年中,FPGA內(nèi)置嵌入式處理器的應(yīng)用在穩(wěn)步增長(zhǎng)(圖2)。但是,并不是所有基于FPGA的解決方案都能夠滿足目前苛刻的需求。傳統(tǒng)上,使用基于HDL的“軟核”ARM來(lái)實(shí)現(xiàn)基于FPGA

2021-07-12 08:00:00

的流行方法是使用許多FPGA供應(yīng)商都提供的已有電源管理參考設(shè)計(jì)。這對(duì)于優(yōu)化設(shè)計(jì)來(lái)說(shuō)是一個(gè)很好的入門(mén)方式。但此類(lèi)設(shè)計(jì)往往需要修改,因?yàn)?b class="flag-6" style="color: red">FPGA系統(tǒng)通常需要額外的電壓軌和負(fù)載,這些也需要供電。在參考設(shè)計(jì)上增加

2019-05-05 08:00:00

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:04:25

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺(tái):ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實(shí)現(xiàn)

2014-06-19 12:06:43

其在設(shè)計(jì)思路和編程風(fēng)格等方面也存在差異,這些差異會(huì)對(duì)系統(tǒng)綜合后的電路整體性能產(chǎn)生重要的影響。在VHDL語(yǔ)言電路優(yōu)化設(shè)計(jì)當(dāng)中,優(yōu)化問(wèn)題主要包括面積優(yōu)化和速度優(yōu)化。面積優(yōu)化是指CPLD/FPGA的資源

2019-06-18 07:45:03

基于ESP32CAM的物聯(lián)網(wǎng)相機(jī)系統(tǒng)③(在JSP服務(wù)器圖傳相片給所有客戶(hù)端欣賞)第四篇:最簡(jiǎn)單DIY基于ESP32CAM的物聯(lián)網(wǎng)相機(jī)系統(tǒng)④(用調(diào)試串口助手實(shí)現(xiàn)串口圖傳)第五篇(上):最簡(jiǎn)單DIY基于ESP32CAM的物聯(lián)網(wǎng)相機(jī)系統(tǒng)⑤(用1306OLED實(shí)現(xiàn)WIFI黑白屏照相機(jī))第五篇(下):最簡(jiǎn)單DIY

2022-01-25 07:47:08

如何用單顆芯片實(shí)現(xiàn)出色的處理性能、能效和安全性?如何優(yōu)化AR解決方案?

2021-06-02 06:56:16

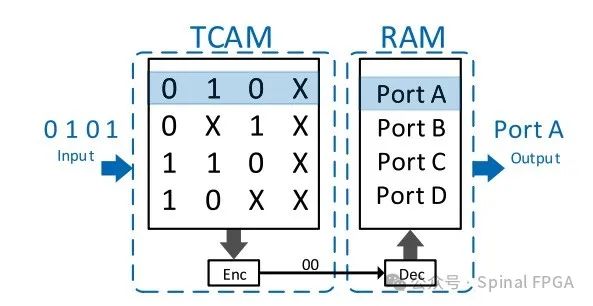

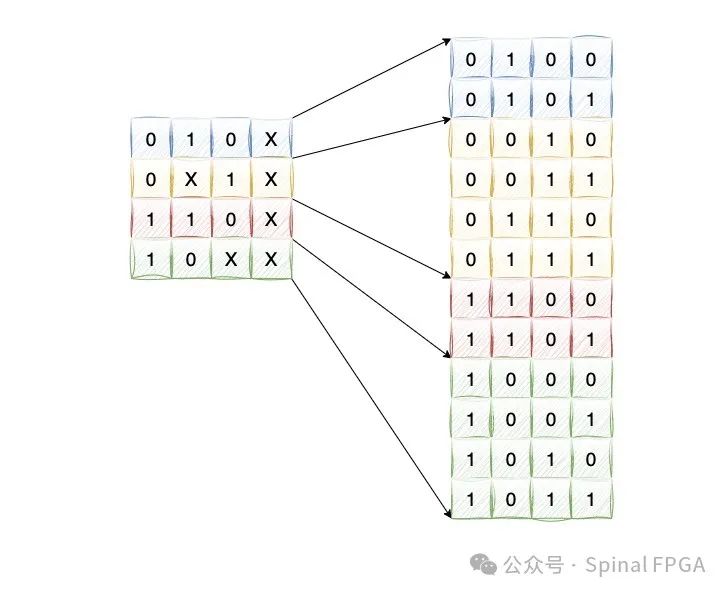

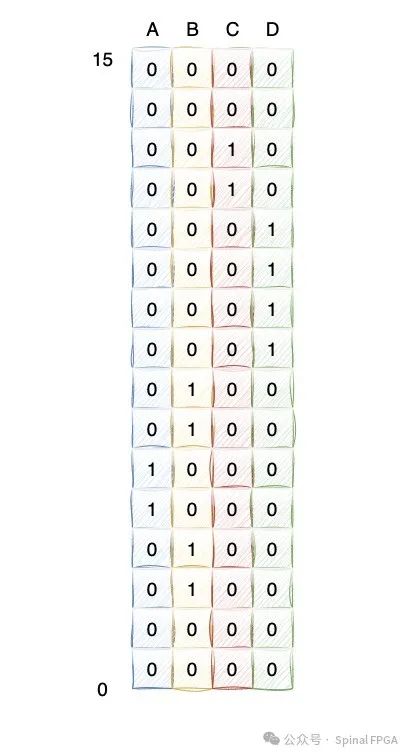

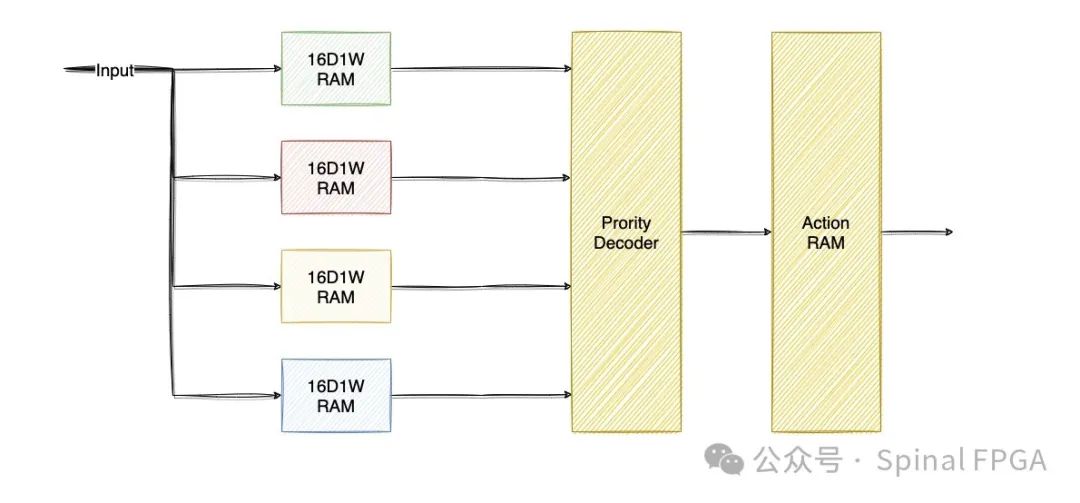

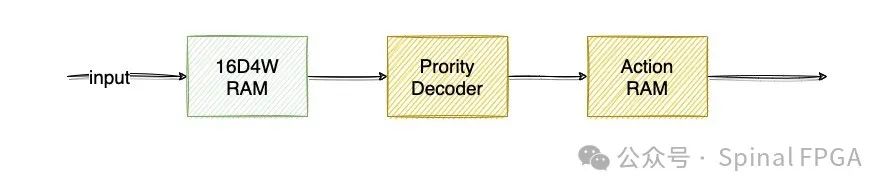

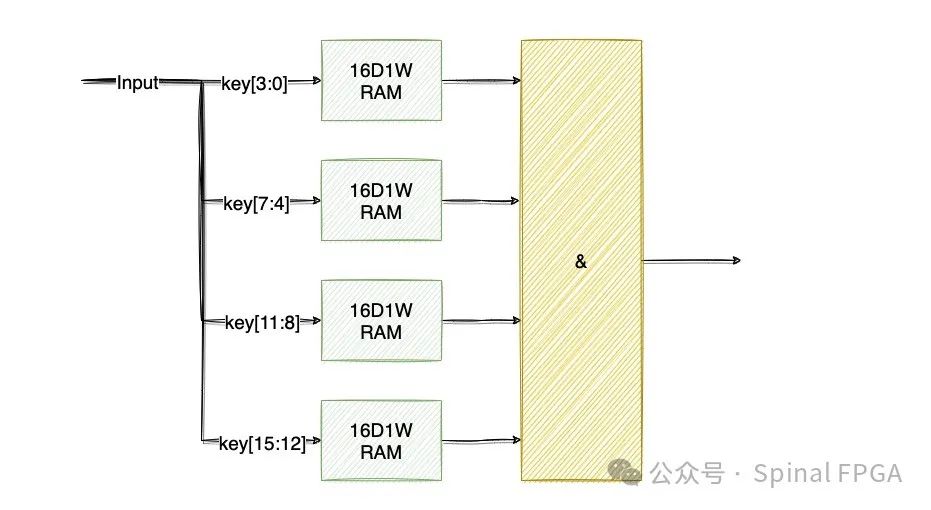

基于關(guān)聯(lián)比較器的信號(hào)預(yù)分選原理關(guān)聯(lián)比較器的設(shè)計(jì)基于CAM的關(guān)聯(lián)比較器的FPGA實(shí)現(xiàn)

2021-04-29 06:02:12

。 FPGA曾一度被認(rèn)為是僅用于開(kāi)發(fā)的解決方案,但如今其價(jià)位下降非常迅速,使得許多問(wèn)題迎刃而解,甚至能以低于傳統(tǒng)ASIC或ASSP解決方案的總體系統(tǒng)成本投產(chǎn)。現(xiàn)在,面向汽車(chē)市場(chǎng)的各大FPGA供應(yīng)商均已通過(guò)ISO-TS16949認(rèn)證,使得可編程邏輯器件逐漸成為汽車(chē)市場(chǎng)的主流技術(shù)。

2019-09-03 06:54:39

。 FPGA曾一度被認(rèn)為是僅用于開(kāi)發(fā)的解決方案,但如今其價(jià)位下降非常迅速,使得許多問(wèn)題迎刃而解,甚至能以低于傳統(tǒng)ASIC或ASSP解決方案的總體系統(tǒng)成本投產(chǎn)。現(xiàn)在,面向汽車(chē)市場(chǎng)的各大FPGA供應(yīng)商均已通過(guò)ISO-TS16949認(rèn)證,使得可編程邏輯器件逐漸成為汽車(chē)市場(chǎng)的主流技術(shù)。

2019-09-24 08:33:51

`作者:Frederik Dostal為FPGA應(yīng)用設(shè)計(jì)優(yōu)秀電源管理解決方案不是一項(xiàng)簡(jiǎn)單的任務(wù),相關(guān)技術(shù)討論有很多。本文一方面旨在找到正確解決方案并選擇最合適的電源管理產(chǎn)品,另一方面則是如何優(yōu)化實(shí)際

2018-08-13 09:29:10

。FPGA曾一度被認(rèn)為是僅用于開(kāi)發(fā)的解決方案,但如今其價(jià)位下降非常迅速,使得許多問(wèn)題迎刃而解,甚至能以低于傳統(tǒng)ASIC或ASSP解決方案的總體系統(tǒng)成本投產(chǎn)。現(xiàn)在,面向汽車(chē)市場(chǎng)的各大FPGA供應(yīng)商均已通過(guò)ISO-TS16949認(rèn)證,使得可編程邏輯器件逐漸成為汽車(chē)市場(chǎng)的主流技術(shù)。

2019-08-27 08:20:49

目前FIR濾波器的硬件實(shí)現(xiàn)的方式有哪幾種?怎么在FPGA上實(shí)現(xiàn)FIR濾波器的設(shè)計(jì)?

2021-05-07 06:03:13

相比,能夠?yàn)橥ㄐ藕投嗝襟w應(yīng)用提供高達(dá)10倍速的更高的設(shè)計(jì)和驗(yàn)證能力。Synphony HLS為ASIC 和 FPGA的應(yīng)用、架構(gòu)和快速原型生成最優(yōu)化的RTL。Synphony HLS解決方案架構(gòu)圖

2019-08-13 08:21:49

如何去實(shí)現(xiàn)ESP32-CAM高性?xún)r(jià)比溫濕度監(jiān)控系統(tǒng)配網(wǎng)與上網(wǎng)方案的設(shè)計(jì)呢?

2022-02-22 07:36:33

求助大神,在FPGA上實(shí)現(xiàn)retinex算法 。。。

2013-05-08 23:29:41

個(gè)以上要求的數(shù)組,并放入到二維數(shù)組B中。最終只需要顯示B。3,以上代碼運(yùn)行效率最優(yōu)化。(即運(yùn)行時(shí)間最短)

2018-09-25 16:34:11

電源解決方案 那么,如何才能簡(jiǎn)化設(shè)計(jì)呢?幸運(yùn)的是,有多種解決方案都有助于實(shí)現(xiàn)簡(jiǎn)化。在本文中,我將重點(diǎn)介紹兩種能夠幫助您快速便捷地實(shí)現(xiàn)設(shè)計(jì)目標(biāo)的創(chuàng)新技術(shù)…

2022-11-23 07:14:47

脈沖耦合神經(jīng)網(wǎng)絡(luò)(PCNN)在FPGA上的實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)分類(lèi)功能,有報(bào)酬。QQ470345140.

2013-08-25 09:57:14

的運(yùn)行設(shè)備基礎(chǔ)上,進(jìn)行節(jié)能潛力的挖掘。為實(shí)現(xiàn)這種方案,首先對(duì)D座空調(diào)系統(tǒng)進(jìn)行系統(tǒng)檢測(cè),從空調(diào)各個(gè)方面進(jìn)行評(píng)估。通過(guò)技術(shù)手段,傳感技術(shù),無(wú)線通信技術(shù),數(shù)據(jù)處理技術(shù),給出優(yōu)化解決方案。系統(tǒng)可以通過(guò)傳感器

2020-06-24 22:44:41

雙電源自動(dòng)切換電路圖,外部對(duì)電池充電。尋求最優(yōu)化電路。和比較穩(wěn)定的29.4V鋰電管理IC。充電電流2A~3A

2019-11-01 09:33:38

本文推導(dǎo)出一種適合在FPGA上實(shí)現(xiàn)從RGB到Y(jié)CbCr。顏色空間變換的新算法,采用單片FPGA完成電路設(shè)計(jì),利用FPGA內(nèi)嵌DSP核實(shí)現(xiàn)乘法運(yùn)算,提高了轉(zhuǎn)換算法的運(yùn)行速度。

2021-04-29 06:57:57

我使用SIMULINK中的系統(tǒng)生成器設(shè)計(jì)了我的PID控制器浮點(diǎn)。我們可以使用生成的代碼在Zynq 7020 FPGA上實(shí)現(xiàn)設(shè)計(jì)嗎?或者我們需要在處理單元(ARM Cortex)上實(shí)現(xiàn)它?換句話說(shuō),我可以在FPGA上實(shí)現(xiàn)浮點(diǎn)而不是PS(處理器)嗎?謝謝。丹尼爾·穆罕

2019-09-03 10:14:00

軌采用單獨(dú)的高效率開(kāi)關(guān)穩(wěn)壓器實(shí)現(xiàn)低功耗和減少發(fā)熱所有開(kāi)關(guān)穩(wěn)壓器在 >2MHz 下工作,實(shí)現(xiàn)最優(yōu)尺寸和外部組件成本并降低 AM 無(wú)線波段的噪聲為電路板上的所有電源軌進(jìn)行電壓定序提供專(zhuān)用的 DDRx 內(nèi)存終端此電路經(jīng)過(guò)測(cè)試并包含設(shè)計(jì)注意事項(xiàng)

2018-11-19 15:00:01

。 這本書(shū)把多年推廣到諸多公司和工程師團(tuán)隊(duì)的經(jīng)驗(yàn)以及由專(zhuān)門(mén)的白皮書(shū)和應(yīng)用要點(diǎn)匯集的許多知識(shí)進(jìn)行濃縮,可以用來(lái)完善工程師的知識(shí),幫助他們成為高級(jí)的fpga設(shè)計(jì)者。...高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化

2012-03-01 14:59:23

高級(jí)FPGA設(shè)計(jì)、結(jié)構(gòu)、實(shí)現(xiàn)與優(yōu)化(Advanced FPGA Design Architecture, Implementation,and Optimization)

2013-12-10 14:16:25

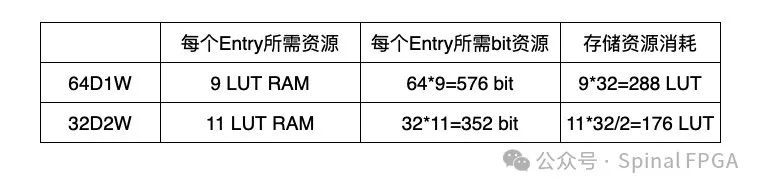

內(nèi)容可尋址存儲(chǔ)器CAM 是一種快速匹配存儲(chǔ)器件, 在通信、雷達(dá)等許多領(lǐng)域有著廣泛的應(yīng)用。本文在介紹CAM 基本原理的基礎(chǔ)上,提出在兩類(lèi)新型FPGA 上實(shí)現(xiàn)CAM 的設(shè)計(jì)方法,并對(duì)兩類(lèi)FP

2009-05-13 15:47:22 22

22 一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 步科推出CAM總線系統(tǒng)解決方案

CAM總線系統(tǒng)解決方案即是利用CAN總線的優(yōu)點(diǎn)及其特長(zhǎng)為機(jī)器自動(dòng)化設(shè)備提供高效、可靠、性?xún)r(jià)比高的解決方案。

2010-04-01 08:52:10 22

22 ADI公司為不同超聲平臺(tái)上實(shí)現(xiàn)成像質(zhì)量與功耗性能的最優(yōu)化

全球領(lǐng)先的高性能信號(hào)處理

2008-10-08 11:43:09 643

643 matlab最優(yōu)化實(shí)驗(yàn)6.1知識(shí)要點(diǎn)與背景6.1.1 由簡(jiǎn)入繁: 最佳水槽斷面問(wèn)題的推廣 6.1.2 微分法求最大和最小

2008-10-17 00:35:22 2231

2231 摘要: Ansoft 軟件能夠?qū)﹄姍C(jī)工作狀況進(jìn)行模擬,解決了電機(jī)模型分析困難的問(wèn)題。本文作者借助Ansoft 軟件分析各個(gè)參數(shù)對(duì) 發(fā)電機(jī)性能的影響,并對(duì)各參數(shù)進(jìn)行優(yōu)化設(shè)計(jì),最終確定了90 瓦永磁發(fā)電機(jī)的最優(yōu)化結(jié)構(gòu)參數(shù)。 關(guān)鍵詞:永磁發(fā)電機(jī);最優(yōu)化;磁路;參數(shù);氣

2011-03-01 15:03:05 0

0 介紹最優(yōu)化方法,其中包括網(wǎng)絡(luò)最大流,指派問(wèn)題,運(yùn)輸問(wèn)題,最短路,關(guān)鍵路線法,以及二部圖的匹配問(wèn)題。其使用方法有別于傳統(tǒng)方法,而是利用MATLAB構(gòu)造多個(gè)自編函數(shù),使所述問(wèn)

2011-11-30 16:41:34 0

0 高級(jí)FPGA設(shè)計(jì)結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化 作者:(美)克里茲著,孟憲元譯;出版社:機(jī)械工程出版社 學(xué)FPGA不一定需要開(kāi)發(fā)板,自己學(xué)會(huì)modelsim仿真、寫(xiě)testbench,用PC機(jī)仿真就能有不少長(zhǎng)進(jìn)。這

2012-11-28 14:03:22 0

0 電子發(fā)燒友網(wǎng)站提供《精通MATLAB最優(yōu)化計(jì)算(第2版).龔純等.掃描版_龔純/王正林.txt》資料免費(fèi)下載

2015-07-15 14:07:09 0

0 基于FPGA的SM3算法優(yōu)化設(shè)計(jì)與實(shí)現(xiàn)的論文

2015-10-29 17:16:51 4

4 基于FPGA實(shí)現(xiàn)POWERlink的方案

2015-11-17 15:55:08 19

19 SVPWM算法優(yōu)化及其FPGA_CPLD實(shí)現(xiàn)

2016-04-13 15:42:35 18

18 高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 15

15 高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化,適合于學(xué)習(xí)FPGA的進(jìn)階學(xué)習(xí)。

2016-05-11 16:40:55 14

14 最優(yōu)化方法及其Matlab程序設(shè)計(jì)

2016-12-17 20:59:43 0

0 基于最優(yōu)開(kāi)關(guān)角的逆變器諧波優(yōu)化研究_劉強(qiáng)

2016-12-28 14:24:14 0

0 混沌擴(kuò)頻SPWM最優(yōu)參數(shù)選取方法及其在FPGA上的實(shí)時(shí)實(shí)現(xiàn)_朱少平

2017-01-08 10:57:06 0

0 機(jī)器學(xué)習(xí)算法之最優(yōu)化方法

2017-09-04 10:05:10 0

0 現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 2990

2990 作為賽靈思用戶(hù)論壇的定期訪客(見(jiàn) ),我注意到新用戶(hù)往往對(duì)時(shí)序收斂以及如何使用時(shí)序約束來(lái)達(dá)到時(shí)序收斂感到困惑。為幫助 FPGA設(shè)計(jì)新手實(shí)現(xiàn)時(shí)序收斂,讓我們來(lái)深入了解時(shí)序約束以及如何利用時(shí)序約束實(shí)現(xiàn)

2017-11-24 19:37:55 4932

4932

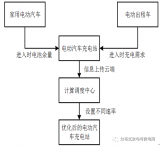

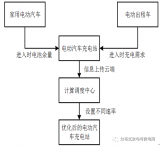

充電站最大化其收入與電力系統(tǒng)最大化其負(fù)載因子形成一個(gè)多目標(biāo)優(yōu)化問(wèn)題。本文提出多目標(biāo)最優(yōu)化方法來(lái)解決此多目標(biāo)優(yōu)化問(wèn)題,進(jìn)而產(chǎn)生柏雷多(Pareto)最優(yōu)電動(dòng)汽車(chē)充電策略。文末進(jìn)行數(shù)值分析來(lái)驗(yàn)證所提出方法的有效性。

2018-01-16 13:52:29 5993

5993

最優(yōu)化方法是一種數(shù)學(xué)方法,它是研究在給定約束之下如何尋求某些因素(的量),以使某一(或某些)指標(biāo)達(dá)到最優(yōu)的一些學(xué)科的總稱(chēng)。

2019-01-17 09:25:05 2442

2442

的效率將大大降低。然而,由于時(shí)間緊張、計(jì)算資源不足,很多組織架構(gòu)沒(méi)有采用最優(yōu)方案。更重要的是,我們用于解決大量優(yōu)化問(wèn)題的方法仍有很大的改進(jìn)空間。

2019-03-06 10:44:49 2846

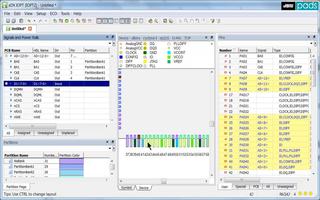

2846 與 FPGA 軟件工具進(jìn)行自動(dòng)雙向信息交換可提供由供應(yīng)商規(guī)則驅(qū)動(dòng)的“設(shè)計(jì)即正確”的 I/O 分配,從而實(shí)現(xiàn)快速、無(wú)誤的優(yōu)化流程。其包括了最新的器件支持,并且可提前訪問(wèn)尚未發(fā)布的 FPGA 供應(yīng)商器件。

2019-05-16 06:13:00 3407

3407

本文檔的主要內(nèi)容詳細(xì)介紹的是如何使用Xilinx的FPGA對(duì)高速PCB信號(hào)實(shí)現(xiàn)優(yōu)化設(shè)計(jì)。

2021-01-13 17:00:59 25

25 綜合就是針對(duì)給定的電路實(shí)現(xiàn)功能和實(shí)現(xiàn)此電路的約束條件,如速度、功耗、成本及電路類(lèi)型等,通過(guò)計(jì)算機(jī)進(jìn)行優(yōu)化處理,獲得一個(gè)能滿足上述要求的電路設(shè)計(jì)方案。被綜合的文件是HDL文件(或相應(yīng)文件等),綜合

2021-01-20 16:27:00 8

8 在選取較優(yōu)化的指紋識(shí)別預(yù)處理算法的基礎(chǔ)上,根據(jù)算法的結(jié)構(gòu)選取具有并行處理、低功耗、速度快等特點(diǎn)的FPGA作為實(shí)現(xiàn)算法的基本器件。由于用FPGA實(shí)現(xiàn)復(fù)雜算法較傳統(tǒng)器件從思考角度和實(shí)現(xiàn)方向上都有很大區(qū)別,所以本次設(shè)計(jì)從新的方向來(lái)完成傳統(tǒng)的指紋處理的設(shè)計(jì)。實(shí)際結(jié)果表明FPGA基本達(dá)到了設(shè)計(jì)的最初要求。

2021-02-03 15:53:00 11

11 LLC諧振變換器的理論分析與最優(yōu)化設(shè)計(jì)。

2021-05-13 10:44:49 65

65 主要研究問(wèn)題解的最優(yōu)性條件、靈敏度分析、解的存在性和一般復(fù)雜性等.而最優(yōu)化方法研究包括構(gòu)造新算法、證明解的收斂性、算法的比較和復(fù)雜性等.最優(yōu)化的應(yīng)用研究則包括算法的實(shí)現(xiàn)、算法的程序、軟件包及商業(yè)化、在實(shí)際問(wèn)題的應(yīng)用

2021-10-28 11:12:16 1870

1870 的設(shè)計(jì)與實(shí)現(xiàn)第四篇:ESP32-CAM創(chuàng)建熱點(diǎn)構(gòu)成并發(fā)式DNS服務(wù)器第五篇:ESP32-CAM高性?xún)r(jià)比溫濕度監(jiān)控系統(tǒng)第六篇:ESP32-CAM高性?xún)r(jià)比溫濕度監(jiān)控系統(tǒng)配網(wǎng)與上網(wǎng)方案設(shè)計(jì)與實(shí)現(xiàn)文章目錄ESP32-CAM ArduinoIDE開(kāi)發(fā)系列文章目錄前言一、ESP32-CAM高性?xún)r(jià)比溫濕度監(jiān)

2021-12-29 19:05:21 18

18 作為愛(ài)立信認(rèn)知軟件產(chǎn)品組合的一部分,“愛(ài)立信性能優(yōu)化器(Ericsson Performance Optimizers)”采用了數(shù)字孿生技術(shù),以及深度強(qiáng)化學(xué)習(xí)等先進(jìn)AI技術(shù),充分利用網(wǎng)絡(luò)優(yōu)化技術(shù)的自動(dòng)化、可擴(kuò)展性、速度、精度和一致性,同時(shí)實(shí)現(xiàn)用戶(hù)體驗(yàn)最優(yōu)化與運(yùn)營(yíng)商效益最大化。

2022-05-10 11:36:39 940

940 根據(jù),在線性可分情況下,支持向量機(jī)尋找最優(yōu)分類(lèi)超平面的優(yōu)化問(wèn)題

2023-05-11 11:13:07 997

997

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 ? FPGA 高級(jí)設(shè)計(jì)之實(shí)現(xiàn)功耗優(yōu)化 與ASICs(Application Specific Integrated Circuits)比較,相似的邏輯功能,用FPGA來(lái)實(shí)現(xiàn)

2023-05-19 13:50:02 869

869 本文詳細(xì)描述了FPGA實(shí)現(xiàn)圖像去霧的實(shí)現(xiàn)設(shè)計(jì)方案,采用暗通道先驗(yàn)算法實(shí)現(xiàn),并利用verilog并行執(zhí)行的特點(diǎn)對(duì)算法進(jìn)行了加速;

2023-06-05 17:01:45 886

886

? 這是筆者去年某個(gè)時(shí)間節(jié)點(diǎn)的感悟,由于工作繁忙,寫(xiě)完后擱置一邊了。而對(duì)于“設(shè)計(jì)最優(yōu)化”這個(gè)議題,筆者也一直深感功力不夠,不敢多做闡釋。但是,不管怎樣,若能每隔幾年都好好做些反思回顧,讓自己

2023-06-25 15:46:02 399

399 電子發(fā)燒友網(wǎng)站提供《SDAccel環(huán)境剖析和最優(yōu)化指南.pdf》資料免費(fèi)下載

2023-09-15 11:37:58 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論