今天給大俠帶來基于FPGA的內存128M flash芯片控制器設計,話不多說,上貨。 ? ? 設計原理及思路

FLASH閃存?閃存的英文名稱是"Flash Memory",一般簡稱為"Flash",它屬于內存器件的一種,是一種不揮發性( Non-Volatile )內存。

閃存的物理特性與常見的內存有根本性的差異:目前各類 DDR 、 SDRAM 或者 RDRAM 都屬于揮發性內存,只要停止電流供應內存中的數據便無法保持,因此每次電腦開機都需要把數據重新載入內存;閃存在沒有電流供應的條件下也能夠長久地保持數據,其存儲特性相當于硬盤,這項特性正是閃存得以成為各類便攜型數字設備的存儲介質的基礎。

本次設計使用的是 W25Q128FV 內存128M的flash芯片,大家可以自己在官網上下載器件手冊。在這里為了方便,也提供給各位,需要使用的可以在公眾號內部回復“W25Q128FV手冊資料”,各位可以根據實際項目應用靈活設計。

這款flash芯片的的存儲是一個扇區4KB,一個扇區可以存256個字,一個字是8位,一個塊是64KB,一共有256個塊組成一個存儲flash內存。

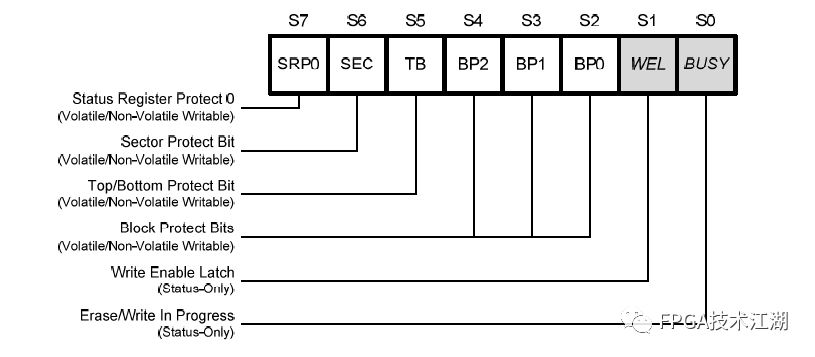

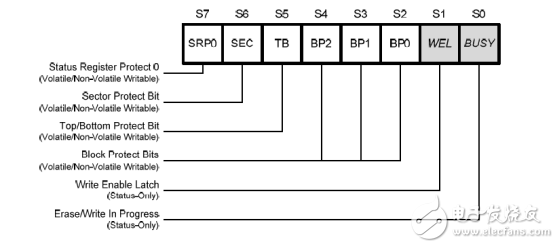

在下面的講解中,將主要講實現一下字節的讀寫,本次設計使用的協議是SPI協議,這個芯片支持QSPI,雙端口SPI等。flash有三個狀態寄存器,每一個狀態寄存器的每一位都有各自的功能。大家可以具體的看器件手冊,首先給大家簡單的講一下第一個狀態寄存器。

這個狀態寄存器第一位是可讀、忙和不忙的標志位,大家可以在我們的設計中判斷芯片是否忙和不忙來是否進行下一步的操作。第二位是一個寫標志的信號,當寫使能打開的時候它為1,只有它為1的時候我們才可以進行寫,值得一說的不管是頁操作,還是擦除等命令后都會使這個標志位變成0。然后前面的命令算的上的是保護命令,具體有使用的邏輯功能。

在flash中,寫數據前先要擦除數據(想要擦除的地方),然后進行寫,如果沒有用過的flash芯片的話那么可以不用擦除,因為flash掉電不丟失數據。

設計思路大概是先讀出器件廠商和芯片ID,然后寫命令,寫使能打開,頁操作寫入數據(值得說明的是我們FLASH是新的所以沒進行擦除命令,建議擦除---關閉寫使能 -- 打開寫使能),然后讀第一個寄存器判斷芯片的第一位是否忙,不忙然后進行讀操作之后再數碼管上顯示出我們寫入的數據。

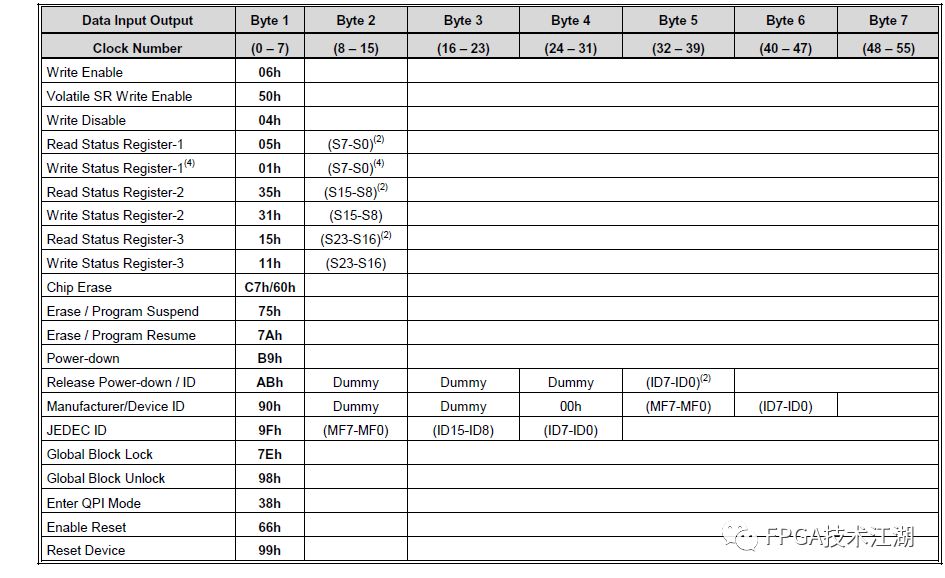

部分操作命令如下:

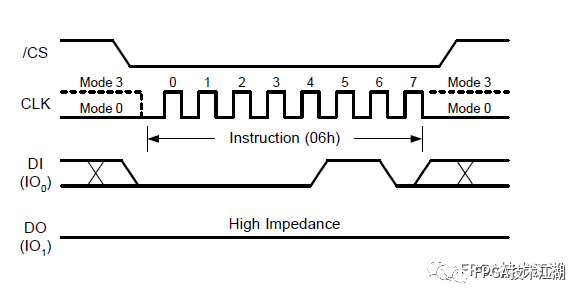

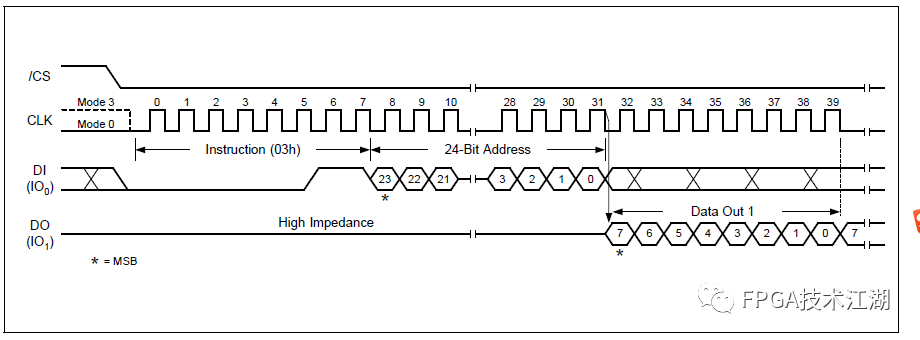

我們的發送格式為在時鐘的上升沿寫入命令,在時鐘的下降沿讀出命令,用的是標準的SPI協議,端口IO0,和IO1,都是單向的。

寫使能時序:

讀使能時序:

其他的時序在這里就不分別列舉出來了,大家可以參考器件手冊。

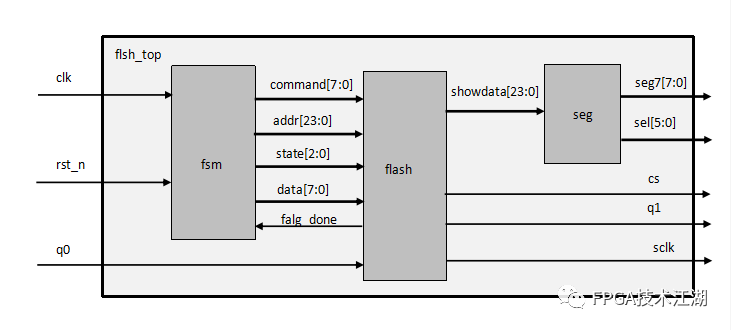

設計架構

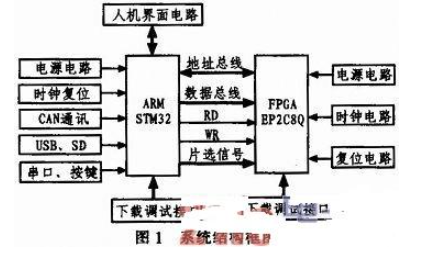

本次的設計是用一個FSM控制器來控制發送什么命令,flash模塊判斷FSM發送過來的state信號來選擇應該執行什么操作,當命令寫入或者讀出后,會發送一個flag_done命令,這個命令讓我們判斷上個指令是否完成,如果完成后FAM將發送下一個命令。總體架構圖如下:

設計代碼

頂層模塊 flash_top 代碼:

?

?

module flash_top(clk , rst_n, q0, q1, sclk, cs, seg, sel); input clk, rst_n; input q0; output q1; output sclk; output cs; output [5:0] sel; output [7:0] seg; wire [7:0] command; wire [23:0] addr; wire [2:0] state; wire [7:0] data; wire [23:0] show_data; wire flag_done; flash flash_dut( .clk(clk) , .rst_n(rst_n), .q0(q0), .q1(q1), .sclk(sclk), .cs(cs), .command(command), .addr(addr), .state(state), .data(data), .show_data(show_data), .flag_done(flag_done) ); fsm fsm_dut( .clk(clk), .rst_n(rst_n), .flag_done(flag_done), .command(command), .addr(addr), .state(state), .data(data) ); seg seg_dut( .clk(clk), .rst_n(rst_n), .sel(sel), .seg7(seg), .data_in(show_data) ); endmodule?

?

?

設計模塊 fsm?代碼:

?

?

module fsm(clk, rst_n, flag_done, command, addr, state, data);

input clk, rst_n;

input flag_done; //輸入標志位

output reg [7:0] command; //輸出命令

output reg [23:0] addr; //輸出地址

output reg [2:0] state; //輸出狀態模式

output reg [7:0] data; //輸出寫入數據

reg [2:0] state_s;

reg [20:0] count;

always @ (posedge clk)

if(!rst_n)

begin

state_s <= 0;

data <= 8'd0;

addr <= 24'd0;

command <= 8'd0;

state <= 0;

count <= 0;

end

else

case (state_s)

0 : begin

if(count < 200) //延遲一段時間

count <= count + 1;

else

begin //發送讀廠商ID的命令

command <= 8'h90;

addr <= 24'd0;

state <= 1;

count <= 1;

end

if(flag_done) //檢查是否完成

state_s <= 1;

end

1 : begin

if(count < 200) //延遲一段時間

count <= count + 1;

else

begin //寫使能

command <= 8'h06;

state <= 3;

count <= 0;

end

if(flag_done) //檢查是否完成

state_s <= 2;

end

2 : begin

if(count < 200) //延遲一段時間

count <= count + 1;

else

begin //頁操作

command <= 8'h02;

addr <= 24'd0;

state <= 4;

data <= 8'haa;

count <= 0;

end

if(flag_done) //檢查是否完成

state_s <= 3;

end

3 : begin

if(count < 200) //延遲一段時間

count <= count + 1;

else

begin //讀寄存器

command <= 8'h05;

count <= 0;

state <= 5;

end

if(flag_done) //檢查是否完成

state_s <= 4;

end

4 : begin

if(count < 200) //延遲一段時間

count <= count + 1;

else

begin //讀數據

command <= 8'h03;

addr <= 24'd0;

state <= 2;

count <= 0;

end

end

default: state_s <= 0;

endcase

endmodule

?

?

中間模塊flash代碼:

?

?

module flash (clk , rst_n, q0, q1, sclk, cs, command, addr, state, data, show_data, flag_done); input clk, rst_n; input q0; output reg q1; output reg sclk; output reg cs; input [7:0] command; //輸入命令 input [23:0] addr; //地址 input [2:0] state; //狀態 input [7:0] data; //數據 output reg [23:0] show_data; //顯示 output reg flag_done; //命令完成標志 reg [5:0] count; reg [5:0] cnt; reg [31:0] temp; reg [15:0] d; reg [5:0] count_s; reg [7:0] dou; reg [39:0] xie; reg [7:0] r_reg; always @ (posedge clk) if(!rst_n) begin sclk <= 1; count_s <= 0; end else if(cs) begin count_s <= 0; sclk <= 1; end else begin if(count_s == 25 - 1) //產生1M的時鐘 begin count_s <= 0; sclk <= ~sclk; end else count_s <= count_s + 1; end reg [1:0] signle_s; //邊沿檢測電路 always @ (posedge clk or negedge rst_n) if(!rst_n) begin signle_s <= 2'b11; end else begin signle_s[0] <= sclk; signle_s[1] <= signle_s[0]; end assign pose_dge = signle_s[0] && ~signle_s[1]; //上升沿脈沖 assign nege_dge = ~signle_s[0] && signle_s[1]; //下降沿脈沖 reg [1:0] s; reg [1:0] s1,s2,s3,s4; always @ (posedge clk or negedge rst_n) if(!rst_n) begin q1 <= 0; count <= 0; cs <= 1; temp <= 0; d <= 0; cnt <= 0; s <= 0; s1 <= 0; s2 <= 0; s3 <= 0; flag_done <= 0; s4 <= 0; end else begin if (state == 1) //state == 1進入讀芯片的廠商和ID case (s) 0: begin cs <= 0; temp <= {command,addr}; s <= 1; end 1 : begin if(nege_dge) //下降沿發送數據 begin if(count < 32) begin q1 <= temp[31]; count <= count + 1; temp <= {temp[30:0],temp[31]}; end else begin count <= 0; s <= 2; end end else q1 <= q1; end 2 : begin if(pose_dge) //上升沿采集數據 begin if(count < 16) begin count <= count + 1; d <= {d[14:0],q0}; end else begin s <= 3; cs <= 1; count <= 0; flag_done <= 1; show_data <= d; end end else begin s <= 2; end end 3 : begin flag_done <= 0; end endcase else if(state == 2) //state == 2進入讀模式 case (s1) 0: begin cs <= 0; temp <= {command,addr}; s1 <= 1; end 1 :begin if(nege_dge) begin if(count < 32) begin q1 <= temp[31]; count <= count + 1; temp <= {temp[30:0],temp[31]}; end else begin count <= 0; s1 <= 2; end end else q1 <= q1; end 2 : begin if(pose_dge) begin if(count < 8) begin count <= count + 1; dou <= {dou[6:0],q0}; s1 <= 2; end else begin s1 <= 3; cs <= 1; count <= 0; flag_done <= 1; show_data <= dou; end end else begin s1 <= 2; end end 3 : begin flag_done <= 0; end endcase else if(state == 3) //state == 3 進入寫使能模式 case (s2) 0: begin cs <= 0; temp <= {command,addr}; s2 <= 1; end 1 :begin if(nege_dge) begin if(count < 8) begin q1 <= temp[31]; count <= count + 1; temp <= {temp[30:0],temp[31]}; end else begin count <= 0; s2 <= 2; cs <= 1; flag_done <= 1; end end else q1 <= q1; end 2 : flag_done <= 0; endcase else if(state == 4) //state == 4 進入頁寫操作 case (s3) 0: begin cs <= 0; xie <= {command,addr,data}; s3 <= 1; end 1 :begin if(nege_dge) begin if(count < 40) begin q1 <= xie[39]; count <= count + 1; xie <= {xie[38:0],xie[39]}; end else begin count <= 0; s3 <= 2; cs <= 1; flag_done <= 1; end end else q1 <= q1; end 2 : flag_done <= 0; endcase else if(state == 5) //state == 5 進入讀第一個狀態寄存器操作 case (s4) 0: begin cs <= 0; r_reg <= command; s4 <= 1; end 1 :begin if(nege_dge) begin if(count < 8) begin q1 <= r_reg[7]; count <= count + 1; r_reg <= {r_reg[6:0],r_reg[7]}; end else begin count <= 0; s4 <= 2; end end else q1 <= q1; end 2 : begin if(pose_dge) begin if(count < 8) begin count <= count + 1; d <= {d[14:0],q0}; end else begin cs <= 1; count <= 0; if(!d[8]) //判斷BUSY位忙不忙,不忙進入下個狀態 begin flag_done <= 1; s4 <= 3; end else //忙繼續讀第一個寄存器 s4 <= 0; end end else begin s4 <= 2; end end 3 : flag_done <= 0; endcase end endmodule

?

?

數碼管模塊seg代碼: ?

?

module seg(clk,rst_n,sel,seg7,data_in);

input clk;

input rst_n;

input [23:0] data_in;

output reg [5:0] sel;

output reg [7:0] seg7;

parameter s0 = 3'b000;

parameter s1 = 3'b001;

parameter s2 = 3'b010;

parameter s3 = 3'b011;

parameter s4 = 3'b100;

parameter s5 = 3'b101;

`define T1ms 50_000

//`define T1ms 5

reg [15:0] count;

reg flag;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

begin

count <= 16'd0;

flag <= 1;

end

else

if(count == (`T1ms / 2 - 1))

begin

count <= 16'd0;

flag <= ~ flag;

end

else

begin

count <= count + 1'b1;

end

reg [2:0] state;

reg [3:0] num;

always @ (posedge flag or negedge rst_n)

if(!rst_n)

begin

sel <= 3'b0;

state <= 3'b0;

num <= 4'b0;

end

else

begin

case (state)

s0:begin

state <= s1;

sel <= 6'b011111;

num <= data_in[23:20];

end

s1:begin

state <= s2;

sel <= 6'b101111;

num <= data_in[19:16];

end

s2:begin

state <= s3;

sel <= 6'b110111;

num <= data_in[15:12];

end

s3:begin

state <= s4;

sel <= 6'b111011;

num <= data_in[11:8];

end

s4:begin

state <= s5;

sel <= 6'b111101;

num <= data_in[7:4];

end

s5:begin

state <= s0;

sel <= 6'b111110;

num <= data_in[3:0];

end

default:state <= s0;

endcase

end

always @ (*)

begin

case (num)

0:seg7 = 8'b1100_0000;

1:seg7 = 8'b1111_1001;

2:seg7 = 8'b1010_0100;

3:seg7 = 8'b1011_0000;

4:seg7 = 8'b1001_1001;

5:seg7 = 8'b1001_0010;

6:seg7 = 8'b1000_0010;

7:seg7 = 8'b1111_1000;

8:seg7 = 8'b1000_0000;

9:seg7 = 8'b1001_0000;

10:seg7 = 8'b1000_1000;

11:seg7 = 8'b1000_0011;

12:seg7 = 8'b1100_0110;

13:seg7 = 8'b1010_0001;

14:seg7 = 8'b1000_0110;

15:seg7 = 8'b1000_1110;

default:;

endcase

end

endmodule

?

?

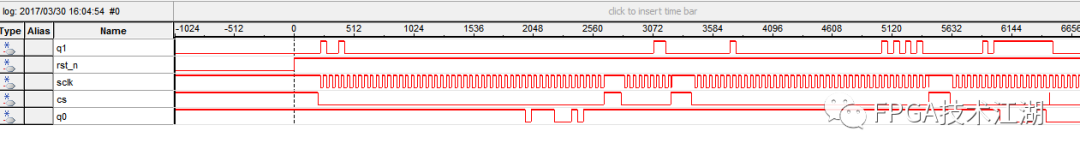

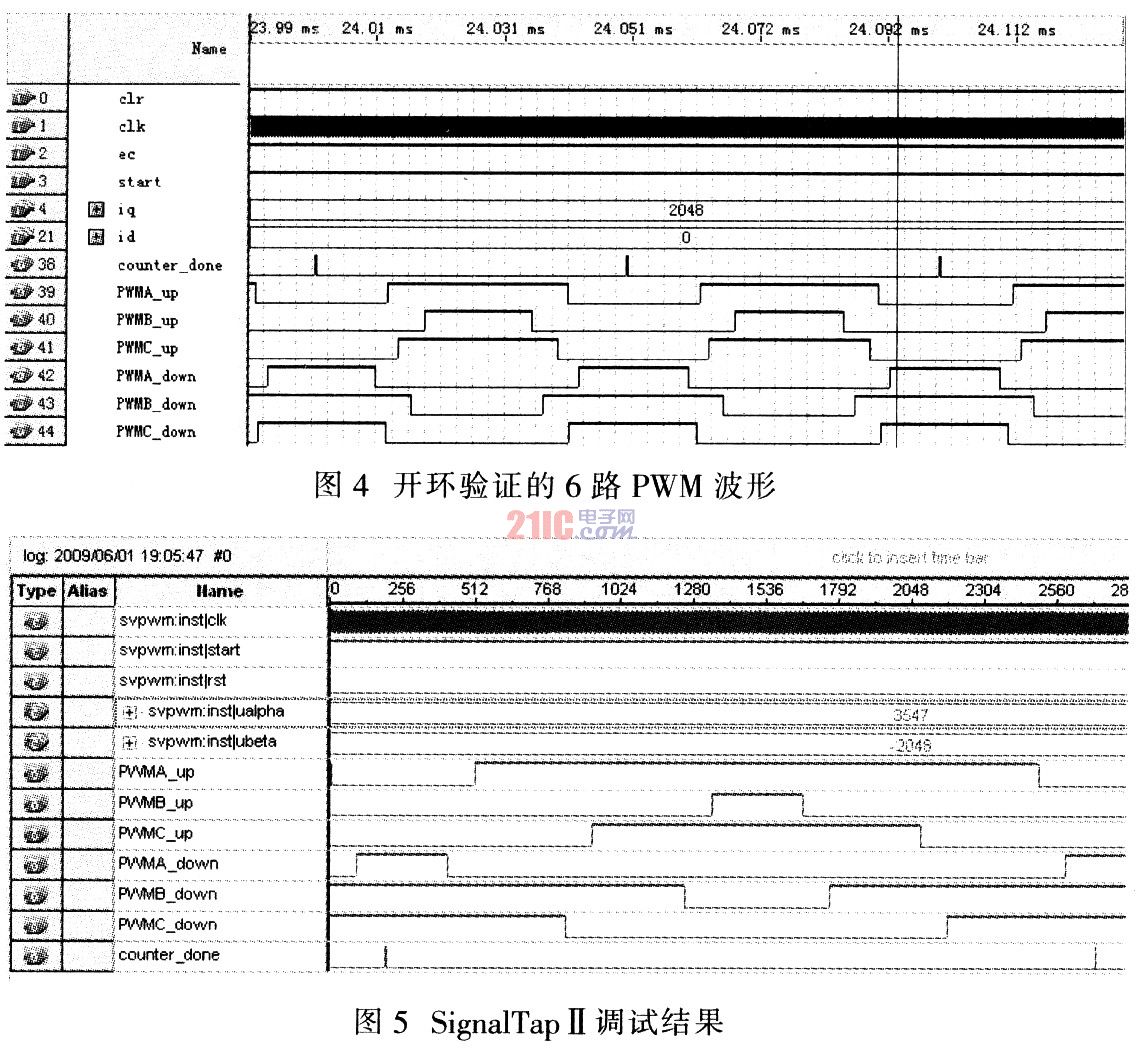

SignalTap 采集圖

圖中顯示的和我們的設計一樣,發送的各個命令也是一樣的,我們寫入的是AA然后接收的也是AA,設計正確。

審核編輯:黃飛

?

電子發燒友App

電子發燒友App

評論