對于使用安謀國際(ARM)處理器的系統(tǒng)單芯片(SoC)設(shè)計者而言,在原型制作的階段經(jīng)常會面臨如何整合處理器的問題。本文以賽靈思(Xilinx)的Zynq為例,說明如何應(yīng)用內(nèi)嵌安謀國際核心的現(xiàn)場可編程門陣列(FPGA)做為安謀國際核心測試芯片,進而建構(gòu)SoC原型制作平臺。

驗證SoC設(shè)計 FPGA原型最穩(wěn)當(dāng)

FPGA原型制作是在FPGA上實作SoC或特定應(yīng)用集成電路(ASIC)設(shè)計的方法,并進行硬件驗證和早期軟件開發(fā)。藉由這個接近真實ASIC的實作方式,設(shè)計人員可以用接近實時的速度,在真實的處理器上做軟件測試與系統(tǒng)整合。

由于半導(dǎo)體制程的快速進步,每片芯片上可以放進的晶體管數(shù)目急遽增加,因此SoC的設(shè)計也變得更加龐大且復(fù)雜。芯片設(shè)計人員開始發(fā)現(xiàn)由于執(zhí)行速度太慢和模型準確性的限制,光靠軟件仿真來驗證硬件設(shè)計是不夠的。更嚴重的是,SoC的設(shè)計錯誤,常會隱藏在系統(tǒng)深處,只有在軟硬件之間復(fù)雜的互動情形下,才會呈現(xiàn)出來,因此及早開始進行軟件和韌體開發(fā)變得更加重要,而在這個階段也只有FPGA原型的速度足以執(zhí)行復(fù)雜的操作系統(tǒng)和軟件應(yīng)用。總的來說,只有用FPGA原型來驗證SoC設(shè)計才是最可靠的方法,且藉由FPGA原型才能做到軟件和硬件的并行開發(fā)(圖1)。

圖1 SoC設(shè)計流程中的FPGA原型制作

借力測試芯片與核心板 SoC原型整合處理器迎刃解

大多數(shù)的SoC設(shè)計都包含一個或多個處理器。隨著所采用處理器的不同,其來源對原型制作的支持形式也迥異,可能是用來刻錄在FPGA里的緩存器轉(zhuǎn)化層(RTL)程序或已經(jīng)編譯和優(yōu)化的比特流(Bitstream),也可能是電路板上面載有處理器芯片或已刻錄線路的FPGA。

對于使用安謀國際處理器的SoC設(shè)計者而言,在原型制作的階段常會面臨如何整合處理器的問題。一般的解決方式如下:

測試芯片

測試芯片(Test Chip)是安謀國際和合作廠商為了驗證新的處理器設(shè)計和制程所制作的芯片,因此測試芯片中包含安謀國際處理器硅智財(SIP),以及一些必需的邏輯線路,如控制頻率用的鎖相回路(PLL)和頻率分頻器(Clock Divider),及邊界掃描(Boundary Scan)測試線路等。測試芯片常會對內(nèi)嵌處理器的接口訊號做處理,以減少所需的接腳數(shù)目,從而降低封裝成本,如把多個先進微控制器總線架構(gòu)(AMBA)接口用多任務(wù)方式(Multiplexed)變成一組外接訊號。

測試芯片和一般內(nèi)嵌安謀國際處理器的SoC最大不同之處,即在于它提供直接從處理器AMBA界面拉出來的接腳,因此使用測試芯片便可以把兼容于AMBA界面的周邊設(shè)計接上處理器,從而形成完整的應(yīng)用系統(tǒng)。

測試芯片內(nèi)的安謀國際處理器可以提供接近ASIC的執(zhí)行速度,不過測試芯片制作成本甚高,一般很難取得。

核心板

一般開發(fā)者只能以核心板(Core Tile)的型式取得具有AMBA外接接口的安謀國際處理器芯片。

核心板是上面載有測試芯片的子板,且板上的連接器提供測試芯片的AMBA接口訊號。核心板是安謀國際開發(fā)平臺的一部分,須裝在基板(Baseboard)上使用,由基板提供電源、內(nèi)存及周邊,若是要擴充FPGA可以再加上可程序邏輯板(Logic Tile);這些開發(fā)板合起來構(gòu)成完整的原型系統(tǒng),讓開發(fā)者用來評估處理器、進行效能測試、開發(fā)軟件或驗證IP設(shè)計(圖2)。開發(fā)者可以購買到這些開發(fā)板,不過價錢并不便宜。

圖2 ARM開發(fā)平臺

另有部分市售的FPGA原型制作平臺亦使用核心板加入安謀國際處理器,這些平臺的共同點為提供FPGA和核心板之間的連接方式,如透過另一子板及其上的高速連接器,以轉(zhuǎn)接核心板到原型制作平臺上。

由于核心板上測試芯片接口訊號的接腳眾多,若設(shè)計者欲把核心板連接到自制的FPGA原型制作平臺上,在設(shè)計時就要考慮到接口和連接的問題。

對于使用安謀國際(ARM)處理器的系統(tǒng)單芯片(SoC)設(shè)計者而言,在原型制作的階段經(jīng)常會面臨如何整合處理器的問題。本文以賽靈思(Xilinx)的Zynq為例,說明如何應(yīng)用內(nèi)嵌安謀國際核心的現(xiàn)場可編程門陣列(FPGA)做為安謀國際核心測試芯片,進而建構(gòu)SoC原型制作平臺。

內(nèi)嵌ARM核心的FPGA傾巢出

SoC FPGA并不是新產(chǎn)品,這類結(jié)合硬式核心(Hard-core)處理系統(tǒng)和可程序邏輯的產(chǎn)品,早就用在除了處理器和周邊之外,另須外加邏輯的應(yīng)用中。它的可程序邏輯可用來進行大量運算或訊號處理,以提升系統(tǒng)整體效能;此外,這類產(chǎn)品亦可做為許多應(yīng)用的單芯片解決方案。

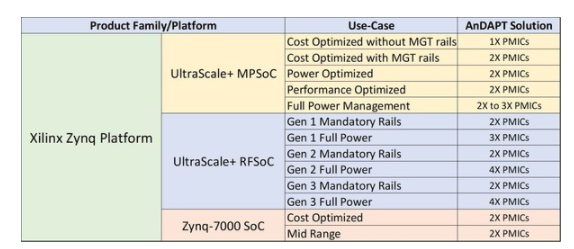

過去這類產(chǎn)品的硬式核心處理器多采用PowerPC核心,不過隨著安謀國際核心的普及,目前已有三家廠商推出內(nèi)嵌安謀國際核心的FPGA,其中美高森美(Microsemi)的SmartFusion內(nèi)嵌應(yīng)用廣泛的Cortex-M3硬式核心微控制器(MCU),而Altera的Cyclone V和Arria V系列,以及賽靈思的Zynq-7000系列都選擇內(nèi)嵌更高效能的雙核心Cortex-A9處理器。

借助Zynq開發(fā)SoC原型實作

Zynq包含處理系統(tǒng)(Processing System, PS)和可程序邏輯(Programmable Logic, PL)兩部分(圖3)。

圖3 Zynq FPGA功能方塊圖

PS處理系統(tǒng)是如同ASIC一般的固定硬件(Hard-wired),相當(dāng)于一個內(nèi)嵌于FPGA中既定架構(gòu)的安謀國際處理系統(tǒng),其包含雙核心、頻率可達800MHz的Cortex-A9處理器,及固定硬件的雙倍數(shù)據(jù)率(DDR)和閃存控制器;此外,固定硬件的部分還包含以太網(wǎng)絡(luò)(Ethernet)、第二代通用串行總線(USB)2.0、控制器局域網(wǎng)絡(luò)(CAN)、安全數(shù)字輸入/輸出(SDIO)、內(nèi)部整合電路(I2C)、串行周邊接口(SPI)、通用異步收發(fā)器(UART)和通用輸入/輸出(GPIO)等常見的嵌入式系統(tǒng)周邊。

Zynq-7000系列產(chǎn)品都內(nèi)嵌一樣的安謀國際處理系統(tǒng),但是PL可程序邏輯的大小則各有不同。兩個較大的產(chǎn)品容量分別相當(dāng)于一百九十萬和三百五十萬個ASIC邏輯閘,而兩個較小的產(chǎn)品容量分別相當(dāng)于四十三萬和一百三十萬個ASIC邏輯閘。

連接PS和PL的是AXI接口。安謀國際所制定的AMBA接口是SoC On-chip Bus的實際標準,它已為滿足芯片容量增加隨之而來的效能需求修訂好幾版,最新的規(guī)格就是AXI(Advanced eXtensible Interface)。

由此可知,Zynq FPGA即包含處理器核心和可程序邏輯,且使用和ASIC同樣的AXI接口連接,很明顯地它可以用作SoC原型制作,因此使用Zynq即能建構(gòu)一個支持Cortex-A9設(shè)計的原型制作平臺。

AXI接口評估要點

Zynq連接PS和PL的AXI接口有好幾種,各有不同的特性,因此當(dāng)你決定要用Zynq做為原型制作平臺時,馬上就面臨一個問題:在這幾種AXI接口之中,究竟要用哪個來做為處理器和SoC其他部分連接的原型?PL中的邏輯要跟哪個AXI接口連接才能接到處理器,而不只是接到處理系統(tǒng)的內(nèi)存控制器和周邊?

連接PS和PL的有三種AXI接口:通用(General-purpose)、高效能(High-performance)和加速器一致性端口(Accelerator Coherency Port, ACP)。對PS而言,有兩個到PL的通用Master AXI接口和兩個從PL來的通用Slave AXI接口。Master在這里指的是數(shù)據(jù)傳輸?shù)陌l(fā)起者,而Slave只能響應(yīng)數(shù)據(jù)傳輸?shù)囊蟆S的Master AXI接口一般是用來對PL中的周邊做傳輸,而Slave AXI接口則用來響應(yīng)PL的要求。此外,還有四個高效能(64位寬度)的AXI接口,這四個接口對PS來說都是Slave,且都接到PS里的內(nèi)存控制器,用來讓PL里的Master存取內(nèi)存。最后,ACP則是另一個從PL到PS的32位Slave AXI接口。

因此,若要用安謀國際處理器做為Master連接PL,必須用那兩個通用Master AXI接口。這兩個接口均相同,因此使用任一個皆可。

具功能擴充性 Zynq FPGA巧扮SoC原型平臺

對不具備印刷電路板(PCB)設(shè)計能力的公司而言,使用市售的FPGA原型制作平臺是最省時且有效的方法,但若使用這些平臺亦會受到既定系統(tǒng)配置與架構(gòu)限制,無法自由發(fā)展?jié)M足需求的系統(tǒng)架構(gòu),且在傳輸帶寬和執(zhí)行頻率方面也缺乏彈性。相反地,自行制作平臺就很容易滿足設(shè)計人員的需求,如可以在板上使用某些特定的周邊和組件等。

成本也是選擇自行制作平臺的一個考慮因素。為發(fā)配給每位團隊成員平行開發(fā)軟件,因此需要有多片平臺,使得自行制作所需的成本相較于購買市售平臺來得低廉。

為實現(xiàn)自主架構(gòu)SoC的原型制作,Zynq FPGA包含DDR、儲存型快閃(NAND Flash)和SPI Serial Flash等內(nèi)存控制器,以及互補式金屬氧化物半導(dǎo)體影像傳感器(CMOS Image Sensor)、液晶顯示器(LCD)、高分辨率多媒體接口(HDMI)、SD Card、USB Host、以太網(wǎng)絡(luò)、音頻編譯碼(Audio CODEC)、UART、GPIO和JTAG(Joint Test Action Group)等周邊界面(圖4)。

圖4 Zynq FPGA 原型制作平臺

至于PS內(nèi)的固定硬件周邊,雖然在驗證個別IP時可以加以應(yīng)用,但是它們還需要在板上有所屬的特定線路和組件才能使用,如此會大幅增加電路板布局的復(fù)雜度,因此只好放棄不用;不過若選擇使用固定硬件的DDR控制器,就可以在驗證工作一開始時,就有可以運作的DDR內(nèi)存功能。

此外,在板上還配置了擴充用連接器。用戶只要設(shè)計可以接到此連接器的電路板,即可擴充平臺的功能,這是擴充平臺功能最快也最省錢的方法;此外,它也可以用在連接其他FPGA板以擴充容量和周邊,或是用于對架構(gòu)的探索研究。

利用Zynq FPGA還可以實現(xiàn)「測試芯片模式(Test Chip Mode)」,也就是只使用Zynq做為安謀國際測試芯片,用來支持其他FPGA板的原型制作。實現(xiàn)「測試芯片模式」時,設(shè)計人員只須把Zynq內(nèi)處理器的AXI接口訊號經(jīng)過PL拉到外部接腳上即可。

當(dāng)要把AXI接口訊號拉到Zynq外部接腳時,若可用的接腳數(shù)目不夠,就要使用接腳多任務(wù)(Pin Multiplexing)或某些橋接(Bridging)的方法來減少使用接腳數(shù)目;以我們設(shè)計的橋接方式為例,用32位數(shù)據(jù)寬度做傳輸時所需的接腳數(shù)目為四十四(包括控制訊號);而用16位數(shù)據(jù)寬度做傳輸時所需的接腳數(shù)目為二十八。不過因為這些方法都是用犧牲傳輸帶寬的方式換取使用較少的接腳數(shù)目,因此會造成效能的下降。

針對用多片相同的Zynq FPGA板來做擴充的需求,板上的擴充用連接器也有特殊的配置:在板的左右兩側(cè)各配置有四十接腳的連接器,扣除電源接腳后每個連接器可用的接腳數(shù)目為二十八,正是前述橋接方式用16位數(shù)據(jù)寬度做傳輸時所需的接腳數(shù)目,如此使用多片Zynq FPGA板做板對板連接,即可分別支持32位數(shù)據(jù)寬度的雙板對接模式(圖5)和16位數(shù)據(jù)寬度的多板串接模式(圖6)。

圖5 Zynq FPGA板的板對板連接(32位數(shù)據(jù)寬度的雙板對接模式)

圖6 Zynq FPGA板的板對板連接(16位數(shù)據(jù)寬度的多板串接模式)

打造SoC原型制作平臺 FPGA SoC嶄露頭角

SoC的原型制作已是達成硬件驗證和及早進行軟件和韌體開發(fā)的主流方法。相較于找尋合適的處理器核心測試芯片或使用既定架構(gòu)的安謀國際原廠開發(fā)板,利用內(nèi)嵌安謀國際核心的FPGA即可輕松實現(xiàn)SoC的原型制作。

電子發(fā)燒友App

電子發(fā)燒友App

評論