針對雙天線干涉SAR 基線測量系統(tǒng)數(shù)據(jù)量大、實時性要求高和體積小的特點,設(shè)計并實現(xiàn)了一種基于FPGA + PCI 的實時數(shù)據(jù)采集存儲系統(tǒng)。 系統(tǒng)基于PCI 總線技術(shù),采用FPGA 和大容量SDRAM 對采集數(shù)據(jù)進行控制和緩存,利用多個硬盤組成的磁盤陣列進行實時存儲,實現(xiàn)了CCD 相機和激光測距儀與PCI 總線間的高速數(shù)據(jù)實時傳輸。 對系統(tǒng)進行了功能和性能測試,測試結(jié)果表明,系統(tǒng)數(shù)據(jù)吞吐量大,實時性強,性能穩(wěn)定,能夠有效地滿足基線測量系統(tǒng)的需求。雙天線干涉合成孔徑雷達系統(tǒng)可以獲取地面目標的高程信息,具有全天候、全天時工作、測繪范圍廣、分辨率高等優(yōu)點。干涉測量一般采用單軌雙天線或重復(fù)軌道單天線系統(tǒng),對于單軌雙天線系統(tǒng),其交軌干涉基線越長、越精確,獲取的高程精度越高。一般干涉基線長度大于4 m 時,基線呈柔性結(jié)構(gòu)而不能保持穩(wěn)定基線,由于柔性基線結(jié)構(gòu)出現(xiàn)的變形和抖動,會造成2 個天線的相對位置和姿態(tài)動態(tài)變化,并最終嚴重影響高程精度。 采用CCD 相機和激光測距儀的組合基線測量系統(tǒng)能夠?qū)崿F(xiàn)對2 個天線的位置和姿態(tài)變化進行精密動態(tài)測量,CCD 相機對布設(shè)在天線上LED 標志點進行高速跟蹤拍攝,激光測距儀同步測量平臺與合作目標之間的距離。 這使得柔性基線測量系統(tǒng)具有輸出數(shù)據(jù)量大、處理算法復(fù)雜、計算量大、處理實時性要求高等特點,本文針對柔性基線測量系統(tǒng)的需求,提出一種基于FPGA +PCI 的數(shù)據(jù)實時采集與高速存儲的解決方案,進行了硬件關(guān)鍵功能設(shè)計與實現(xiàn)。 系統(tǒng)采用FPGA進行核心邏輯控制,對CCD 相機和激光測距儀的數(shù)據(jù)進行同步采集控制,整理、利用外部大容量的SDRAM 組進行緩存,采用專用的PCI 接口芯片PLX9656,實現(xiàn)了2 個傳感器數(shù)據(jù)與PCI 總線數(shù)據(jù)的高速傳輸,利用多個SATA 硬盤構(gòu)成的大容量的磁盤陣列進行實時存儲。 并對該數(shù)據(jù)采集存儲系統(tǒng)進行了功能和性能測試,實測數(shù)據(jù)表明本文設(shè)計的系統(tǒng)能夠有效解決柔性基線測量系統(tǒng)數(shù)據(jù)高速采集,大容量數(shù)據(jù)傳輸?shù)碾y題。

1 系統(tǒng)組成及工作原理

1. 1 主要功能和技術(shù)指標

在柔性基線測量系統(tǒng)中,為了精確實時測量柔性基線的抖動和2 個天線相對姿態(tài)的變化,需要選擇高幀頻、大面陣的CCD 相機和高精度的激光測距儀進行組合測量,這樣會產(chǎn)生大量高速的圖像數(shù)據(jù)和激光測距儀輸出的距離數(shù)據(jù)。 因此本文設(shè)計的高速采集存儲系統(tǒng)主要功能是控制各測量傳感器之間的時間同步,完成各傳感器數(shù)據(jù)的實時采集,并對采集的數(shù)據(jù)進行分流。 一路數(shù)據(jù)進行高速存儲; 另一路數(shù)據(jù)輸出至另外的實時處理系統(tǒng)中。根據(jù)柔性基線測量系統(tǒng)的要求,本文系統(tǒng)應(yīng)該能夠?qū)崟r采集和存儲2 個傳感器測量數(shù)據(jù),需要達到的技術(shù)指標主要包括持續(xù)采集速度、持續(xù)存儲速度和最小存儲容量等。系統(tǒng)中CCD 相機采用SVS-VISTEK 公司生產(chǎn)的一款高分辨率、高幀頻的面陣數(shù)字相機,圖像的分辨率為1608 列× 1208 行,相機幀頻最高為30 Hz. 該相機數(shù)據(jù)AD 采樣為10 位,數(shù)據(jù)采集只取高8 位,則CCD 相機每秒產(chǎn)生的數(shù)據(jù)量約為55. 57 MB. 激光測距儀采用的是德國公司生產(chǎn)的LRFS-0040-2 激光測距儀,測量速率最高可達50Hz,數(shù)據(jù)接口采用的是RS 422 接口,產(chǎn)生的數(shù)據(jù)量為9. 6 KB / s.2 個傳感器每秒的數(shù)據(jù)量約為56 MB / s,則采集系統(tǒng)的持續(xù)采集速度必須大于56 MB / s,才能對2 個傳感器數(shù)據(jù)進行實時采集。只有當持續(xù)存儲速率大于采集速度時,才能夠把數(shù)據(jù)實時準確的存儲數(shù)據(jù)。 所以持續(xù)存儲速度要大于56 MB / s,SATA 硬盤理論讀寫速度最大可達150 MB / s,利用多個SATA 硬盤組成RAID陣列,可以提供比單個硬盤更高的存儲性能。

根據(jù)柔性基線測量系統(tǒng)的需求,該采集存儲系統(tǒng)的持續(xù)工作時間最長約為2 h,則需要的最小的存儲容量約為390. 76 GB.根據(jù)上述數(shù)據(jù)采集系統(tǒng)的需求分析,并考慮到系統(tǒng)的可擴展性以及數(shù)據(jù)實際傳輸、終端處理的需要,要求數(shù)據(jù)采集記錄速度要達到70 MB / s,持續(xù)寫盤陣速度要達到120 MB / s,存儲容量要求達到2 TB.對于32 bit /33 MHz 的PCI 總線,實際使用中一般能達到80 MB / s,數(shù)據(jù)進出系統(tǒng)內(nèi)存都要經(jīng)過PCI 總線,會導(dǎo)致總線的效率降低一半。 而系統(tǒng)的采集速度必須大于56 MB / s,所以選擇64 bit /66 MHz的PCI 總線,數(shù)據(jù)傳輸?shù)姆逯邓俣瓤梢赃_到528 MB / s,現(xiàn)有系統(tǒng)表明64 bit /66 MHz的PCI 總線實際傳輸?shù)乃俣饶苓_到200 MB / s 以上,所以該PCI 總線的傳輸速度完全能滿足系統(tǒng)需求。

1. 2 系統(tǒng)組成和整體方案

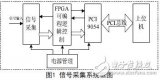

整個系統(tǒng)主要由CCD 相機、激光測距儀,PCI數(shù)據(jù)采集卡,SATA 磁盤陣列和計算機組成。 其中PCI 圖像采集卡主要由傳感器數(shù)據(jù)接口、FPGA 邏輯控制芯片、高速緩存、PCI 接口芯片組成。 本文提出一種基于FPGA + PCI 的數(shù)據(jù)采集存儲系統(tǒng)的解決方案,該方案的原理如下: 首先由主機端發(fā)送命令對CCD 相機和激光測距儀進行配置,配置完成后啟動采集,CCD 相機輸出的高速圖像數(shù)據(jù)、同步控制信號一起送到FPGA 中,在FPGA 中進行緩存,激光測距儀的數(shù)據(jù)通過串口也送入到FPGA 的雙口RAM 中進行緩存,F(xiàn)IFO 半滿后在FPGA 的控制下把CCD 相機和激光測距儀數(shù)據(jù)進行分流,其中一路送到外部的SDRAM 組中進行緩存,SDRAM 存儲到設(shè)定圖像幀數(shù)后給PCI 發(fā)送中斷,主機響應(yīng)中斷,從SDRAM 中把數(shù)據(jù)讀到內(nèi)存中進行處理,并同時向硬盤中寫數(shù)據(jù)完成實時存儲; 另一路送到相關(guān)的實時處理系統(tǒng)中進行處理。整個設(shè)計方案的框圖如圖1 所示。

圖1 數(shù)據(jù)實時采集與存儲系統(tǒng)設(shè)計方案框圖

應(yīng)用于柔性基線測量系統(tǒng)的數(shù)據(jù)實時,采集存儲系統(tǒng)的設(shè)計包括以下幾個方面的關(guān)鍵技術(shù):

Camera Link 接口技術(shù)、多傳感器同步技術(shù)、多傳感器數(shù)據(jù)的實時采集與高速緩存和多傳感器數(shù)據(jù)的實時存儲。

2 數(shù)據(jù)實時采集存儲系統(tǒng)關(guān)鍵設(shè)計與實現(xiàn)

下面對本系統(tǒng)中的幾個關(guān)鍵技術(shù)具體實現(xiàn)的設(shè)計方案進行詳細闡述。

2. 1 數(shù)據(jù)采集接口設(shè)計

實驗相機采用Camera Link 標準接口,基本配置采用標準的MDR26 連接器輸出。 本系統(tǒng)采用FPGA 作為采集卡的主控芯片,F(xiàn)PGA 支持的I /O 標準為LVCMOS /LVTTL 信號。 因此本系統(tǒng)對于Camera Link 接口的設(shè)計方案為: 通過DS90CR288A 接收器將4 路相機數(shù)據(jù)LVDS 信號和1 路相機時鐘LVDS 信號轉(zhuǎn)換成28 位TTL 數(shù)據(jù),輸出24 位圖像信號、圖像同步信號和像素時鐘信號Strobe. DS90CR288A 的主要功能是完成LVDS 到TTL 電平信號的轉(zhuǎn)換和串行信號轉(zhuǎn)成并行信號。 為了對相機進行參數(shù)設(shè)置和觸發(fā)控制,需要將FPGA 輸出的相機控制信號( CC1-CC4 )和信號SerTC( serial-to-camera) 通過電平轉(zhuǎn)換芯片DS90LV047 轉(zhuǎn)換成LVDS 信號送入接收器中。為了接收相機向采集卡發(fā)送的應(yīng)答信號SerTFG( serial-to-frame-grabber ) ,采用DS90LV048 把該LVDS 信號轉(zhuǎn)換成TTL 信號后送入FPGA 中,并送入主機端進行顯示。

2. 2 PCI 接口設(shè)計

由1. 1 節(jié)指標論證結(jié)果可知,本系統(tǒng)采用64bit /66 MHz 的PCI 總線來實現(xiàn)數(shù)據(jù)的高速傳輸。PCI 接口是PCI 總線與外部總線的通信接口,以實現(xiàn)二者的通信。 目前常用的PCI 接口的方案是采用專用的PCI 總線接口芯片,無需掌握復(fù)雜的PCI 總線協(xié)議,設(shè)計簡單,能夠減少開發(fā)周期和成本。 本系統(tǒng)中采用PLX9656 來進行高速PCI 卡的設(shè)計,以實現(xiàn)設(shè)置相機參數(shù)、設(shè)置激光測距參數(shù)、設(shè)置采樣參數(shù)、讀取圖像數(shù)據(jù)等功能。 PLX9656是目前性能最高的PCI 接口控制器,具有PCI 端66 MHz、64 bits,LOCAL 端66 MHz、32 bits 的性能,符合PCI V2. 2 規(guī)范。 本系統(tǒng)中PCI 接口設(shè)計的重點是PLX9656 本地總線工作方式和數(shù)據(jù)傳輸模式的設(shè)置與實現(xiàn)。 PLX9656 的本地總線可以設(shè)置成3 種模式: M 模式、C 模式和J 模式。 根據(jù)本系統(tǒng)的特點,選擇C 模式,可以通過把MODE1 和MODE0 引腳拉低來實現(xiàn)C 模式的工作方式。 在C 模式下,數(shù)據(jù)傳輸方式分為主模式操作、從模式操作和DMA 操作。 采用DMA 工作方式,能在不需要CPU 干預(yù)的條件下,實現(xiàn)高數(shù)外設(shè)和存儲器間的快速傳輸,因此比較適合CCD相機數(shù)據(jù)和激光測距儀數(shù)據(jù)的傳輸,DMA 傳輸方式的實現(xiàn)可以通過對PLX9656 的內(nèi)部寄存器的DMAMODE0 /1,PCICR置位來實現(xiàn)。

2. 3 FPGA 核心邏輯控制

基于FPGA 的時序邏輯控制模塊是本系統(tǒng)的核心設(shè)計,能夠?qū)崿F(xiàn)對相機和激光測距儀的模式設(shè)置、相機和激光測距儀的數(shù)據(jù)同步控制、多個傳感器數(shù)據(jù)的緩存與整理,對外部高速緩存的控制以及與PLX9656 的通信。 系統(tǒng)采用Altera 公司的Stratix Ⅱ系列EP2S60F1020 器件,配置芯片選用EPC16.

1) 傳感器觸發(fā)設(shè)置

本設(shè)計中,2個傳感器的工作模式通過主機端進行設(shè)置,通過PCI 總線將模式設(shè)置字符串傳到FPGA 中,通過串口控制器實現(xiàn)與相機和激光測距儀的通信,從而完成對相機和激光測距儀的配置。 且相機和激光測距儀收到配置命令后也通過串口控制器把應(yīng)答信息傳到FPGA 中,再通過PCI 總線傳到主機上。為了實現(xiàn)與激光測距儀的同步控制,相機選擇軟件外觸發(fā)模式,此模式下需要在FPGA 內(nèi)產(chǎn)生一個頻率為20 Hz 的EXSYNC 觸發(fā)信號送給CCD 相機進行曝光讀取數(shù)據(jù),EXSYNC 的低電平寬度為10 μs,相機的曝光時間由主機端進行參數(shù)設(shè)置。

2) 數(shù)據(jù)同步控制

把EXSYNC 觸發(fā)信號同時送給激光測距儀和相機,來實現(xiàn)2 個傳感器的輸出同步。 因為2個傳感器的測量速度不同,相機的輸出幀頻為20 幀/ s,激光測距儀的輸出頻率為50 Hz,所以數(shù)據(jù)同步的設(shè)計關(guān)鍵在于如何記錄同時刻的單幀圖像數(shù)據(jù)和激光測距儀數(shù)據(jù),2 個傳感器同步采集的時序關(guān)系圖如圖2 ( a) 所示,CLK 100 Hz 是取2 個頻率的最小公倍數(shù),可以根據(jù)FPGA 的內(nèi)部資源使用情況來設(shè)定,Data_lrf_sel 為選擇的激光數(shù)據(jù),其中I 表示該時刻的數(shù)據(jù)無效,V 表示該時刻的數(shù)據(jù)有效。數(shù)據(jù)同步方案為相機數(shù)據(jù)進入FPGA 后,在2 個雙口RAM 中進行整理緩存,激光測距儀經(jīng)過串口接收器把數(shù)據(jù)傳入FPGA 內(nèi),本設(shè)計的串口接收器帶有FIFO 緩存,數(shù)據(jù)經(jīng)過緩存后接送入雙口RAM 中進行進一步緩存; 按照圖2 ( a) 所示的時序關(guān)系圖生成雙口RAM 的寫使能WEN 信號,WEN 信號有效時把此時刻的激光數(shù)據(jù)寫入雙口RAM 中; 當讀使能信號有效時,首先從雙口RAM 中的激光測距儀數(shù)據(jù)到FIFO 中,接著讀取相應(yīng)幀的圖像數(shù)據(jù)到FIFO 中; FIFO 半滿后,激光測距儀數(shù)據(jù)和相機數(shù)據(jù)一起送到外部的SDRAM中進行進一步緩存,仿真時序圖如圖2 ( b) 所示。由圖2 的仿真結(jié)果可知,本文同步設(shè)計方案能夠有效地減少2 個傳感器之間的延時,采集2 個傳感器的相對同步數(shù)據(jù)。 雖然不是嚴格意義上的同步,但已能滿足柔性基線測量系統(tǒng)的需求。

圖2 CCD 相機和激光測距儀同步采集設(shè)計及仿真時序圖

3) 數(shù)據(jù)緩存與整理

本系統(tǒng)中采用的緩存方案為首先把圖像數(shù)據(jù)、控制信號進行3 級鎖存,因為實驗相機輸出的圖像數(shù)據(jù)為2 個TAP 的數(shù)據(jù),分別把2 個TAP 的數(shù)據(jù)送入FPGA 內(nèi)部的2 個雙口RAM 中進行緩存,左邊TAP 的數(shù)據(jù)按照順序地址存儲,右邊TAP 的數(shù)據(jù)按照逆序地址存儲,從而將2 個TAP的數(shù)據(jù)拼接成完整的圖像。 當使能信號有效時,把2 個雙口RAM 的數(shù)據(jù)送入到FIFO 中進一步緩存,當FIFO 數(shù)據(jù)半滿后,把FIFO 的數(shù)據(jù)通過SDRAM 接口控制器送入到外部的SDRAM 存儲器中去。

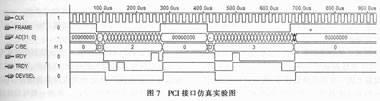

4) PCI 邏輯接口

本系統(tǒng)通過PCI 本地邏輯接口來完成FPGA與PLX9656 的通信。 系統(tǒng)加電啟動后,PLX9656的內(nèi)部寄存器由PCI 總線的RST#信號復(fù)位; 同時PLX9656 輸出局部復(fù)位信號LRESET,并檢查EEPROM 是否存在。 如果采用本地端DMA 方式控制,則整個握手過程如下: 首先當SDRAM 緩存中的數(shù)據(jù)達到設(shè)定值后,LINTI # 信號有效,PLX9656 向主機端發(fā)送中斷請求信號; 若CPU 響應(yīng)中斷,則在中斷相應(yīng)程序內(nèi)發(fā)出DMA 讀命令、要讀的字節(jié)數(shù)和地址信息等。 PLX9656 申請本地總線,使LHOLD 信號有效。 FPGA 驅(qū)動LHOLDA信號有效來響應(yīng)PLX9656 的請求,PLX9656 將PCI 地址空間映射到本地地址空間。 接著通過設(shè)置寄存器來啟動DMA 傳輸,PLX9656 有效ADS#( 地址選通信號) 、訪問地址出現(xiàn)在LA 地址總線上。 再次FPGA 有效READY # 信號,同時使能SDRAM 控制接口的讀使能有效信號,數(shù)據(jù)開始出現(xiàn)在LD 數(shù)據(jù)總線上。 當數(shù)據(jù)的最后一個字節(jié)開始傳輸時,PLX9656 驅(qū)動BLAST#信號有效,同時FPGA 無效READY #信號。 最后使SDRAM 的讀使能是信號無效,PLX9656 驅(qū)動LHOLD 無效,釋放本地總線,接著FPGA 也驅(qū)動LHOLDA 無效,結(jié)束一次數(shù)據(jù)的傳輸。 DMA 傳輸?shù)臅r序仿真圖如圖3 所示。

圖3 本地總線到PCI 總線的DMA 傳輸時序仿真圖

2. 4 高速緩存設(shè)計

由于PCI 接口芯片內(nèi)部緩存容量太小,所以在實時采集過程中必須采用高速緩存器將數(shù)據(jù)進行緩存,然后再通過PCI 總線送到主機,以提高系統(tǒng)的傳輸速度和性能。 大容量高速的SDRAM 容易買到且價格適中,本系統(tǒng)采用SDRAM 進行緩存。 Windows 是多線程、搶先任務(wù)的操作系統(tǒng),為了減少線程由于CPU 占用時間結(jié)束而中斷,中斷間隔應(yīng)大于線程的最大執(zhí)行時間20 ms,所以緩存的容量至少應(yīng)為: 20 ms × 70 MB / s × 2 = 2. 8MB. 本系統(tǒng)中采用Micron 的MT48LC32M16A2芯片,該芯片為512 MB 存儲大小,16 bit 位寬,133 MHz 的讀寫速度,能夠滿足系統(tǒng)數(shù)據(jù)采集和存儲帶寬的要求。本系統(tǒng)采用緩存方案為在FPGA 外接2 組32M* 32 位的SDRAM,由4 片SDRAM 配置而成,用于相機到PCI 的數(shù)據(jù)緩沖。 且SDRAM 通過控制器的封裝做成FIFO 的接口,相機的數(shù)據(jù)寫入FIFO,按照設(shè)定的圖像數(shù)量給PCI 發(fā)送中斷,然后由PCI 讀取相機數(shù)據(jù),從而克服了SDRAM結(jié)構(gòu)復(fù)雜,切換控制電路難操作的缺點。

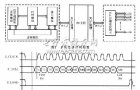

2. 5 實時存儲設(shè)計

實時流盤一直是高速數(shù)據(jù)采集技術(shù)的最大瓶頸,直接制約了采集存儲設(shè)備的實時存儲能力。 本系統(tǒng)中采用支持66 MHz、100 MHz、133 MHz /64 bit的PCI-X 總線的主板,由8 塊容量為1TB 的高速SATA 硬盤,通過3WARE 公司的RAID 卡配置成RAID0 方式,以獲得最大化的磁盤訪問速率,組成高速大容量的存儲設(shè)備,整個數(shù)字相機數(shù)據(jù)采集存儲設(shè)備的設(shè)計框圖如圖4 所示。

圖4 實時高速存儲方案設(shè)計

本系統(tǒng)把實時采集模塊輸出的數(shù)據(jù),利用接口芯片PLX9656,通過PCI 總線把數(shù)據(jù)送進系統(tǒng)內(nèi)存,然后在RAID 卡的控制下,將內(nèi)存中的數(shù)據(jù)通過PCI 總線寫入SATA 硬盤陣列中,理論持續(xù)寫盤速度可達400 MB / s 以上。

3 實驗及系統(tǒng)測試結(jié)果

雙天線干涉SAR 柔性基線測量系統(tǒng)的模擬實驗平臺由傳感器測量平臺、合作目標和運動平臺組成,如圖5( a) 和圖5( b) 所示。 本文設(shè)計實現(xiàn)的數(shù)據(jù)采集存儲系統(tǒng)實物如圖5( c) 所示。

圖5 柔性基線測量系統(tǒng)原理樣機

實驗中,對系統(tǒng)分別進行了功能測試和性能測試。 性能測試主要包括實時采集記錄速度測試、持續(xù)寫盤陣速度測試和穩(wěn)定性測試。對于系統(tǒng)的功能測試,分別進行模擬圖像和實際圖像數(shù)據(jù)采集測試。 模擬圖像為在FPGA 內(nèi)產(chǎn)生循環(huán)有規(guī)律的數(shù)據(jù),對應(yīng)的圖像為條紋圖像,根據(jù)采集的數(shù)據(jù)是否正確來驗證采集系統(tǒng)的功能; 然后切換到實際數(shù)據(jù)源,采集合作目標的運動圖像。 模擬和實測的圖像和數(shù)據(jù)文件分別如圖6所示。

圖6 數(shù)據(jù)采集系統(tǒng)采集的數(shù)據(jù)文件與圖像

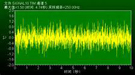

由圖6( a) 和圖6( b) 可知,對于模擬數(shù)據(jù)源,本文系統(tǒng)采集圖像為黑白相間的條紋,且圖像數(shù)據(jù)中像素的灰度值與設(shè)定值是一致的,不存在丟數(shù)問題。 由圖6( c) 和圖6( d) 可知,本文系統(tǒng)采集的合作目標的圖像和實際物體是一致的。 模擬和實測圖像數(shù)據(jù)的測試結(jié)果均表明,本文系統(tǒng)可以正確地進行數(shù)據(jù)采集和存儲,沒有圖像錯位現(xiàn)象,這驗證了系統(tǒng)功能的正確性。系統(tǒng)實時采集記錄速度的測試方法為: 由于本系統(tǒng)中傳感器的輸出頻率有限,無法反映系統(tǒng)的最大采集記錄速度。 采用在FPGA 內(nèi)部生成不同頻率的模擬圖像,通過本系統(tǒng)進行實時采集和寫盤,利用上位機軟件對圖像進行回放,查看有無丟幀和錯位現(xiàn)象。 實測結(jié)果表明,當輸出頻率超過50 Hz 時,如果只采集不存盤,圖像采集正確,但是選擇同時存盤時,開始出現(xiàn)圖像錯位和丟幀現(xiàn)象。 原因主要有2 個: 一個是當頻率大于50 Hz時,數(shù)據(jù)量大于100 MB / s,本系統(tǒng)外接的高速緩存,其讀寫速度理論值為133 MHz,因為做成FIFO 接口,是邊寫邊讀,造成傳輸速度減半,可能導(dǎo)致緩存數(shù)據(jù)沒有及時讀走,造成圖像錯位和丟失; 另一個是系統(tǒng)在主機內(nèi)存中讀和寫是一個線程,邊讀邊寫數(shù)據(jù)導(dǎo)致速率跟不上。 綜上所述,本系統(tǒng)的采集記錄速度可以達到100 MB / s,滿足系統(tǒng)70 MB / s 的指標要求。持續(xù)寫盤陣速度測試方法為采用專用的硬盤讀寫速度測試軟件,從主機內(nèi)存往磁盤陣列寫入不同容量數(shù)據(jù),對軟件統(tǒng)計的速度作平均。 實測結(jié)果表明,在不同的采集時間內(nèi),系統(tǒng)的實時存儲速度都能達到240 MB / s 以上,滿足系統(tǒng)指標120 MB / s的要求。 另外,系統(tǒng)采用8 塊1TB 的SATA 硬盤,總的記錄容量為8 TB,滿足系統(tǒng)最小記錄容量2 TB 的指標要求。對于系統(tǒng)的穩(wěn)定性測試的方法為: 在不同工作模式下,多次采集2 個傳感器數(shù)據(jù),通過校驗程序?qū)?shù)據(jù)包頭計數(shù)器進行校驗,統(tǒng)計數(shù)據(jù)的丟失幀數(shù)。 從而計算系統(tǒng)的丟幀率。 在系統(tǒng)要求的工作時間內(nèi),系統(tǒng)在不同模式下都沒有出現(xiàn)丟幀情況,性能非常穩(wěn)定,既使工作時間為要求的3 倍,本系統(tǒng)的丟幀率最高只有0. 03% ,能夠滿足基線測量系統(tǒng)的要求。

綜上所述,本系統(tǒng)的實測性能指標均高于基線測量系統(tǒng)的指標要求,能夠?qū)崟r地對基線測量系統(tǒng)輸出數(shù)據(jù)進行高速采集和實時存儲。 為了進一步提高系統(tǒng)的性能,可以通過采用性能更高的磁盤陣列控制卡和高速磁盤陣列,如速率更高的SAS 接口硬盤,增大外部高速緩存容量,把SDRAM 做成乒乓模式提高傳輸速率,對主機端控制程序進行對線程優(yōu)化等來實現(xiàn)提高采集記錄速度。

4 結(jié)論

基于FPGA + PCI 數(shù)據(jù)采集存儲硬件設(shè)計,采用了高性能FPGA 邏輯器件與多個磁盤陣列構(gòu)成的高速存儲系統(tǒng),實現(xiàn)了對柔性基線測量系統(tǒng)輸出的高速采集與實時存儲。 本文詳細介紹了該設(shè)計的工作原理和關(guān)鍵模塊設(shè)計,重點描述了利用FPGA 對CCD 相機和激光測距儀進行設(shè)置、同步采集與數(shù)據(jù)高速緩存,通過PCI 專門接口芯片,和PCI 總線進行高速實時傳輸?shù)牧鞒獭?實際系統(tǒng)測試結(jié)果表明,該系統(tǒng)通過PCI 總線傳輸速度達200 MB / s以上,持續(xù)寫盤陣速度達到240 MB / s,實時采集記錄速度達100 MB / s. 該系統(tǒng)具有實時性強、性能穩(wěn)定、設(shè)計靈活等特點。

電子發(fā)燒友App

電子發(fā)燒友App

評論