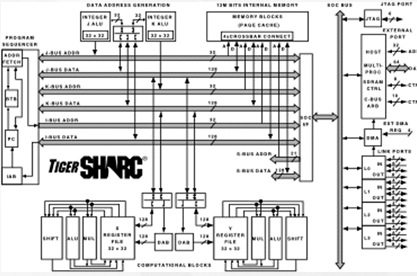

隨著科技的進步,對DSP 的處理速度以及相互之間的通信速度要求越來越高。ADI 的TS201 是目前業界性能最高的DSP 處理器之一,具有極強的數據處理能力和豐富的硬件資源, 其主頻可高達600MHz ,總體性能可以達到3GFLOPS 或者12GOPS ,外部數據通信速度就成為發揮其性能的瓶頸。為了配合發揮其強大的處理能力,TS201 專門為高速通信設計了基于LVDS 技術的LinkPort 口。LVDS 是一種小振幅差分信號技術,使用非常小的幅度信號(350mV) 通過一對差分PCB 走線來傳輸數據,在兩條平行的差分信號上流經的電流和電壓幅度相反,噪聲同時耦合到兩條線上,于是噪聲被抵消。LVDS差分信號技術降低了對噪聲的關注。TS201 使用LinkPort 進行高速通信,解決了TS201 之間的通信瓶頸問題,但無法和需要高速通信的實時系統之間實現連接。FPGA 具有接口靈活,硬件設計軟件化的功能,可以方便的實現各種數據接口和協議的對接。本文介紹了用FPGA 與DSP 的LinkPort 的對接原理和實際應用,在實時系統和TS201 之間搭起了一條高速通道。

1 LinkPort 介紹

TS201 上有4 個LinkPort 口,每個LinkPort 口有24 根線,包含收發兩個模塊,每個模塊中包含了5對差分數據線和兩個控制線,分別是LxDATO3 - 0P ,LxDATO3 - 0N , LxCLKOUTP , LxCLKOUTN , LxACKI ,LxBCMPO , LxDATI3 - 0P , LxDATI3 - 0N , LxCLKINP ,LxCLKINN , LxACKO , LxBCMPI。其中接收和發送數據的數據線以及時鐘線都是使用LVDS ,這樣有利于實現高速的數據傳輸,在應用中,DSP 之間的Link2 Port 傳輸數據可高達每對線500MHz。

LinkPort 通信協議:LinkPort 口發送和接收數據的邏輯是很直接的,但是通過采用LVDS 技術,可以運行在很高的速度上。TS201 處理器所使用的Link2 Port 協議的一個簡化說明如圖1 所示。

數據幀的開始是由LinkPort 時鐘的上升沿來指示的,在時鐘的上升沿和下降沿分別傳送數據,時鐘結束,則數據傳送也停止。所以LinkPort 口上的時鐘是不連續的。TS201 的LinkPort 發送數據是以128bit 為基本單位的,所以一次發送數據至少需要16 個時鐘周期來完成。

2 在FPGA 中實現LinkPort 口

Xilinx 的Virtex - II 系列的FPGA 是一款高性能,資源豐富的產品,它支持和TS201 DSP 之間的LinkPort 互聯。由于LinkPort 口具有收發兩個模塊,所以在FPGA 中要實現和LinkPort 口的對接,需要在其內部實現收發兩個模塊來分別和DSP 的LinkPort 口相對應。

2. 1 FPGA 中的時鐘以及DCM

要在FPGA 中實現LinkPort 口的收發功能,就必須要進行復雜的時序控制,Virtex 系列的FPGA 中提供了功能強大的DCM(數字時鐘管理器) 模塊,它可以實現延遲鎖相環,數字頻率合成器,數字移相器,數字擴頻。在LinkPort 的實現中,至少要用到兩個DCM,其中一個DCM 作為延遲鎖相環,另一個作為移相器。利用這兩個DCM 模塊,可以給LinkPort 的實現提供同頻率的,相位分別是0 度,90 度,180 度和270 度的時鐘供LinkPort 口實現的時候使用。

FPGA中實現LinkPort 涉及到多個時鐘: FPGA的外部輸入時鐘,FPGA 的LinkPort 口的發送時鐘,FPGA 的LinkPort 口的接收時鐘。對于這些不同的時鐘采取了不同的處理方法。FPGA 的外部輸入時鐘是由外部的時鐘輸入管腳經過FPGA 的全局時鐘緩沖IBUFG模塊送到DSP 內部的DCM 模塊供內部系統使用。FPGA 的LinkPort 口的接收時鐘直接使用Xilinx 所提供的差分接收模塊ibufds_lvds_25_dt 直接轉換成內部的單端時鐘信號使用。使用這個時鐘以及它的反向時鐘來鎖定LinkPort 口上的上升沿數據和下降沿數據。LinkPort 口的發送時鐘則是由Xilinx 的FDDRRSE 模塊來實現的。

2. 2 LinkPort 接收模塊的設計

接收模塊首先調用FPGA 內部的差分信號轉單端的模塊ibufds_lvds_25_dt ,把外部傳輸線上的LinkPort 口差分信號轉換成內部的處理信號。由于LinkPort 口在LinkPort 時鐘的上升沿和下降沿分別傳送4 位的數據, 同時一次LinkPort 傳送最少是

128bit 的數據,也就是一次LinkPort 傳送至少需要16個LinkPort 的時鐘周期。因此需要將接收的數據進行拼裝組合并保存。為了實現這個功能,利用雙端口RAM采用了兩級緩沖的機制,先用8 個16 位深度的1bit 小的數據緩沖模塊RAM16X1D 將數據從LinkPort 口接收下來,然后以8bit 為單位寫到FPGA內部內建的一個較大的非對稱雙口RAM 模RAM16_S9_S18 中。這個小的數據緩沖區利用一個狀態機控制它的地址變化,形成一個循環的數據緩沖區。使用以下語句實現了一個類似乒乓緩沖的小的數據緩沖區:

數據接收的時候,開始接收的數據超過8 個的時候,就開始從RAM16X1D 的這個小的數據緩沖區中讀取數據。當接收的數據收全之后,wr_addrp =“0000”,接收停止,而rd addr 此時處于高的緩沖區,這個時候程序會自動的讀取剩下的8 組數據,將其送到大的數據緩沖區RAM16_S9_S18 ,保證接收的數據全部正確地放到內部的RAM 中去,此時rdaddr 也為“0000”,接收模塊停止工作。

發送模塊的關鍵是如何控制時鐘和數據的發生以及保證他們之間的相位關系,使得在時鐘的上升沿和下降沿都可以進行數據傳輸,同時數據是穩定的。實現這個功能的關鍵是使用了FPGA 內部的帶有兩個相位相差180 度的獨立時鐘的雙數據速率的D 觸發器(FDDRRSE) 。保證數據的穩定性是靠前面所提到的DCM模塊所提供的不同相位的時鐘信號,LinkPort 模塊發送時鐘使用90 度和270 度相位的時鐘,要發送的數據使用的是0 度和180 度的時鐘。LinkPort 發送模塊的數據和相位之間90 度的相差可以保證LinkPort 的時鐘發送時的數據是穩定的。

FDDRRSE 模塊有一個復位輸入R ,一個置位輸入S ,一個時鐘使能輸入CE ,兩組數據和時鐘對D0與C0 和D1 與C1 ,一個數據輸出Q。復位輸入R ,當它為高的時候,重載所有的輸入,并在時鐘(C0 或者C1) 從低到高的過程中,將Q 的輸出置為低(復位的優先級比置位的優先級要高) 。當S 的輸入是高而R 的輸入是低的時候,觸發器被置位,在時鐘(C0 或者C1) 從低到高的時候輸出高電平。當R 和S 為低,CE 為高,C0 時鐘從低到高的時候D0 上的數據加載到D 觸發器中。當R 和S 為低,CE 為高,C1 時鐘從低到高的時候D1 上的數據加載到D 觸發器中。調用FDDRRSE 產生LinkPort 口的發送時鐘時,

R和S 為低, CE 為高,D0 為時鐘產生控制信號CLOCKOE ,D1 為低,C0 為90 度相位的時鐘txclk90 ,C1 為270 度相位的時鐘txclk90not 。正常工作的時候,在txclk90 的上升沿將D0 的clockoe 的信號輸出到lxclkout ,在txclk90not 的上升沿將D1 的低電平輸出到lxclkout 。這樣當clockoe 為低的時候, lxclkout就一直為低,需要傳輸數據的時候,將clockce 設置為高- 這樣就可以根據需要產生非連續的LinkPort時鐘。

當雙口RAM 中存在要發送的數據的時候,LinkPort 的發送模塊先從雙端口RAM 中取一個16位的數據,通過內部的時鐘控制和時序調整,將這個16 位的數據串行化成LinkPort 上傳輸的4 位一組的數據,這些數據分批以txclk ,txclk180 的時鐘發送到LinkPort 口,同時以txclk90 ,txclk90not 的時鐘產生相應的LinkPort 時鐘。在FPGA 的輸出到管腳之前,調用FPGA 內部的obufds_lvds_25 模塊將內部的單端信號轉換成差分信號。

3 工程應用及性能指標

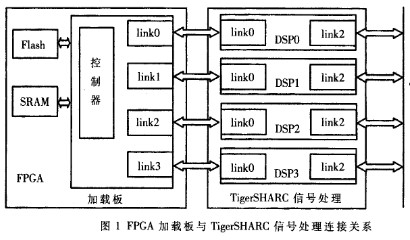

采用LinkPort 通訊的技術在DSP 處理板上已經得到了應用,該板的結構如圖2 所示。

在這個實時處理系統中,利用FPGA 提供的高速LinkPort 數據接口,實現了雷達測速系統和DSP處理器之間的無縫連接,很好地滿足了應用的要求。

要求該板上的FPGA 和DSP 之間的LinkPort 口上的時鐘能夠達到200MHz。板上的時鐘同時提供給TS201 芯片和FPGA ,使用一個DSP 的LinkPort 口和FPGA 進行測試,由于FPGA 內部的LinkPort 接收數據是以8 位為單位進行處理,發送數據是以16 位為一組進行處理的,把LinkPort 口的接收模塊稱為rx_8 模塊,發送模塊稱為tx_16 模塊。FPGA 內部的數據流程如圖3 所示。

經過實際驗證, 在LinkPort 口上的時鐘達到300MHz 及300MHz 以下的頻率時可以可靠收發數據。而LinkPort 口每個時鐘可以傳送1Byte 數據,也就是說FPGA 和TS201 之間的LinkPort 的通信速度已經達到雙向2. 4GbitPs。對于目前的應用來說已經足夠了。

FPGA 中的接收模塊和發送模塊是可以分別使用的,通過和FPGA 內部不同模塊進行組合以及時序控制就可以應用到實際系統中,在西部某雷達測速系統中已經將方案進行了實際應用,實際應用中FPGA 的內部框架及接口如圖4 所示。

4 結束語

本文介紹了TS201 的LinkPort 口的協議以及在Xilinx V2Pro20 FPGA 中實現該協議的原理, 并給出了該方案的具體指標和典型應用。因為FPGA 具有很強的靈活性,可以很方便地實現各種數據接口格式和協議的對接,根據實際系統的需要實現FPGA 與系統的對接,就可以利用FPGA 和DSP 之間的LinkPort 高速通道,實現DSP 和系統之間數據交換的無縫連接。

電子發燒友App

電子發燒友App

評論