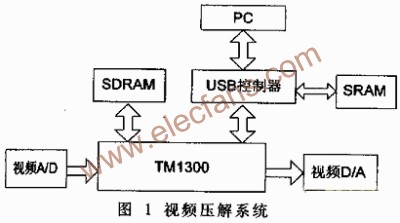

本文針對高速數據傳輸需求,根據USB2.0的協議規范,利用VHDL語言實現符合該協議的功能控制器,在視頻壓解系統中使數據在PC與外設之間高速傳輸。

2010-10-28 15:44:03 1170

1170

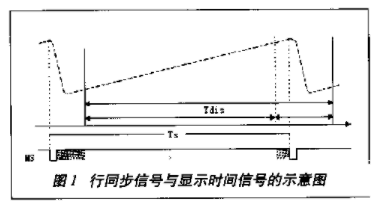

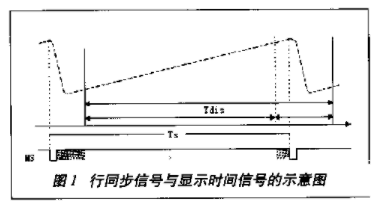

利用可編程器件CPLD/FPGA實現VGA彩色顯示控制器在工業現場中有許多實際應用。以硬件描述語言VHDL對可編程器件進行功能模塊設計、仿真綜合,可實現VGA顯示控制器顯示各種圖形、圖像、文字,并實現了動畫效果。

2020-08-30 12:03:59 882

882

FPGA 加三移位法,有人用vhdl 語言寫過嗎

2019-03-20 15:59:05

希望在今后的學習中大家多多幫助,先來幾個基礎的verilog 教材吧 現在我用到了FPGA關鍵分配的知識。 不過還是想系統的學習一下。那就先從軟件的使用和語法開始學習吧。 完整的pdf格式文檔電子發燒友下載地址(共31頁): FPGA中文VHDL語言教程.pdf

2018-07-04 01:11:32

設計RISC微處理器需要遵循哪些原則?基于FPGA技術用VHDL語言實現的8位RISC微處理器

2021-04-13 06:11:51

)設計交通燈控制電路 基于VHDL建模實現FSK的調制與解調 數字鎖相環法位同步信號 用VHDL實現搶答器設計 基于單片機和CPLD接收GPS信號的顯示系統 基于單片機和CPLD實現的GPS

2012-02-10 10:40:31

VHDL 主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL 在語言形式、描述風格和句法上與一般的計算機高級語言十分相似。VHDL 的程序結構特點是將一項

2018-09-07 09:04:45

VHDL與其他傳統集成電路描述語言相比具有什么優勢?VHDL語言為核心的EDA技術在醫學中的應用

2021-05-07 06:38:41

用VHDL語言編寫的基于FPGA的波形發生器,使用了QuartusII程序。可以在1602液晶顯示器上顯示目前的波形種類。產生的波形分別是正弦波,三角波,鋸齒波和方波。

2019-08-10 08:55:34

,非常詳細的講解了Quartus II的基本使用,從工程的建立、文本的輸入,系統的仿真,RTL視圖查看,管腳的分配,硬件的配置等。整個過程全部用VHDL語言講解,從VHDL語言庫的調用,實體的描述

2009-03-26 16:38:29

予幫助 ,說明白我想找個人代寫, 花錢是肯定的,但是請各位不要要價太高, 還是個負收入的人啊. 題目是:編寫全自動洗衣機控制電路的VHDL語言程序要求是:1.必須有VHDL硬件描述語言

2010-03-01 12:45:08

Vhdl語言嚴謹啊用狀態機設計一個能使數碼管顯示多樣字符的控制器:1、用狀態機控制3個數碼管,按“000-StA-1bC-2FG-3HL- End”的順序輪流顯示以上字符,各組字符顯示的時間間隔為

2016-10-26 10:21:40

請問使用VHDL語言設計FPGA有哪些常見問題?

2021-05-06 09:05:31

控制器。為了使微控制器的數據總線(8位)與SDRAM控制器的數據總線(32位)相匹配,利用VHDL語言實現8位到32位的雙向數據轉換,使整個數據獲取系統能可靠正常工作。 3. VHDL程序設計

2016-05-08 06:18:34

不知道有沒有大神做過:基于FPGA的圖像邊緣檢測系統設計,用VHDL語言實現

2018-05-10 00:22:07

,死區時間可預置,并具有閉環調節功能等特點。整個電路通過FPGA芯片實現,采用硬件描述語言(VHDL)與原理圖輸入相結合的方法,完成了整個功能模塊的設計,使得控制系統更加簡單可靠。對所設計的控制器進行了

2019-06-21 07:53:14

用vhdl語言做步進電機的控制器。應該如何入手呢?看了很多資料,各有各的思路,越看越混亂,要分成幾個模塊去做呢? 求大神帶!

2016-04-27 10:21:33

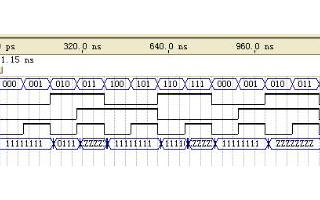

應用VHDL語言設計數字系統,大部分設計工作可在計算機上完成,從而縮短系統開發時間,提高工作效率。下面介紹基于VHDL設計交通燈控制器的一種方案,并給出源程序和仿真結果。

2019-10-18 07:21:51

成為描述、驗證和設計數字系統中最重要的標準語言之一。由于VHDL在語法和風格上類似于高級編程語言,可讀性好,描述能力強,設計方法靈活,可移植性強,因此它已成為廣大EDA工程師的首選。目前,使用VHDL

2019-06-18 07:45:03

的仿真,RTL視圖查看,管腳的分配,硬件的配置等。整個過程全部用VHDL語言講解,從VHDL語言庫的調用,實體的描述,結構體的描述,進程和函數的應用。一步一步的講解設計過程中的每個語句和注意事項,同時

2009-02-07 11:34:24

本文介紹應用美國ALTERA公司的MAX+PLUSⅡ平臺,使用VHDL硬件描述語言實現的十六路彩燈控制系統。

2021-04-19 07:43:57

各位大家好,我正在尋找用VHDL語言編寫的UDP / IP堆棧(我必須在Spartan-6 FPGA中實現它)。我正在尋找一個盡可能簡單的功能:使用VHDL語言編寫,而不是Verilog - 在

2019-08-06 02:37:22

通過對傳統MCS-51單片機指令時序和體系結構的分析,使用VHDL語言采用自頂向下的設計方法重新設計了一個高效的微控制器內核。

2021-04-13 06:10:59

本文介紹直流電機進行位置控制的方法,給出位置控制模塊的設計和實現,使用 VHDL語言進行編程完成了FPGA對直流電機的各種控制。

2021-05-10 06:19:17

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件

2019-08-28 08:05:46

本文介紹一種使用硬件描述語言VHDL來實現基于Petri網的并行控制器的方法。首先使用Petri網對問題進行建模,并對模型進行分析和控制,獲得控制器的Petri網模型;然后用VHDL對Petri網

2019-08-16 07:52:03

在語法和風格上類似于高級編程語言,可讀性好,描述能力強,設計方法靈活,可移植性強,因此它已成為廣大EDA工程師的首選。目前,使用VHDL語言進行CPLD/FPGA設計開發,Altera和Lattice

2019-08-08 07:08:00

親愛的朋友們,我聽說我們甚至可以通過FPGA實現微控制器。例如,我們可以用FPGA實現AVR micro。我的問題是:我們怎樣才能使用它?假設我們已經用C語言編寫了代碼,現在我們改變了主意,決定用

2019-03-22 07:32:06

本人小菜鳥,開始學FPGA的時候學的Verilog語言,后來因為課題組前期的工作都是VHDL就該學VHDL了。最近聽了幾個師兄的看法,說國內用VHDL的已經很少了,建議我還是堅持用Verilog,小菜現在好糾結,請問到底應該用哪種語言呢?望各位大神指點!

2015-07-08 10:07:56

本帖最后由 簡單明了 于 2013-5-20 15:14 編輯

求一篇程序,描述如下:基于FPGA的液晶顯示LCD的顯示,用VHDL語言,液晶顯示LCD的型號是TG12864E,內部控制器

2013-05-20 15:00:49

求全彩LED顯示屏控制器的FPGA設計的VHDL代碼,不勝感激!!!

2015-11-14 01:57:35

)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。HDL硬件描述語言(HDL)是一種用來設計數字邏輯系統和描述數字電路的語言,常用的主要有VHDL、Verilog HDL、System Verilog 和 System C。VHDL是一種用于電路設計的高級

2021-12-22 07:39:43

、FPGA)的發展和硬件描述語言(HDL, Hardware Description Language)的出現,軟、硬件設計之間的界限被打破,數字系統的硬件設計可以完全用軟件來實現,只要掌握了HDL語言就可以

2008-09-11 15:47:23

VHDL硬件描述語言教學:包括fpga講義,VHDL硬件描述語言基礎,VHDL語言的層次化設計的教學幻燈片

2006-03-27 23:46:49 93

93

VHDL的定義和功能VHDL的發展概況程序編程語言和硬件描述語言的對比引入硬件描述語言對系統進

2008-09-03 12:58:41 39

39

全面地介紹了VHDL硬件描述語言的基本知識和利用VHDL進行數字電路系統設計的方法。全書共分13章:第1-6

2008-09-11 15:45:27 1333

1333 [學習要求] 掌握VHDL硬件描述語言的基本語法和源文件的結構,學會用VHDL硬件描述語言設計典型數字邏輯電路。[重點與難點]重點:VHDL語言的程序結構;VHDL語言的數據類型及數

2009-03-18 20:02:35 47

47 VHDL語言概述:本章主要內容:硬件描述語言(HDL)VHDL語言的特點VHDL語言的開發流程

1.1 1.1 硬件描述語言( 硬件描述語言(HDL HDL)H

2009-08-09 23:13:20 47

47 VHDL語言描述數字系統:本章介紹用 VHDL 描述硬件電路的一些基本手段和基本方法。 VHDL 語言是美國國防部在 20 世紀 80 年代初為實現其高速集成電路計劃(VHSIC)而提出的

2009-09-01 09:02:40 37

37 通過模糊自整定PID 控制器的設計,本文提出了一種基于VHDL 描述、DSP Builder 和Modelsim 混合仿真、FPGA實現的智能控制器設計及測試新方法。首先,通過MATLAB 仿真,得出智能控制器的結

2009-09-04 09:34:11 17

17 VHDL硬件描述語言與數字邏輯電路設計:本書系統地介紹了一種硬件描述語言,即VHDL語言設計數字邏輯電路和數字系統的新方法。這是電子電路設計方法上一次革命性的變化,也是邁

2010-02-06 16:55:22 359

359 闡述密碼控制設計的基本原理。介紹了VHDL語言的特點以及基本的語法結構。在MAX+plusⅡ開發軟件環境下,利用VHDL硬件描述語言實現密碼控制系統設計,并對其系統各個模塊進行仿真

2010-12-16 16:10:37 0

0 介紹基于VHDL的微型打印機控制器的設計。論述了微型打印機的基本原理,以及實現控制器的VHDL語言設計。打印機的數據來自系統中的存儲模塊,根據需要控制打印。該微型打印機控

2010-12-23 16:44:19 60

60 實驗六、VHDL的基本描述語句設計一? 實驗目的1掌握VHDL語言的基本結構及設計的輸入方法。2掌握VHDL語言的基本描述語句的使用方法。二? 實驗設備

2009-03-13 19:23:57 1998

1998 【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優越性。

2009-05-10 19:47:30 1111

1111

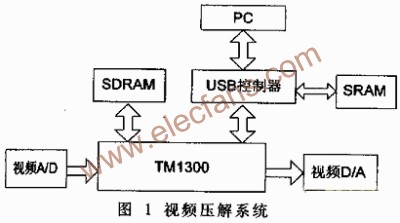

摘要:介紹了一種用VHDL設計USB2.0功能控制器的方法,詳術了其原理和設計思想,并在FPGA上予以實現。

關鍵詞:USB VHDL FPGA

在視

2009-06-20 13:26:46 1474

1474

基于VHDL語言的智能撥號報警器的設計

介紹了以EDA技術作為開發手段的智能撥號報警系統的實現。本系統基于VHDL語言,采用FPGA作為控制核心,實現了遠程防盜報警。該

2009-10-12 19:08:43 1167

1167

采用CPLD/FPGA的VHDL語言電路優化原理設計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起

2010-03-19 11:38:02 2318

2318

本設計是一種基于FPGA(現場可編程門陣列)的液晶顯示控制器。與集成電路控制器相比,FPGA更加靈活,可以針對小同的液晶顯示模塊更改時序信號和顯示數據。FPGA的集成度、復雜度和

2010-07-02 11:14:05 1247

1247

介紹一種基于FPGA(Field Programmable Gate Array)現場可編程門陣列的可鍵盤控制的計數,顯示電路的實現方法。應用VHDL語言(高速集成電路硬件描述語言)完成了34矩陣開關的掃描電路,可

2011-05-03 18:02:14 97

97 本文介紹了用硬件描述語言 VHDL 設計顯示屏控制電路的方法,此方法設計的控制電路達到了簡化系統總體結構、擴大應用范圍,并易于編制控制程序的目的。

2011-07-13 17:50:44 161

161 本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術,并使用VHDL語言設計實現DRAM控制器。

2012-02-02 11:29:58 1185

1185

VHDL(Very High Speed Integrated CIRCUITHARDWARE DESCRIPTION Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起來的。

2012-03-02 09:16:05 3822

3822

介紹了一種基于FPGA的多軸控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外圍電路組成,用于同時控制多路電機的運動。利用Verilog HDL 硬件描述語言在FPGA中實現了電機控制邏

2013-04-27 16:23:11 82

82 硬件描述語言VHDL簡介,好東西,喜歡的朋友可以下載來學習。

2016-02-19 17:19:50 0

0 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:FM收音機的解碼及控制器VHDL語言實現

2016-06-07 14:13:43 11

11 Xilinx FPGA工程例子源碼:USB接口控制器參考設計VHDL代碼(Xilinx)

2016-06-07 14:54:57 21

21 Xilinx FPGA工程例子源碼:基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程序

2016-06-07 15:07:45 12

12 VHDL語言編程學習之VHDL硬件描述語言

2016-09-01 15:27:27 0

0 VHDL語言編程學習Verilog硬件描述語言

2016-09-01 15:27:27 0

0 硬件描述語言VHDL的學習文檔,詳細的介紹了VHDL

2016-09-02 17:00:53 12

12 VHDL硬件描述語言與數字邏輯電路設計,感興趣的小伙伴們可以瞧一瞧。

2016-11-10 14:20:34 0

0 基于VHDL的SDRAM控制器的實現

2017-01-22 13:43:27 12

12 在小規模數字集成電路就要淘汰的今天,作為一個電類專業的畢業生應該熟悉VHDL語言和CPLD、FPGA器件的設計,閻石教授新編寫的教材也加入了VHDL語言方面的內容,可見使用VHDL語言將數字系統集成

2017-12-05 09:00:31 20

20 本文主要介紹了vhdl按鍵控制數碼管顯示。利用VHDL來實現程序控制有這些優點:VHDL支持自頂至下的和基于庫的設計方法,而且支持同步電路、異步電路、現場可編程門陣列器件FPGA以及其他隨機

2018-01-16 16:55:36 17309

17309 1987年, VHDL被正式確定為IEEE 1076標準。 VHDL是一種強類型語言, 具有豐富的表達能力, 可使各種復雜度(系統級、 電路板級、 芯片級、 門級)的電路網絡在同一抽象程度上被描述

2018-03-30 11:20:15 9

9 VHDL語言是一種在EDA設計中廣泛流行的硬件描述語言,主要用于描述數字系統的結構、行為、功能和接口。除了含有許多具有硬件特征的語句外,VHDL語言的句法、語言形式和描述風格十分類似于一般的計算機高級語言,是目前硬件描述語言中應用最為廣泛的一種。

2018-03-30 16:04:27 21

21 本文檔的主要內容詳細介紹的是VHDL硬件描述語言入門教程資料免費下載包括了:1. VHDL語言基礎,2. VHDL基本結構,3. VHDL語句,4. 狀態機在VHDL中的實現,5. 常用電路VHDL程序,6. VHDL仿真,7. VHDL綜合

2019-04-08 08:00:00 41

41 基于FPGA設計 LCD顯示控制器 ,關鍵在于采用硬件描述語言設計有限狀態機(FSM)來控制LCD模塊的跳轉,文獻中就是使用FSM實現了對LCD模塊的顯示控制,但是它們都是針對一種類型LCD模塊的某種顯示模式,不具有多模式的顯示控制能力。

2020-04-02 09:13:50 1026

1026 VHDL是一種用來描述數字邏輯系統的“編程語言”。它通過對硬件行為的直接描述來實現對硬件的物理實現,代表了當今硬件設計的發展方向。VHDL是為了滿足邏輯設計過程中的各種需求而設計的。

2020-04-23 15:51:03 2362

2362

什么是vhdl語言 VHDL 的英文全名是VHSIC Hardware Description Language(VHSIC硬件描述語言)。VHSIC是Very High Speed

2020-04-23 15:58:49 10242

10242 利用 VHDL 硬件描述語言在 FPGA 中設計直流伺服電機控制器。其含 4 路 PWM 控制器,每個控制器均分配一個 ID,當地址線 Address 選中某個 ID 時,表明對該 PWM 控制器

2020-05-11 08:00:00 13

13 本文檔的主要內容詳細介紹的是使用VHDL描述一個讓6個數碼管同時顯示出來的控制器資料免費下載。

2020-08-26 18:28:41 18

18 VHDL語言由于其其強大的行為描述能力及與硬件行為無關的特性,被廣泛的用于數字系統設計,實現了硬件電路設計的軟件化,成為實現Petri網邏輯控制器的有力的工具。用VHDL語言進行數字電路設計的很大

2020-09-22 20:46:51 691

691

提高了控制器的控制效果、運算速度和可靠性。使用該方法, 設計者不必十分了解 FPGA (可編程邏輯門陣列) 和VHDL (硬件描述語言) , 在Matlab中便可設計出需要的伺服控制器。

2020-11-30 14:02:00 2192

2192

本文檔的主要內容詳細介紹的是硬件描述語言VHDL及其應用的詳細說明。

2021-01-21 16:02:11 21

21 本文檔的主要內容詳細介紹的是VHDL硬件描述語言的學習課件免費下載包括了:VHDL概述,VHDL數據類型與數據對象,VHDL命令語句

2021-01-22 08:00:00 5

5 VHDL與Verilog硬件描述語言在數字電路的設計中使用的非常普遍,無論是哪種語言,仿真都是必不可少的。而且隨著設計復雜度的提高,仿真工具的重要性就越來越凸顯出來。在一些

2021-08-04 14:16:44 3307

3307 vhdl描述半加器

2023-02-24 11:08:31 0

0 Petri網是離散事件系統建模的重要工具,本文使用硬件描述語言VHDL實現了基于Petri網的并行控制器。文中通過一個液位控制系統實例具體介紹了這一方法,并通過仿真波形證明了該方法的正確性。這對于離散事件系統并行控制器的設計具有十分重要的意義。

2023-08-03 15:33:38 299

299

FPGA芯片主要使用的編程語言包括Verilog HDL和VHDL。這兩種語言都是硬件描述語言,用于描述數字系統的結構和行為。

2024-03-14 16:07:38 85

85 fpga用的是什么編程語言 FPGA(現場可編程邏輯門陣列)主要使用的編程語言是硬件描述語言(HDL)。在眾多的HDL中,Verilog HDL和VHDL是最常用的兩種。 Verilog HDL

2024-03-14 17:09:32 223

223 FPGA(現場可編程門陣列)的編程主要使用硬件描述語言(HDL),其中最常用的是Verilog HDL和VHDL。

2024-03-14 18:17:17 549

549 FPGA(現場可編程門陣列)的編程涉及到三種主要的硬件描述語言(HDL):VHDL(VHSIC Hardware Description Language)、Verilog以及SystemVerilog。這些語言在FPGA設計和開發過程中扮演著至關重要的角色。

2024-03-15 14:36:01 89

89 FPGA(現場可編程門陣列)的通用語言主要是指用于描述FPGA內部邏輯結構和行為的硬件描述語言。目前,Verilog HDL和VHDL是兩種最為廣泛使用的FPGA編程語言。

2024-03-15 14:36:34 87

87 功能,從而實現對數字電路的高效定制。FPGA語言主要包括VHDL(VHSIC Hardware Description Language)和Verilog等,這些語言具有強大的描述能力,能夠精確地定義硬件的每一個細節,從而實現復雜的數字系統設計。

2024-03-15 14:50:26 166

166

正在加载...

電子發燒友App

電子發燒友App

評論