Xilinx公司出品的Spartan6系列FPGA所具有的MultiBoot特性,允許用戶在不掉電重啟的情況下,根據(jù)不同時刻的需求,有選擇地從存儲于Flash中的多個配置文件中加載其中的一個,對FPCA在系統(tǒng)重配置,實現(xiàn)不同的功能。MultiBoot特性使得用戶可以在某些場合選擇較少邏輯資源的Xilinx FPGA,實現(xiàn)需要較大邏輯資源且較昂貴的FPGA或ASIC才能實現(xiàn)的功能,從而提高器件利用率及系統(tǒng)安全性、降低系統(tǒng)成本。

1 基本概念

Spartan-6 FPGA在上電時從片外Flash加載mcs文件進行配置。根據(jù)所包含的bit流文件的個數(shù),mcs文件分為兩類:一類是南單bit流文件生成的mcs文件,即該mcs文件中只包含一個bit流文件,用此類mcs文件配置FPGA時,只能實現(xiàn)一種功能;另一類是由多個bit流文件生成的mcs文件,即該mcs文件包含多個bit流文件。用此類mcs文件配置FPGA時,可根據(jù)需求有選擇地加載其中的某個bit流文件對FPGA進行系統(tǒng)重配置,即MultiBoot特性。

Spartan-6 FPGA擁有專用的MultiBoot邏輯配置模塊,來實現(xiàn)MultiBoot和Fallback操作。MultiBoot操作是在各配置bit流文件能正常加載的前提下,通過ICAP設(shè)置配置模塊中的相關(guān)寄存器并觸發(fā)IPROG命令,實現(xiàn)在不同配置bit流文件中的切換,達(dá)到FPGA實現(xiàn)不同功能的目的。Fallback操作是在從配置A切換到配置B的過程中出錯時,用另一個比較“安全”的bit流文件代替配置文件B配置FPGA的操作。這個比較“安全”的bit流文件稱為Golden。

FPGA的重配置操作,是通過專用的ICAP_SPARTAN6原語向配置模塊發(fā)送IPROG命令來實現(xiàn)的。重配置操作可由FPGA外部的處理器、微控制器、計算機和按鍵等“智能”終端觸發(fā)。在應(yīng)用設(shè)計中,只需在每個應(yīng)用程序中例化一個ICAP_SPARTAN6原語來實現(xiàn)相關(guān)命令序列即可實現(xiàn)MultiBoot特性。

Spartan6的多bit流配置可通過SPIx1,x2,x4及BPI模式實現(xiàn),文中只介紹基于SPI模式的MultiBoot特性的實現(xiàn),用配置文件代替應(yīng)用程序。

2 MultiBoot操作相關(guān)寄存器簡介

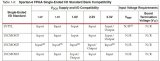

(1)所有Spartan-6 FPGA的bit流控制命令都是通過讀寫相關(guān)配置寄存器實現(xiàn)的。配置數(shù)據(jù)都是16位寬的字,也有一些數(shù)據(jù)是多字的,配置數(shù)據(jù)包含的3個主要命令如表1所示。

(2)所有的操作數(shù)據(jù)可分為兩種:

TYPE1包含兩部分:Header,Data。

TYPE2包含3部分:Header,Word Count,Data。

用TPYE1就能實現(xiàn)MultiBoot和Fallback操作,故只介紹TYPE1。TYPE1的Header是個16位字,用其中6位表示相關(guān)寄存器的地址,如表2所示。

其中Operation位[12:11]是表1中所列的操作碼,寄存器地址[10:5]如表4所示,字節(jié)數(shù)[4:0]表示操作所需的字節(jié)數(shù)。

TYPE1的數(shù)據(jù)部分形式如表3所示。

(3)Spartan-6 FPGA的MultiBoot常用配置寄存器及功能列表如表4所示。

寄存器功能介紹:

1)命令寄存器CMD。命令寄存器CMD存儲配置控制命令,以產(chǎn)生全局信號執(zhí)行其配置功能。在MultiBoot操作中,常用的CMD命令如表5所示。

2)General寄存器。觸發(fā)IPROG命令后,General1、General2中存放用于對FPGA進行重配置的下一個bit流文件的地址,其中General1存放地址的低16位,General2的高8位存放SPI操作碼,低8位存放地址的高8位。General3、General4存放FMlback時的配置文件地址,其中Gener al3存放低16位地址,General4的高8位存放SPI操作碼,低8位存放地址的高8位。General5中存放MultiBoot或Fallback時的用戶自定義數(shù)據(jù)。

3)模式寄存器MODE_REG。MODE_REG模式寄存器主要用于重配置時的一些模式設(shè)置,如SPI總線的位寬。模式寄存器中各位的功能如表6所示。MultiBoot和Fallback操作需對[13:8]進行相應(yīng)設(shè)置。

4)控制寄存器CTL、配置選項寄存器COR2。因CRC校驗錯誤也可能觸發(fā)Fallback操作,因此為安全起見,如果可能發(fā)生CRC校驗錯誤,需將CTL寄存器的CRC_EXTSTAT位清零,使能CRC校驗,并將COR2寄存器的RESET_ON_ERROR置1,使能CRC錯誤時的Fallback操作。但如果能確定不發(fā)生CRC錯誤,可不設(shè)置這兩位。

3 MultiBoot原理

如上所述,Spartan-6 FPGA內(nèi)置有專用的MultiBoot邏輯控制模塊,來實現(xiàn)MultiBoot(IPROG)和Fallback操作。當(dāng)觸發(fā)Fallback或IPROG時,片內(nèi)會產(chǎn)生一個復(fù)位脈沖,使片內(nèi)配置邏輯復(fù)位,但不會使專用的MultiBoot邏輯和BOOTSTS、MODE、G1-G5復(fù)位。

實現(xiàn)MultiBoot特性時,存儲器中的配置文件組織模式如圖1所示。

如圖1所示,第一部分是Header,這個小的bit文件中包含同步字、下一個配置文件的地址以及IPROG命令。此段必須位于Flash存儲器中的0地址處。該部分可由命令文件生成。第二部分是MultiBootBitstream,由用戶的多個bit流配置文件組成,其地址可在生成mcs文件時指定到符合Flash操作要求的任何地方。進行MultiBoot操作時只需通過ICAP向MuhiBoot邏輯控制模塊發(fā)送IPROG命令,之后控制模塊就會根據(jù)Gene ral1、General2指定的地址,加載下一個需要的配置文件。第三部分是Fallback或Golden配置文件,地址可由General3、General4指定。

Header、MultiBoot配置文件、Fallback配置文件在加載過程中,如果出錯,F(xiàn)PGA會根據(jù)相應(yīng)寄存器的值,從配置文件的起始地址重新加載3次,加載次數(shù)的計數(shù)保存在BOOTSTS寄存器的[15:12]位,名稱為strike。

Header在加載過程中分配有3個strike計數(shù)值:6、7、8。當(dāng)檢測到CRC錯誤,且RESET_ON_ERROR為1、strike《9,則strike計數(shù)器加1,并重新開始配置過程。若看門狗計時器超時也會觸發(fā)相同操作,但此時會忽略RESE_ON_ERROR的狀態(tài)。若strike等于9,則停止配置,且將INIT和DONE引腳拉低。

MultiBoot配置文件在加載過程也分配有3個strike計數(shù)值:0、1、2。當(dāng)在加載過程檢測到錯誤時,如果strike《3且RESET_ON_ERROR為1,則strike計數(shù)器加1,且從General1、General2指定的地址處重新加載配置文件。若strike計數(shù)器等于3,則觸發(fā)Fallback操作。

Fallback或Golden配置文件在加載過程也分配有3個計數(shù)值:3、4、5。當(dāng)在加載工程中檢測到錯誤時,若strike計數(shù)器值《6,則strike計數(shù)器加1,并從General3和General4指定的配置文件地址處重新加載配置文件。若strike計數(shù)器為6,則從0地址處加載Header配置文件。此時,F(xiàn)PGA會執(zhí)行循環(huán)加載過程:Header→MultiBoot→Fallback(或Golden)→Header,每次循環(huán)都會使strike計數(shù)器加1,最多3次。若其間某

個配置文件加載成功,則停止循環(huán),否則直到strike計數(shù)為9,停止加載過程。Strike計數(shù)器只能通過復(fù)位或重啟系統(tǒng)清零。

Fallback是一種出于安全性考慮的操作。一旦該操作被觸發(fā)且加載Golden成功,若再想退出Golden加載其他用戶配置文件,只能復(fù)位FP GA或重啟系統(tǒng)。

4 MultiBoot實現(xiàn)簡例

實現(xiàn)MultiBoot操縱有兩種方法:(1)基于ICAP的寄存器編程實現(xiàn)。(2)通過在生成bit流文件時,設(shè)置相關(guān)選項實現(xiàn)。

4.1 基于ICAP的寄存器編程實現(xiàn)

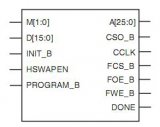

如上所述,通過ICAP_SPARTAN6原語發(fā)送IPROG命令,其發(fā)送命令序列如下:(1)發(fā)送同步字。(2)配置General1-General4,指定相關(guān)操作所需配置文件地址及操作碼。(3)發(fā)送IPROG命令。ICAP_SPARTAN6原語接口定義如表7所示。

在主SPI模式下,ICAP_SPARTAN6的輸入數(shù)據(jù)在從總線I[15:0]輸入前,要進行字節(jié)范圍內(nèi)的位交換,即16位寬的字分為高8位1 Byte,低8位1 Byte,各字節(jié)的最高位[7]和最低位[0]交換,位[6]與位[1]交換,其他以此類推。

通過ICAP觸發(fā)IPROG的命令序列舉例如表8所示。

IPROG命令后需經(jīng)過一段時間后,F(xiàn)PGA內(nèi)部才會產(chǎn)生相應(yīng)的重配置信號,因此在IPROG命令后需跟幾個空操作命令,一般為4個。GENERA L2、GENERAL4中的操作碼:0x0B、0x3B、0x6B分別為SPIx1、SPIx2、SPIx4。

ICAP邏輯模塊是FPGA中的專有邏輯模塊,因此在生成bit文件的各源文件中必須都實例化一個ICAP模塊。一般情況下對ICAP模塊的控制操作通過狀態(tài)機實現(xiàn)。

4.2 選項設(shè)置實現(xiàn)

實現(xiàn)MultiBoot功能所需配置的所有寄存器,均可在生成bit文件時通過添加相關(guān)的生成設(shè)置選項實現(xiàn)。在進程菜單中單擊Generate Pro gramming File,選擇Process Properties,彈出配置窗口如圖2所示。

5 結(jié)束語

介紹了實現(xiàn)MultiBoot操作的兩種方式,一種是基于ICAP的寄存器編碼配置方式。可通過源代碼中的注釋,使后續(xù)開發(fā)維護人員閱讀代碼、擴展功能時思路清晰,缺點是需編寫大量代碼,并需對ICAP的操作與命令序列有一定了解。第二種通過在生成bit文時添加相關(guān)設(shè)置選項實現(xiàn),方便簡單,但需大量的文本注釋,以便后續(xù)的開發(fā)與維護。當(dāng)然,實際的應(yīng)用開發(fā)過程中可同時使用這兩種方法,實現(xiàn)更高效便捷的編碼開發(fā)。

電子發(fā)燒友App

電子發(fā)燒友App

評論