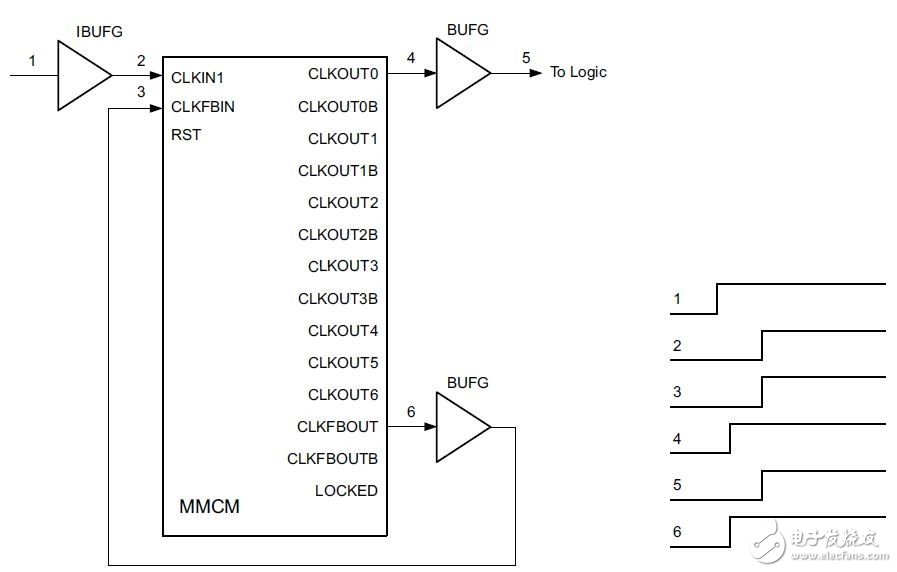

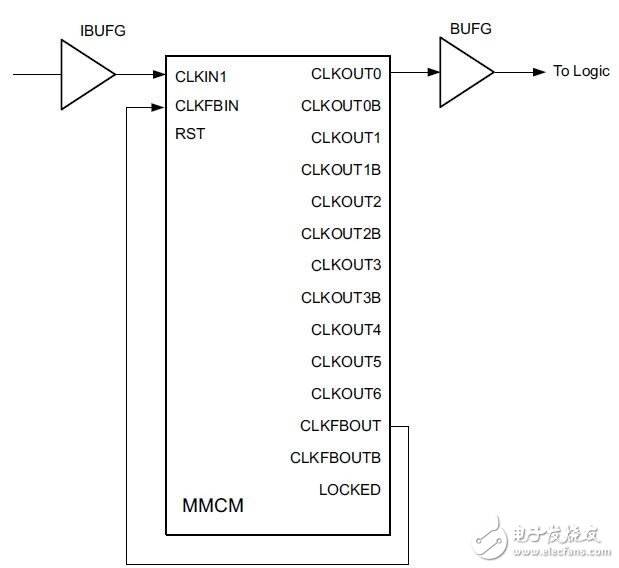

DCM一般和BUFG配合使用,要加上BUFG,應該是為了增強時鐘的驅動能力。DCM的一般使用方法是,將其輸出clk_1x接在BUFG的輸入引腳上,BUFG的輸出引腳反饋回來接在DCM的反饋時鐘

2018-05-11 03:53:00 1566

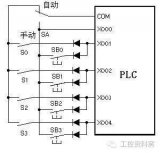

1566 一般認為輸入點數(shù)是按系統(tǒng)輸入信號的數(shù)量來確定的。但在實際應用中,通過以下措施可達到節(jié)省PLC輸入點數(shù)的目的,下面以FX1N系列PLC來介紹。

2023-06-01 09:49:31 610

610

大家好,對于BUFG-BUFG級聯(lián)對錯誤,我有[Place 30-120]次優(yōu)放置。我知道錯誤的發(fā)生是因為BUFG無法級聯(lián)...請參閱下面的“有問題”邏輯。如您所見,時鐘多路復用器的輸出連接

2018-10-29 14:20:35

BUFG BUFG BUFGP BUFGDS 等含義以及使用目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發(fā)沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序

2014-11-24 17:58:10

嗨,當在Planahead 10.1中運行DRC檢查時,我收到此錯誤:位于DCM_ADV_X0Y5的DCM clock_divider_i連接到位于BUFGCTRL_X0Y25的BUFG

2020-06-02 13:49:29

嗨,我們很有興趣使用具有PLL和MMCM的高頻(高達1066 MHz)的Virtex 7(-3速度等級)。BUFG和MMCM靜態(tài)精細相移是否在此頻率下正常工作?我可以使用包括PLL,具有靜態(tài)精細相移

2020-07-14 16:05:47

嗨,對于BUFG,是否有關于Max Fan的經(jīng)驗法則或建議?如果我還沒有找到它。我的問題是每個人都告訴我一個主時鐘的BUFG,一個V7的完整設計是可以的。然而,我在Timing Violation

2019-03-20 12:28:13

四、時鐘資源介紹4.1 BUFG BUFG在“Device”中如圖2-1-1所示,其中它有多種模式可根據(jù)需求來選擇使用,可以實現(xiàn)將時鐘傳遞到FPGA中的各種資源,具體架構在上文已做闡述,本文

2022-01-06 08:21:32

要提升輸出功率有效的方法就是電池升壓后再給功放供電。由于升壓轉換效率的存在又影響電池的續(xù)航時間。有效提升機器續(xù)航時間辦法有:1.用同步升壓,同步升壓可以規(guī)避非同步升壓整流二極管固有壓降大而損耗大的相對

2020-10-27 06:46:06

關電源的PCB布線不是很精通,這個辦法很有效。 2.輸入電容采用電解電容和瓷片電容配合來,如果方便的話就再并聯(lián)幾個0.01uf的貼片電容,如果有鉭電容就更好了,但是大家一定要注意:所有電容的耐壓值電壓輸入電壓

2016-01-18 14:30:43

本帖最后由 island008 于 2014-2-18 00:02 編輯

手機流量使用問題一直都被用戶們所關注,怎么才能節(jié)省流量呢?下面小編就分享一些節(jié)省流量的辦法,分析出具體步驟,讓大家節(jié)省

2014-02-18 00:00:41

芯片上正確的GTX站點。我已成功構建并測試了4 GTX版本的頻道。我可以使用這種方法成功構建一個8通道版本,但由于BUFG耗盡,我不能再使用GTX了(我還需要兩個以上共10個)。有8個GTX通道(除了我

2020-06-17 07:46:51

正確的方法是使用3個BUFGMUX組件,然后是BUFGCE,但這有問題:1)即使我有V2000 Virtex7 FPGA,由于放置限制,我最多只能使用32個BUFG。2)假設我可以放棄并減少時鐘區(qū)域

2020-06-19 12:53:16

嗨,我使用virtex7 xc7vx690t來運行P& R但總是得到unrouted網(wǎng)絡的錯誤。但我發(fā)現(xiàn)報道的錯誤是“BUFG驅動SLICE”。我認為BUFG是全球時鐘資源,它可以驅動

2018-11-13 14:16:20

在syn中設定了bufg為32個,syn后的報告中也是32個bufg。但是執(zhí)行impl后,vivado報錯說是生成了35個bufg,超出芯片容量。重新syn之后還是這樣。不知道是什么原因,怎么syn和impl的結果會不同。

2015-03-09 17:00:15

你好團隊xilinx,我正在使用zed板,需要通過tcp鏈接通過以太網(wǎng)接口接收5MB的大文件。我能夠以大小為1446字節(jié)的數(shù)據(jù)包接收它。有沒有辦法立刻收到完整的有效載荷?等待回復。提前致謝。問候,Akash.O

2020-04-29 09:58:21

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專用時鐘布線資源。對于SerDes應用,我們使用BUFIO2來獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

為什么BUFG驅動DSP48E1的CE會出現(xiàn)問題?警告:LIT:683 - DSP48E1符號“Inst_control_loop / u_Subsystem11

2020-06-12 11:45:43

什么是功耗?計技巧為什么能夠節(jié)省功耗?

2021-04-08 06:49:56

你知道在空閑任務中使用一行代碼可以節(jié)省多少能量嗎?FreeRTOS商業(yè)版本OpenRTOS及安全版本SAFERTOS的提供商WHIS創(chuàng)建了一個基本應用程序,在RTOS的idle hook中添加了一條

2022-06-24 15:38:36

本文介紹使開發(fā)物聯(lián)網(wǎng)解決方案更加有效的方法的6個方法。

2021-05-20 06:10:27

我正在嘗試在結構中使用GTE時鐘。根據(jù)架構指南,這就是BUFG_GT的用途。但是對于Vivado 2014.1,當我這樣做時:電線wClk156; IBUFDS_GTE3 mIBufDS(.I

2020-07-20 14:42:32

嗨我使用vivado 2015.4,我收到了這條消息:[放置30-150] MMCM-BUFG組件對的次優(yōu)放置。如果此子設計可接受此子優(yōu)化條件,則可以使用.xdc文件中

2020-04-24 07:44:55

1、聊一聊 一首含蓄而又簡單的歌曲,細細評味或許會在不經(jīng)意間想起曾經(jīng)的那么ta!2、正文部分1 現(xiàn)象對于MCU省內存,bug菌應該說得夠多了,今天這篇文章主要是對使用const省內存辦法中一個小細節(jié)

2022-01-25 07:08:04

大前提:C語言基礎扎實且熟悉單片機編程(或者會自己查資料解決基礎問題)小前提:該功能較為復雜不封裝函數(shù)難以促成簡潔的代碼第一步:尋找自己要實現(xiàn)的功能的所有子功能的介紹及實現(xiàn)辦法舉個例子:當我們目標

2021-11-22 07:22:55

我在vivado 2016.3中看到了以下地方的錯誤錯誤:[放置30-675]支持全局時鐘的IO引腳和BUFG對的次優(yōu)放置。如果此子設計可接受此子優(yōu)化條件,則可以使用.xdc文件中

2018-11-09 11:37:33

嗨,大家好,我正在使用Vivado 2014.對于設計,是使用BUFG或IBUF / OBUF原語到端口引腳還是工具將在分配PIN時自動獲取緩沖區(qū)?我沒有為時鐘引腳A2YCLK0分配BUFG。在我

2019-04-03 13:28:08

實際應用經(jīng)常只會用到數(shù)據(jù)轉換器模擬信號范圍的一部分。如果在應用中只用到該范圍的一半或者四分之一,則可以很容易地計算出有效分辨率。但如果遇到的是一個更復雜的分數(shù),又該怎么辦呢?本文將介紹在使用任何模擬信號范圍時有效分辨率的計算。

2019-07-17 06:59:27

)然后傳遞到BUFG。 BUFG的輸出驅動邏輯。如果沒有BUFG,即使在13.5MHZ CLK上也無法滿足時序要求。我們的問題是LX150設備只有16個BUFG。我們僅將8x用于此模塊,我們的整個系統(tǒng)

2019-07-01 10:20:35

我們已經(jīng)介紹了應用單片機的外設功能的結構和使用方法。本期我們介紹更有效地應用單片機而必須的外設功能——“中斷功能”。

2021-02-25 08:07:05

在我合成一個設計之后,我發(fā)現(xiàn)估計BUFG的使用率是44,但是設備只有32個。所以我想我必須減少我手動使用的BUFG的數(shù)量。但是第一步是我需要在哪里使用這些BUFG,所以在打開合成設計之后,我怎樣才能

2019-03-06 07:37:30

使用7系列FPGA,ISERDES的新時鐘方法出現(xiàn)了,至少我以前從未見過它:由BUFG驅動的CLK,由不同的BUFG驅動的CLKDIV您可以查看這兩個文檔以獲得更好的解釋:7系列:http

2020-07-16 09:42:53

當我放BUFG bufg_axi_rst_i(.O(axi_rst),. I(~frst [0])); //它是https://github.com/Elphel/eddr3/blob/master

2018-10-19 14:38:55

嗨,在我的設計中將Clock引腳連接到BUFG時出現(xiàn)以下錯誤器件為xc7a200tffg1156,引腳編號為P29,是時鐘引腳。解決這個問題應該有什么限制?[放置30-574] IO引腳和BUFG

2020-08-04 06:38:55

建立靈活的、節(jié)省成本的ECU測試系統(tǒng)本文簡要介紹了發(fā)動機控制器的功能和測試。目錄:ECU的歷史ECU的用途為何要測試ECU?測試系統(tǒng)開發(fā)員面臨的挑戰(zhàn)ECU怎樣工作?ECU 功能模塊National

2009-12-14 16:17:03

比較器另一端是ramp 電壓比較器輸出是pulseosc是用referance 電壓的分壓作為 比較器一端輸入(中間有單位緩沖器)發(fā)現(xiàn)vref 受osc 影響不小,在ramp 劍鋒時刻 有小幅震動在電路上有辦法 有效隔離嗎?

2012-01-11 10:00:50

方法是增加一個連接到posedge clk的計數(shù)器,并使用第24位的值來設置clk上的led觸發(fā)器。我讀了一個線程,其中有人使用BUFG根據(jù)計數(shù)器內的一個位創(chuàng)建一個觸發(fā)信號似乎更簡單..但它對我不起作用

2019-06-11 08:41:01

嗨,運行時出現(xiàn)此錯誤:錯誤:[放置30-467]根據(jù)用戶約束,此設計需要在SLR no的下半部分放置17個BUFG實例。 1.由于設備容量限制,這是不可能的。 SLR的每一半只有16個BUFG站點

2018-10-30 18:02:31

Ross Bledsoe寫道:我正在從一系列REAL64中提供多種顏色警報。我試圖將顯示屏上的有效位數(shù)限制為四位。我嘗試在數(shù)字選項卡中更改顏色警報的屬性,沒有效果。有沒有辦法將有效數(shù)字限制為4?感謝

2019-10-31 13:11:55

編寫裸機Bootloader有什么辦法判斷APP是否有效,從而避免重復跳入導致復位再跳入的情況。

2024-02-19 06:19:55

7系列有多少BUFG?我從報告中讀到有128個,這是正確答案嗎?

2020-08-25 15:49:16

嗨!我想知道BUFIO2 + BUFG和ODDR2的解決方案是否用于時鐘路由在時鐘源上可以避免使用Spartan 6(使用直接賦值)已經(jīng)從外部緩沖了。我的意思是,而不是 bufio2_axi_clk

2018-10-23 10:24:05

嗨,我使用IBUFDS將差分時鐘信號轉換為單時鐘信號,這個轉換后的單個clokc信號將用于多個PLL_ADV。那么,我應該為每個PLL_ADV的clk_in添加BUFG嗎?或者我只需要在IBUFDS

2020-07-23 10:57:17

我正在使用Spartan 6 FPGA,并且在我當前的設計中運行低BUFG。如果我阻止工具在DCM環(huán)回(CLK0- > CLKFB)中自動插入BUFG,那將釋放我需要用于其他用途的BUFG。從

2019-07-12 09:38:54

請問信號發(fā)生器是如何效節(jié)省測試時間的?

2021-05-06 07:43:02

你好朋友, 我已經(jīng)獲得了Virtex5 FPGA應用筆記XAPP856,根據(jù)圖6和表3,我們不能使用DCM和BUFG驅動OSERDES來實現(xiàn)SFI-4.1。因為Virtex 5系列中的DCM最多可以

2020-06-10 12:48:08

警告:[放置30-574]具有時鐘功能的IO引腳和BUFG對的次優(yōu)放置。這通常是一個錯誤,但CLOCK_DEDICATED_ROUTE約束設置為FALSE,允許您的設計繼續(xù)。強烈建議不要使用此覆蓋

2020-06-17 11:33:53

在某些情況下,采集此類數(shù)據(jù)可能非常困難。有沒有更好的辦法來采集數(shù)據(jù),并保證數(shù)據(jù)是有效的?本文介紹了幾種數(shù)據(jù)采集應用,并將說明一些不同的工具如何幫助您采集和分析數(shù)據(jù)。

2021-04-09 07:04:11

在線評估貯油罐底部腐蝕狀況的經(jīng)濟有效技術:本文介紹了一種非侵入式罐底腐蝕在線檢測技術。應用該技術可為用戶節(jié)省數(shù)百萬美元的損失。本文在介紹該技術原理的基礎上闡述了

2009-11-24 08:29:27 28

28 層出不窮的信號發(fā)生器可有效節(jié)省測試時間

所有電子電路和電子設備都接收輸入信號,然后將其處理成新的不同的輸出信號。工程師在設計和測試電路及設備時會從哪

2009-11-05 08:53:50 1433

1433 TI最新資料擷取系統(tǒng)可有效節(jié)省75%的功耗、空間及成本--ADS8201

2010-01-08 17:38:04 550

550 無線互訪故障現(xiàn)象及應對辦法介紹

伴隨著無線上網(wǎng)技術的不斷成熟以及無線網(wǎng)絡設備價格的不斷走低,無線局域網(wǎng)的“身影

2010-02-23 14:39:20 455

455 廣東省無線電管理實施辦法 第 一 章 總 則

第一條 為了加強無線電管理,維護空中電波秩序,有效

2010-03-29 11:59:33 578

578 以模擬與數(shù)字電路實驗課程為例,簡述了改進學生實驗考核辦法的必要性,提出了一個有效的可操作的綜合性、設計性實驗考核辦法,并討論了該考核辦法的實施效果和存在的問題。改革學

2011-04-01 12:27:36 0

0 本問介紹了CADENCE軟件組件Allegro開機不能正常啟動的問題的解決辦法

2016-08-18 17:26:55 0

0 當Xilinx 7Series FPGA中,存在3種主要的時鐘網(wǎng)絡:BUFG,BUFR,BUFIO以及他們所衍生出的各種變種。那么他們有什么主要特點和區(qū)別呢? BUFIO是IO時鐘網(wǎng)絡,顧名思義

2017-02-08 05:31:40 2048

2048

本文檔內容介紹了通過運動檢測節(jié)省電池的背光控制。

2017-09-17 10:16:09 2

2 本文檔內容介紹了基于面板與PLC通訊的故障處理辦法。

2017-09-25 18:29:55 4

4 本文首先介紹了音箱發(fā)聲的原理,其次闡述了四種音箱沒聲音的原因和解決辦法,最后還介紹了電腦音箱沒聲音的原因及解決辦法,具體的跟隨小編一起來了解一下。

2018-05-28 14:33:41 42281

42281 本文主要介紹了MES系統(tǒng)無紙化操作可以從這三方面節(jié)省.

2018-06-26 08:00:00 2

2 本文針對Vivado中實現(xiàn)的邏輯鎖定和增量編譯進行的工程實例介紹,文中有對應工程的下載地址。友情提示:(1)增量編譯只允許修改當前工程不超過5%的時候才有效,一般應用于較大工程添加修改

2019-07-06 10:32:42 6746

6746

還會造成模具使用的壽命,那么利用什么辦法來有效去除鋼坯表面的氧化皮呢? 傳統(tǒng)的清理方法已經(jīng)過時,比如說,酸洗、鋼絲刷、打磨、拋丸等。這些方法不僅污染環(huán)境,而且效率低,費工費時,造成人力資源的浪費。隨著高壓水除

2020-10-05 11:31:00 20745

20745 腐蝕電路板的進程中不免會遇到一些疑問,這時分咱們就需求有一些應急的處理辦法,下面電工之家就來介紹一下腐蝕電路時的一些應急處理辦法:

2020-03-22 16:36:00 8525

8525 ,但是使用的方法不一樣,芯片的面積是不一樣的。基于SRAM有兩個事實: (1)1R1W的SRAM面積要比1RW的SRAM的面積大不少。 同樣規(guī)格的SRAM,增加一組讀寫接口,其面積會增加很多。但是有一種辦法其實有可能將本來需要使用1R1W的SRAM改用1RW SRAM替掉,從而節(jié)省

2020-06-22 13:36:09 1116

1116 本文主要介紹了觸摸燈的工作原理及觸摸燈自動亮的解決辦法。

2020-08-11 10:00:02 31982

31982 如果是問保護接地(零)線的接地電阻是否合乎要求(即有效)的話、可以用兩種簡單易行辦法測試。

2020-11-23 15:54:25 8377

8377 電子發(fā)燒友網(wǎng)為你提供6個辦法有效提升電路板的電磁兼容性資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-01 08:40:03 11

11 需憑借專門的儀器查看才干發(fā)現(xiàn)。一般電子產品都有幾十、幾百個元器件,乃至成千上萬個元器件,靠查看每個元器件來發(fā)現(xiàn)其中的毛病,是很困難的。下面介紹下鉭電容檢修辦法。

2021-04-09 11:51:56 860

860 節(jié)省空間,降低EMI

2021-05-20 11:42:15 6

6 問題描述:前幾天我遇到了這個問題,剛開始有點恐慌,以為電腦壞了,就在網(wǎng)上查找各種解決辦法,大多數(shù)人都用長按電源按鈕的方法解決了,但是包括我在內的一些朋友就是不行。解決辦法:最后得知電腦是因為氣溫太低

2022-01-10 12:55:06 7

7 LED顯示屏通訊新號載入不上的原因和解決辦法

2022-02-10 14:43:15 2897

2897 梯云物聯(lián):深圳電梯IP五方對講有什么問題和解決辦法?

2022-04-11 18:16:59 5026

5026 有效解決燃煤電廠再熱管腐蝕的辦法及案例

2022-05-31 15:33:34 0

0 運放輸出鉗位機理及避免辦法

2022-10-28 12:00:21 0

0 AN4515_在STM32F41x系列MCU上應用BAM模式節(jié)省功耗的介紹

2022-11-21 08:11:41 0

0 一站式PCBA智造廠家今天為大家講講什么是PCBA加工焊點拉尖?PCBA加工焊點拉尖產生原因及解決辦法。接下來為大家介紹PCBA加工焊點拉尖產生原因及解決辦法。

2023-05-10 08:56:46 936

936 有些設備管理者在遇到軸類磨損的故障之后,多數(shù)為了節(jié)省,選擇補焊的方法進行維修,但補焊修軸真的有效嗎?會對軸有影響嗎?下面小編給大家一一介紹說明下,看看到底如何有效維修。補焊修軸對軸的影響:補焊會對

2022-02-20 09:53:12 580

580

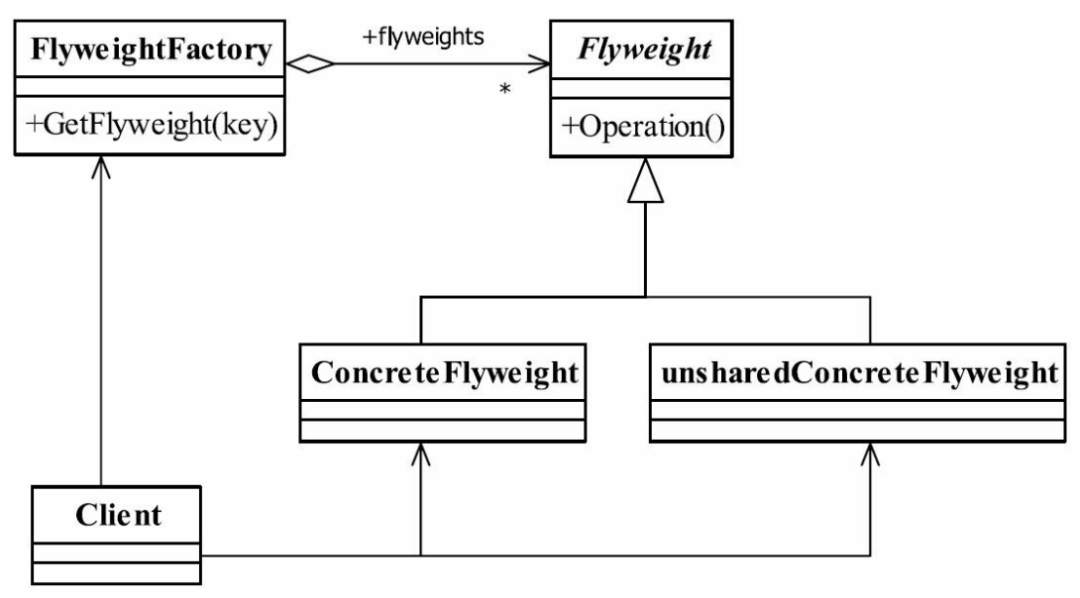

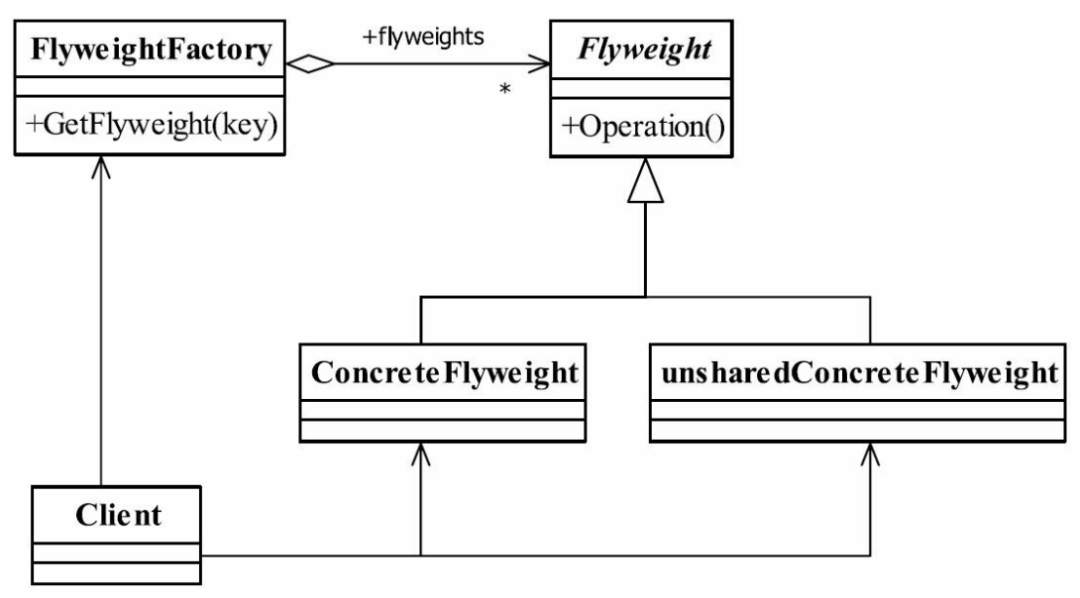

相信大家日常開發(fā)過程中,一個優(yōu)秀的程序猿寫出的代碼一定要節(jié)省空間的,比如節(jié)省內存,節(jié)省磁盤等等。那么如何通過設計模式來節(jié)省內存呢? 1、什么是享元模式? Use sharing to support

2023-10-09 10:31:58 271

271

在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現(xiàn)。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩(wěn)

2024-01-05 14:31:06 454

454

電子發(fā)燒友App

電子發(fā)燒友App

評論