電子發燒友網核心提示 :Xilinx ISE 14.2安裝指南,包括Xilinx ISE 14.2軟件下載、Xilinx ISE 14.2軟件安裝、Xilinx ISE 14.2相關產品介紹、Xilinx ISE軟件激活、Xilinx ISE14.2軟件啟動和Xilinx ISE 14.2新建工

2012-10-31 11:59:13 61264

61264

7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

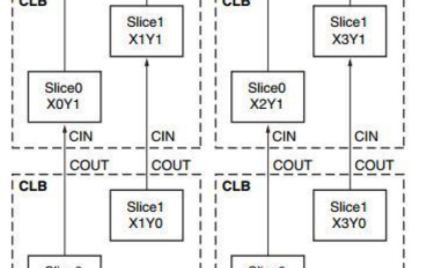

1276 Xilinx FPGA的組成部分 本文是以Xilinx Kintex UltraScale+ 系列為參考所寫,其他系列有所不同,可以參考相應的user guide文檔。 Xilinx家的FPGA有這

2022-12-27 15:54:52 1788

1788 鎖相環基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 2883

2883

。Xilinx FPGA7系列分為全局時鐘(Global clock)和局部時鐘(Regional clock)資源。目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

Xilinx Block Memory Generator(BMG)是一個先進的內存構造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優化的內存。

2023-11-14 17:49:43 736

736

Xilinx7系列普及講座內容請下載附件pdf,更多內容請登錄www.rocetech.com

2013-03-31 14:20:25

Xilinx7系列普及講座內容請下載附件pdf,更多內容請登錄www.rocetech.com

2013-03-31 14:27:04

XILINX FPGA 芯片整體架構是如何構成的?XILINX FPGA 芯片有哪些資源?

2021-10-29 06:26:23

Xilinx Artix7 DEVB_124X92MM 6~16V

2023-03-28 13:05:55

保險絲,保證用戶安全使用開發板15、擴展接口 【主芯片剩余I/O資源均連到擴展接口上】 另外配套了大量的試驗,使用戶方便掌握Xilinx的CPLD/FPGA的編程設計。實驗程序如下:1、串口收發數據

2011-11-17 13:12:57

支持所有Xilinx器件下載 包括FPGA CPLD ISP Configuration PROM 下載接口電壓:5V 3.3V 2.5V 1.8V 1.5V

2023-03-24 15:06:53

可以找到以下資源以獲取幫助以上來自于谷歌翻譯以下為原文 Hello, We purchased a full edition of Xilinx- Vivado/Ise - in March/2016.My

2018-12-21 11:00:57

FPGA最小系統說白了就是設計一個最小系統,其可以作為日后一系列產品的基礎,一是可以加快開發流程,二是可以降低開發難度,本次選用的芯片是Xilinx(賽靈思)的7系列(ARTIX)的FPGA

2021-11-11 07:39:20

LabVIEW資源進行編程,所有其他文件似乎編譯得很好。編譯似乎滯后于Core Generation步驟,大約30分鐘后失敗,并說由于xilinx 13.4錯誤導致編譯失敗。我已經包含了日志文件供您查看。在整個

2020-03-26 10:33:35

xilinx和altera區別分析1. 從好用來說,肯定是Xilinx的好用,不過Altera的便宜他們的特點,Xilinx的短線資源非常豐富,這樣在實現的時候,布線的成功率很高,尤其是邏輯做得比較

2012-02-28 14:40:59

嗨,我在系統生成器2014中使用黑盒子.4在模擬模式下選擇vivado模擬器。如果我運行該項目它正常工作,但如果我在系統生成器或黑盒vhdl中更改某些內容,則會出現此錯誤:Xilinx模塊庫中發

2018-10-30 11:07:57

大家好,我一直在從一系列合成迭代開始和關閉這些迭代。有人能告訴我為什么會這樣嗎?時鐘太多了?解決辦法是什么?[形狀生成器18-119]未能創建I / OLOGIC借道形狀例如system_i

2018-10-19 14:35:03

ADAPTER TC2050 FOR XILINX CABLE

2023-03-22 19:59:52

Cortex-A9 處理器,但該器件上的 FPGA 數量存在差別,如表 1 所示:[td]Xilinx Zynq SoC可編程邏輯單元塊 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

`如題,打算拿手里的十萬邏輯資源Altera板子交換Xilinx板子,現在只打算換Xilinx的FPGA的板子,可以是自己做的或者是其他,但一定要好使的!板子是自己設計的,也是自己焊接的,焊接的比較

2015-06-19 21:38:36

遇到了意外錯誤。建議您在此情況持續存在的情況下保存任何未保存的工作。如需進一步的幫助,請參閱http://support.xilinx.com上的答案數據庫和其他在線資源有任何建議如何解決這個問題?謝謝。

2020-05-29 16:06:51

RAM)的時延和抖動都為最小。為了適應復雜設計的需要,Xilinx的FPGA中集成的專用時鐘資源與數字延遲鎖相環(DLL)的數目不斷增加,最新的Virtex II器件最多可以提供16個全局時鐘輸入端口和8

2019-10-22 06:01:34

HY,我想在xilinx Blockset中估計FFT7.1塊的各個體系結構的資源。有沒有辦法做到這一點?當我嘗試使用“資源估計器”-Block時,結果總是43個IOB。問候Jan以上來自于谷歌翻譯

2018-10-16 07:21:32

'une erreur Xilinx。詳細信息:錯誤:位置:906- 由于位置限制導致違反時鐘區域規則,因此無法放置和路由由IO時鐘網絡驅動的組件。 IO時鐘網被BUFIO驅動鎖定到站

2018-10-19 14:36:19

FPGA的特點及其發展趨勢IP資源復用理念與IP Core設計基于Xilinx FPGA的嵌入式系統設計

2021-04-30 07:21:50

嗨,我是FPGA編程的新手。我在Xilinx ISE中使用VHDL進行設計。我的綜合結果包括:FF,LUT,內存LUT,I / O,BRAM,DSP48,BUFG。我非常感謝能夠幫助我解釋每個資源

2020-03-24 10:14:15

某些Xilinx資源包含一個顯示“所有版本”鏈接的按鈕。有沒有所有版本的xapp1052.zip可用的地方?謝謝,埃米特

2020-04-30 08:18:45

UART 4 UART參考設計,Xilinx提供Verilog代碼 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 usb xilinx代碼,usb xilinx源代碼,usb xilinx程序

The lack of flexibility in reconfiguring the PC has been

2009-06-14 09:04:25 41

41 Xilinx Sol

2009-11-28 11:56:48 14

14 怎樣寫testbench-xilinx

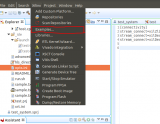

在ISE 環境中, 當前資源操作窗顯示了資源管理窗口中選中的資源文件能進行的相關操作。在資源管理窗口選中了 testbench 文件后

2010-02-09 13:46:12 64

64 Xilinx下載電纜原理圖

2011-01-18 16:09:34 114

114 xilinx實驗板原理圖:

2012-03-20 14:02:47 235

235 本書系統地論述了Xilinx FPGA開發方法、開發工具、實際案例及開發技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發基礎與進階、Xilinx FPGA電路原理與系統設計

2012-07-31 16:20:42 11268

11268

Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發環境的配置

2016-01-18 15:30:20 32

32 Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發環境

2016-01-18 15:30:32 45

45 xilinx_ise9.01中文教程 xilinx_ise9.01中文教程

2016-02-18 18:16:58 0

0 Xilinx FPGA工程例子源碼:Xilinx EDK設計試驗

2016-06-07 14:54:57 9

9 Xilinx FPGA工程例子源碼:Xilinx 公司的加法器核

2016-06-07 15:07:45 12

12 Xilinx FPGA工程例子源碼:Xilinx 高級試驗的代碼

2016-06-07 15:07:45 19

19 Xilinx FPGA工程例子源碼:Xilinx 的I2C工程

2016-06-07 15:07:45 25

25 Xilinx FPGA工程例子源碼:Xilinx.CPLD源碼參考設計

2016-06-07 15:07:45 33

33 xilinx原語的使用,建議有一定經驗的參考。

2016-12-17 11:58:56 13

13 Xilinx學習資料

2017-01-31 20:43:43 68

68 談到數字邏輯,談到FPGA設計,每位工程師都離不開時鐘。這里我們簡單介紹一下xilinx 7 系列中的時鐘資源。時鐘設計的好壞,直接影響到布局布線時間、timing的收斂情況,FPGA的時鐘

2017-02-08 05:33:31 561

561

。從新手的角度,我想談一下自己的一些感受: 網絡資源: xilinx主要是做FPGA的,以前沒有接觸過,zynq是接觸的第一個xilinx的產品,總體上感覺資源比較豐富,論壇,文檔資料都能輕易獲取,就是對英文水平有較高要求,官網上的資源,文檔基本都是英文的,所以英文必須得過關。

2017-02-08 06:31:11 209

209 1. Xilinx 時鐘資源 xilinx 時鐘資源分為兩種:全局時鐘和第二全局時鐘。 1. 全局時鐘資源 Xilinx 全局時鐘采用全銅工藝實現,并設計了專用時鐘緩沖與驅動結構,可以到達芯片內部

2017-02-09 08:43:41 1315

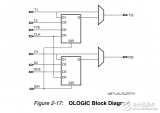

1315 Virtex-6每個I/O片(I/O Tile)包含兩個IOB、兩個ILOGIC、兩個OLOGIC 和兩個IODELAY,如圖5-24 所示。

2017-02-11 09:21:12 2426

2426

xilinx 約束實現

2017-03-01 13:12:47 15

15 Xilinx TI LVDS 參考設計

2017-03-01 13:13:09 16

16 最重磅的發布,最新的視頻和白皮書,還有最新的課程介紹,以及來自 Xilinx 合作伙伴和客戶的成功案例,實用工具和套件分享。一文即可掌握,本月我們給您帶來了什么樣的資源,點擊“閱讀原文”閱讀詳情。

2017-09-20 11:39:57 3236

3236 xilinx 原語使用方法

2017-10-17 08:57:42 11

11 xilinx原語使用方法

2017-10-19 08:50:39 15

15 Xilinx機器視覺導論

2017-10-27 08:38:09 6

6 Xilinx FPGA的Maxim參考設計

2017-10-31 09:59:24 23

23 在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

這一次給大家分享的內容主要涉及Xilinx FPGA內的CLBs,SelectIO和Clocking資源,適合對FPGA設計有時序要求,卻還沒有足夠了解的朋友。

2018-03-21 14:48:00 4672

4672

共同愿景就是幫助用戶簡化設計,降低開發門檻,讓用戶更多關注創新本身,甩掉硬件設計與調試的煩惱。威視銳與Xilinx將提供更多面向行業的解決方案,加快FPGA的創新應用。

在Xilinx的30

2018-06-06 02:45:00 3934

3934 Xilinx Zynq?-7000

2018-06-04 13:47:00 3392

3392 介紹賽靈思為各企業提供的專業的關于Xilinx的資源培訓,以及課程內容

2018-05-22 13:47:33 3154

3154

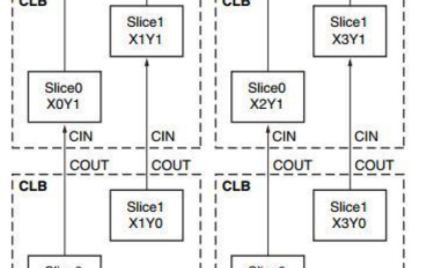

現在的FPGA里面有很多存儲資源,DSP(數字信號處理)資源,布線通道,I/O資源,當然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構。

2018-10-22 11:00:43 5270

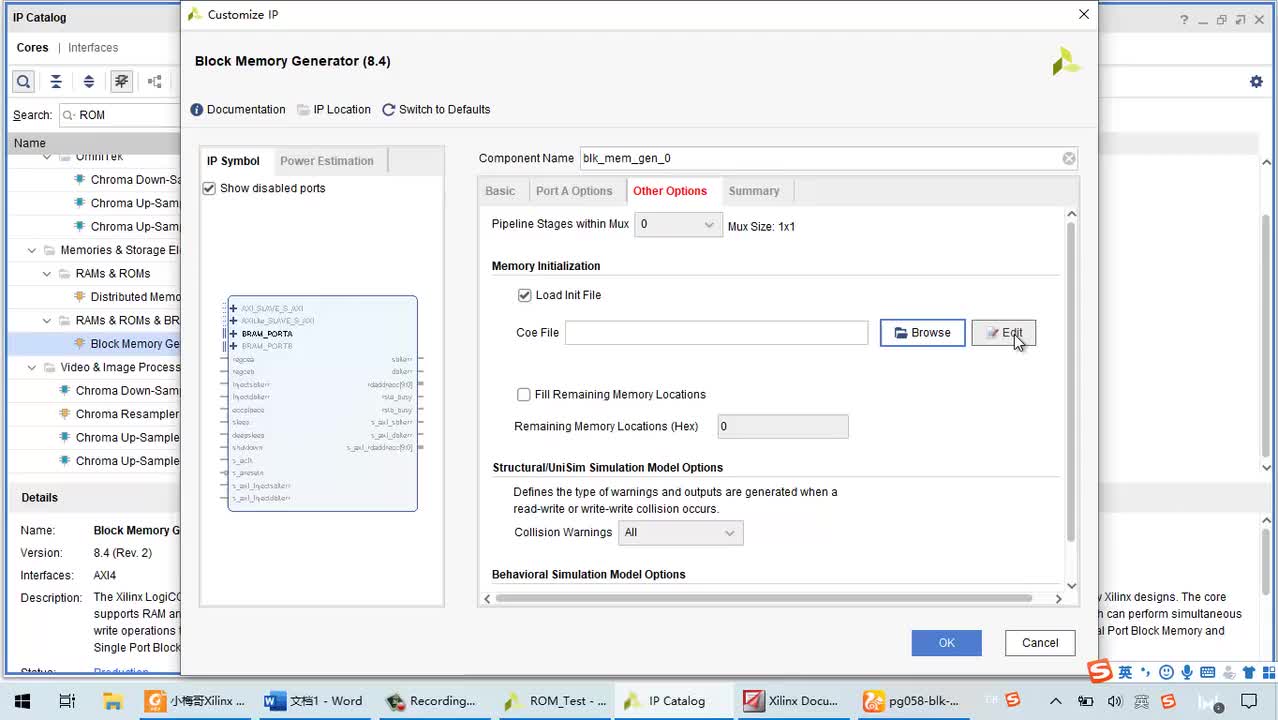

5270 Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。

2018-12-16 11:31:21 12305

12305

Xilinx FPGA有三種可以用來做片上存儲(RAM,ROM等等)的資源,第一個就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。 在用Vivado建立

2019-09-15 12:21:00 4826

4826

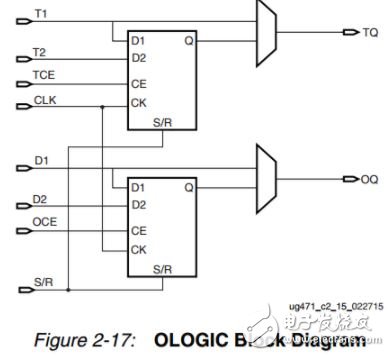

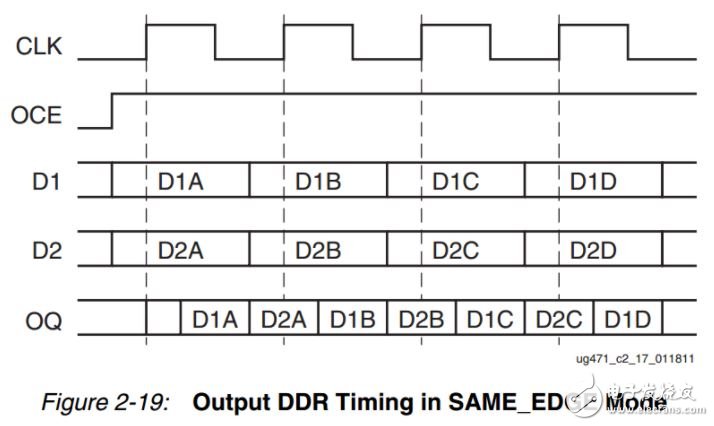

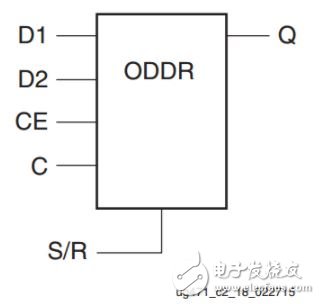

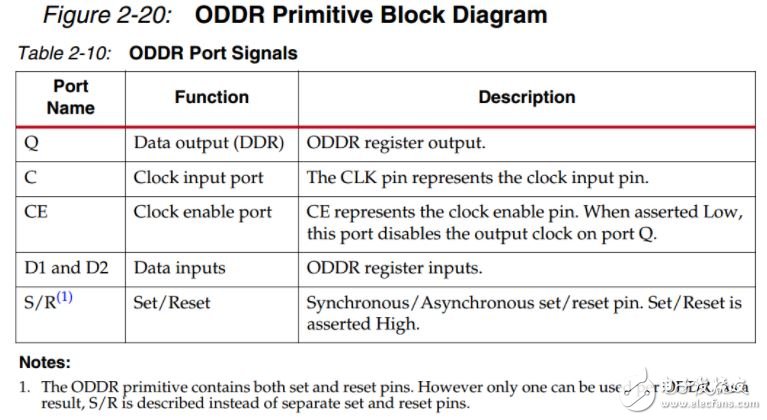

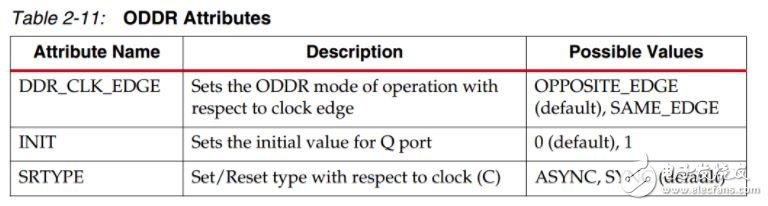

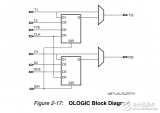

OLOGIC塊在FPGA內的位置緊挨著IOB,其作用是FPGA通過IOB發送數據到器件外部的專用同步塊。

2019-02-17 10:55:30 35932

35932

Xilinx的FPGA的基本結構是一樣的,主要由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等。

2019-06-11 14:28:17 3600

3600

命名規則 5.7系列資源概括 1.Xilinx的四個工藝級別 Xilinx目前主要產品有四個工藝等級,通常情況下,Xilinx的產品每個工藝都會有Spartan、Artix、Kintex和Virtex

2020-11-13 18:03:30 14065

14065 Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達?-7系列是7系列產品中密度最低、成本最低的入門級產品

2020-12-09 14:49:00 24

24 本文檔的主要內容詳細介紹的是FPGA的RAM存儲資源詳細資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構及應用

2020-12-09 15:31:00 10

10 Xilinx LogiCORE IP塊內存生成器(BMG)內核是一種高級內存構造函數,它使用XilinxFPGAs中的嵌入式塊RAM資源生成區域和性能優化的內存。

2020-12-09 15:31:00 22

22 Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達?-7系列是7系列產品中密度最低、成本最低的入門級產品

2020-12-09 15:31:13 9

9 Xilinx7系列FPGA的體系結構具有靈活的內部內存資源,可以配置為各種不同的大小。本白皮書詳細介紹了可用的功能,說明了各種可用內存大小,并顯示了使用不同資源執行不同大小內存功能的利弊。

2020-12-09 16:15:00 8

8 Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達-7系列是7系列產品中密度最低、成本最低的入門級產品

2020-12-10 14:20:00 18

18 結合Xilinx、Altera 等公司的FPGA 芯片,簡要羅列一下FPGA 內部的資源或專用模塊,并簡要說明這些資源的一些作用或用途。(至少列出5 項,越多越好)

2020-12-25 17:34:00 16

16 xilinx FPGA的資源一般指IOB,CLB,BRAM,DCM,DSP五種資源。其中IOB就是input/output block,完成不同電氣特性下對輸入輸出信號的的驅動和匹配要求。

2020-12-29 16:59:33 12

12 全局時鐘資源是一種專用互連網絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 本篇咱們接著介紹I/O邏輯資源,先貼上兩張圖。圖1為HPBANK的I/O模塊,圖2為HRBANK的I/O模塊,兩者區別在于后者無ODELAYE模塊。

2020-12-29 17:27:00 3

3 OLOGIC塊在FPGA內的位置緊挨著IOB,其作用是FPGA通過IOB發送數據到器件外部的專用同步塊。OLOGIC 資源的類型有OLOGIC2(位于HP I/O banks)和OLOGIC2(位于

2020-12-30 16:27:50 9

9 SRL(移位寄存器)資源,在FPGA中都有,不過是叫不同的名字。Xilinx FPGA內部的LUT有個特殊功能,就是可以配置成可變長度SRL。

2020-12-31 16:45:35 8

8 引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 4353

4353

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 自從 Vitis 發布后,Xilinx 在 Github 上持續開源了很多資源,方便開發者進行自己的設計,減少產品上市時間。所以本期文章我們來看下如何獲取和使用 Github 上的開放資源。

2021-04-09 11:51:40 3129

3129

Xilinx參考設計(維基網站)

2021-05-12 10:00:30 3

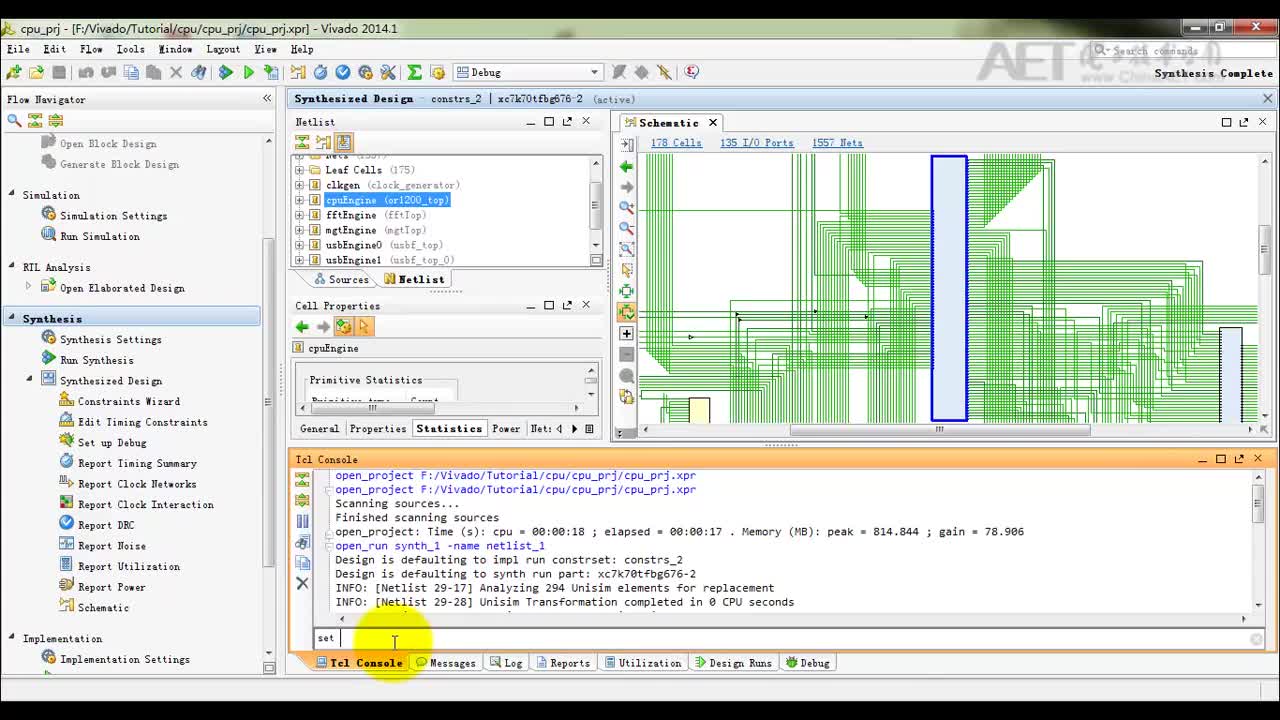

3 在vivado中 ,如何查看各個模塊的資源占用情況呢?方法如下。以在xilinx官方評估板VC709的microblaze的軟核處理器例程為例。工程如下圖模塊組成。

2022-07-08 10:01:27 9566

9566 Xilinx FPGA pcb設計

2023-05-29 09:11:36 0

0 VicorPoweringInnovation播客介紹了OLogic如何推崇高密度電源模塊來推動當今的機器人革命從玩具到建筑工地工具OLogic加速機器人創意從概念到生產的進程馬薩諸塞州安多

2024-02-28 00:00:00 776

776

VicorPoweringInnovation播客介紹了OLogic如何推崇高密度電源模塊來推動當今的機器人革命從玩具到建筑工地工具OLogic加速機器人創意從概念到生產的進程馬薩諸塞州安多

2024-02-28 00:00:00 748

748

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 215

215

電子發燒友App

電子發燒友App

評論