本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析。

2018-04-18 09:06:24 15422

15422

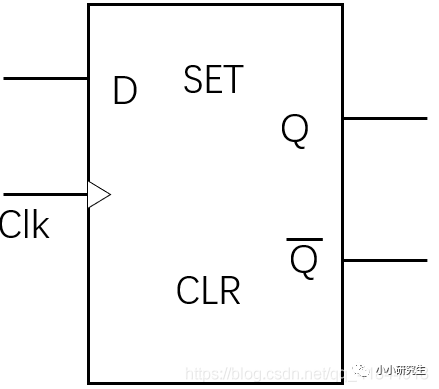

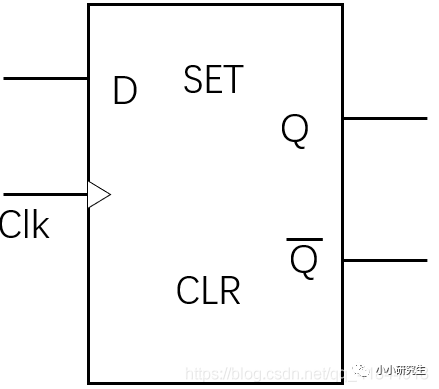

在數字電路中,凡是任一時刻的穩定輸出不僅決定于該時刻的輸入,而且還和電路原來狀態有關者都叫時序邏輯電路。時序邏輯電路結構示意圖如圖2-41所示。時序邏輯電路的狀態是靠具有存儲功能的觸發器所組成的存儲電路來記憶和表征的。

2018-01-31 09:27:23 53525

53525

表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 2768

2768

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 數字電路根據邏輯功能的不同特點,可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另一類叫做時序邏輯電路,簡稱時序電路或時序邏輯。

2022-12-01 09:04:04 459

459 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-01-13 13:57:47 1830

1830

數字邏輯電路分為組合邏輯電路和時序邏輯電路。時序邏輯電路是由組合邏輯電路和時序邏輯器件構成(觸發器),即數字邏輯電路是由組合邏輯和時序邏輯器件構成。

2023-03-21 09:49:49 476

476 FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-06 17:53:07 860

860

時序路徑作為時序約束和時序分析的物理連接關系,可分為片間路徑和片內路徑。

2023-08-14 17:50:02 452

452

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

芯片設計是現代電子設備的重要組成部分,其中組合邏輯和時序邏輯是芯片設計中非常重要的概念。組合邏輯和時序邏輯的設計對于構建復雜的電路系統至關重要。

2023-08-30 09:32:15 809

809 大神求救!我現在想要用FPGA實現一個數與一個數組(寬度為64)數相乘,累加,再取平均,用的是時序邏輯加上非阻塞賦值的方法實現,即從數組0開始相乘,一直到數組63,當乘完63時,將累加的數取平均輸出

2017-09-13 11:02:51

經過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據一些官方的文件對時序分析進行更系統、深入的學習。先總結一下之前

2011-09-23 10:26:01

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種FPGA中的IPO時序優化設計的方案, 切實有效的解決了IPO接口中的時序同步問題。

2012-08-12 11:57:59

FPGA畢竟不是ASIC,對時序收斂的要求更加嚴格,本文主要介紹本人在工程中學習到的各種時序約束技巧。 首先強烈推薦閱讀官方文檔UG903和UG949,這是最重要的參考資料,沒有之一。它提倡

2020-12-23 17:42:10

以及高速數字電路的時序設計與優化。相信通過三天的學習,將會對學員在邏輯設計領域的工作和學習大有裨益。課程時間的安排上授課占60%,實驗占40%。五、培訓對象課程適合于使用FPGA器件進行科研、教學和產品

2009-07-24 13:13:48

基本的時序分析理論1本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態時序分析(STA,Static

2015-07-09 21:54:41

基本的時序分析理論2本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們再來看一個例子,如圖8.2所示

2015-07-14 11:06:10

基本時序路徑本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 對于FPGA內部而言,通常有四大類的基本時序

2015-07-20 14:52:19

CMOS攝像頭接口時序設計1理想時序(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-12 12:42:14

CMOS攝像頭接口時序設計5時序報告(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s

2015-08-19 21:58:55

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

FPGA重要設計思想及工程應用之時序及同步設計希望對大家有用

2016-04-24 22:31:46

實戰應用,這種快樂試試你就會懂的。話不多說,上貨。 數字電路中的時序邏輯 在各種復雜的數字電路中,不但需要對二值信號進行算數運算和邏輯運算,還經常需要將這些信號和運算結果保存起來。為此,需要

2023-02-22 17:00:37

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

時序邏輯電路的設計實驗1 進一步強化EDA仿真軟件的使用;2 掌握利用MSI

2009-03-19 15:10:18

當邏輯行為以默認的方式不能正確的定時邏輯行為,想以不同的方式處理時序時,必須使用時序例外命令。1. 多周期路徑約束指明將數據從路徑開始傳播到路徑結束時,所需要的時鐘周期

2018-09-21 12:55:34

`Xilinx FPGA入門連載37:SRAM讀寫測試之時序解讀特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 SRAM讀寫時序解讀

2015-12-16 12:46:04

根據邏輯電路的不同特點,數字電路分為組合邏輯和時序邏輯,明德揚粉絲里的同學提出,無法正確區分,今天讓我跟一起來學習一下兩種邏輯的區別以及使用環境。·時序邏輯和組合邏輯的區別關于組合邏輯和時序邏輯

2020-03-01 19:50:27

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2019-08-11 08:30:00

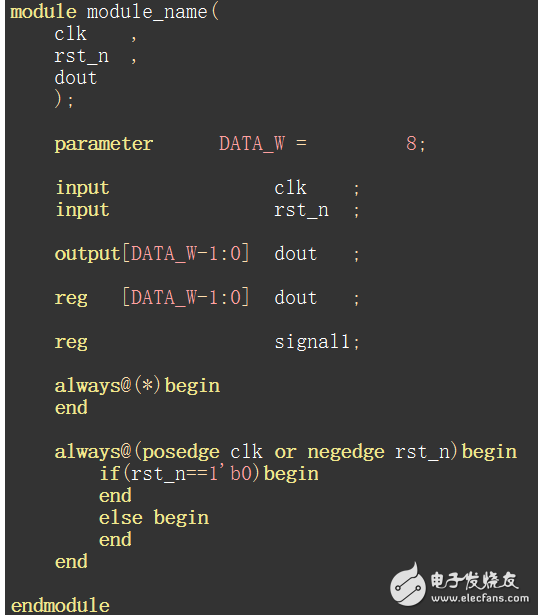

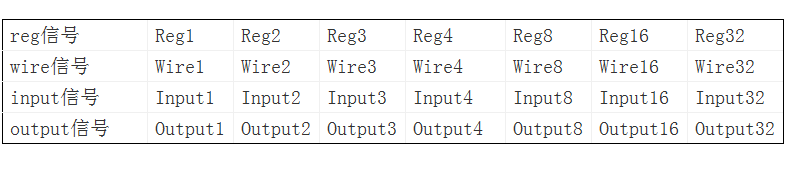

,就能使用這些模板了。1.時序邏輯的模板在GVIM輸入“Module”并回車,如下圖所示就能得到下面的時序邏輯的模板。模塊的模板包括了輸入輸出信號列表、信號定義,組合邏輯和時序邏輯等,這是一個模塊常用

2017-05-08 15:02:21

為什么FPGA可以用來實現組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

什么是時序邏輯?時序邏輯由哪幾部分構成?

2021-09-17 07:43:37

```勇敢的芯伴你玩轉Altera FPGA連載25:組合邏輯與時序邏輯特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 數字電路按照邏輯

2017-11-17 18:47:44

的。話不多說,上貨。 在FPGA中何時用組合邏輯或時序邏輯 在設計FPGA時,大多數采用Verilog HDL或者VHDL語言進行設計(本文重點以verilog來做介紹)。設計的電路都是利用

2023-03-06 16:31:59

涉及時序邏輯電路的實例,希望能夠幫助大家理解在FPGA中實現時序邏輯電路。與組合邏輯電路相比,時序邏輯電路需要時鐘的參與,電路中會有存儲器件的參與,時序邏輯電路的輸出不僅取決于這一時刻的輸入,也受此

2022-07-22 15:25:03

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2021-05-18 15:55:00

了如何通過FPGA實現RS 232接口的時序邏輯設計。關鍵詞:FPGA;時序電路;RS 232;串行通信

2019-06-19 07:42:37

時序分析是FPGA設計的必備技能之一,特別是對于高速邏輯設計更需要時序分析,經過基礎的FPGA是基于時序的邏輯器件,每一個時鐘周期對于FPGA內部的寄存器都有特殊的意義,不同的時鐘周期執行不同的操作

2017-02-26 09:42:48

器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。基本的電子系統如圖 1所示,一般自己的設計都需要時序分析,如圖 1所示的Design,上部分為時序組合邏輯,下部分只有組合

2018-04-03 11:19:08

輸入“Shixu2”并回車就能得到帶有2個if條件的時序邏輯代碼。3.輸入“Shixu3”并回車就能得到帶有3個if條件的時序邏輯代碼。歡迎關注明德揚公眾號“fpga520”,或群97925396,索取明德揚模板。口號:多用模板,減少記憶,專注設計!

2017-04-26 16:08:40

,就能使用這些模板了。1.模塊的模板在GVIM輸入“Module”并回車,如下圖所示就能得到下面的模塊的模板。模塊的模板包括了輸入輸出信號列表、信號定義,組合邏輯和時序邏輯等,這是一個模塊常用的組件

2017-11-29 15:19:11

時序邏輯電路的輸出不但和當前輸入有關,還與系統的原先狀態有關,即時序電路的當前輸出由輸入變量與電路原先的狀態共同決定。為達到這一目的,時序邏輯電路從某一狀態

2009-03-18 22:13:04 71

71 同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 中規模集成時序邏輯設計:計數器:在數字邏輯系統中,使用最多的時序電路要算計數器了。它是一種對輸入脈沖信號進行計數的時序邏輯部件。9.1.1 計數器的分類1.按數制

2009-09-01 09:09:09 13

13 異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 0

0 FPGA重要設計思想及工程應用之時序及同

在FPGA設計中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設計項目中的每一個觸發 器

2010-02-09 10:29:36 51

51 數字邏輯電路按邏輯功能和電路組成的特點可分為組合邏輯電路和時序邏輯電路兩大類。

2010-08-10 11:51:58 39

39 虛擬FPGA邏輯驗證分析儀的設計

隨著FPGA技術的廣泛使用,越來越需要一臺能夠測試驗證FPGA芯片中所下載電路邏輯時序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 8146

8146

當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1169

1169 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 FPGA重要設計思想及工程應用之時序及同步設計

2016-05-10 11:24:33 16

16 電子專業單片機相關知識學習教材資料之時序邏輯電路的分析與設計

2016-09-02 14:30:26 0

0 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設計中的時序問題

2017-01-14 12:49:02 14

14 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。設計者現在有一些

2017-02-09 01:59:11 264

264 fpga時序收斂

2017-03-01 13:13:34 23

23 這是特權同學的關于fpga時序分析方面的極好資料

2017-08-28 11:19:14 20

20 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 2951

2951 控制器,在介紹控制器的邏輯結構的基礎上,對FPGA與SDRAM間數據通信進行了時序分析,實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

2017-11-18 12:42:03 2054

2054

數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2017-11-20 12:26:21 8630

8630 的數量,可以用消耗的觸發器和查找表的個數或者是等效邏輯門數來衡量;速度是指一個設計在FPGA上穩定運行時所能 達到的最高頻率,由設計時序狀態決定。 關于面積和速度的折衷,應在滿足設計時序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規定

2017-11-25 03:57:01 802

802

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 123040

123040

本文開始介紹了時序邏輯電路的特點和時序邏輯電路的三種邏輯器件,其次介紹了時序邏輯電路的組成與時序邏輯電路檢修方法,最后介紹了時序邏輯電路的應用舉例。

2018-03-01 10:53:38 106881

106881

FPGA設計一個很重要的設計是時序設計,而時序設計的實質就是滿足每一個觸發器的建立(Setup)/保持(Hold)時間的要求。

2018-06-05 01:43:00 4150

4150

本文檔的主要內容詳細介紹的是數字電路基礎教程之時序邏輯電路的詳細資料概述。內容包括了:1.時序邏輯電路分析2.若干常用時序邏輯電路3.時序邏輯電路設計

2018-10-17 08:00:00 0

0 時序邏輯電路對于組合邏輯的毛刺具有容忍度,從而改善電路的時序特性。同時電路的更新由時鐘控制。

2018-11-24 11:17:51 3197

3197

本文檔的主要內容詳細介紹的是數字電路教程之時序邏輯電路課件的詳細資料免費下載主要內容包括了:一 概述,二 時序邏輯電路的分析方法,三 若干常用的時序邏輯電路,四 時序邏輯電路的設計方法,五 時序邏輯電路中的競爭冒險現象

2018-12-28 08:00:00 12

12 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2019-02-26 15:22:20 30485

30485 時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發器、 寄存器和計數器等。

2019-02-26 15:25:01 49628

49628 本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

2019-03-27 10:56:04 20

20 FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸入輸出模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。

2019-12-02 07:05:00 1522

1522

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 2539

2539

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-03 07:04:00 2191

2191

典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。

2020-01-27 10:37:00 2460

2460

本文檔的主要內容詳細介紹的是模擬電路教程之時序邏輯電路的課件資料免費下載包括了:1 概述,2 時序邏輯電路的分析方法,3 若干常用的時序邏輯電路,4 時序邏輯電路的設計方法。

2020-06-22 08:00:00 13

13 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 18

18 典型電路的模板1 模板代碼1.1 輸出時序邏輯的模板代碼1.1.1 異步復位的時序電路(用的最多)1.1.2 同步復位的時序電路1.2 輸出組合邏輯的模板代碼1.3 輸出整個模塊部分代碼1.4 輸出

2021-12-22 18:57:03 4

4 本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

2022-03-16 09:17:19 3255

3255

上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 數字門級電路可分為兩大類:組合邏輯和時序邏輯。鎖存器是組合邏輯和時序邏輯的一個交叉點,在后面會作為單獨的主題處理。

2023-02-12 10:28:36 771

771 時序邏輯的代碼一般有兩種: 同步復位的時序邏輯和異步復位的時序邏輯。在同步復位的時序邏輯中復位不是立即有效,而在時鐘上升沿時復位才有效。 其代碼結構如下:

2023-03-21 10:47:07 400

400 FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 768

768 時序邏輯電路會復雜很多,強烈推薦mooc上華中科技大學的數字電路與邏輯設計,是我看過講得最清楚的數電課。

2023-05-14 15:11:33 1693

1693

?時序邏輯電路分為同步時序邏輯電路和異步時序邏輯電路兩大類。

2023-06-21 14:35:58 2539

2539

典型的時序路徑有4類,如下圖所示,這4類路徑可分為片間路徑(標記①和標記③)和片內路徑(標記②和標記④)。

2023-06-26 10:30:43 247

247

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 344

344

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 時序邏輯電路 一 : 觸發器 1:D 觸發器 : 時序邏輯電路最小單元 。 (1):D 觸發器工作原理 忽略清零端情況下 : 當使能條件 ( 往往為時鐘的觸發沿 : 上升沿 / 下降沿 ) 滿足

2023-11-02 12:00:01 308

308

時序邏輯電路是一種能夠存儲信息并根據時鐘信號按照特定順序執行操作的電路。它是計算機硬件中非常重要的一部分,用于實現存儲器、時序控制器等功能。與之相對的是組合邏輯電路,它根據輸入信號的組合情況,立即

2024-02-06 11:18:34 499

499

![]()

![]()

![]()

![]()

![]()

電子發燒友App

電子發燒友App

評論