通常來講,“一個好漢三個幫”,一個完整的嵌入式系統中由單獨一個FPGA使用的情況較少。##系統架構確定,下一步就是FPGA與各組成器件之間互聯的問題了。

2015-05-12 13:41:18 2836

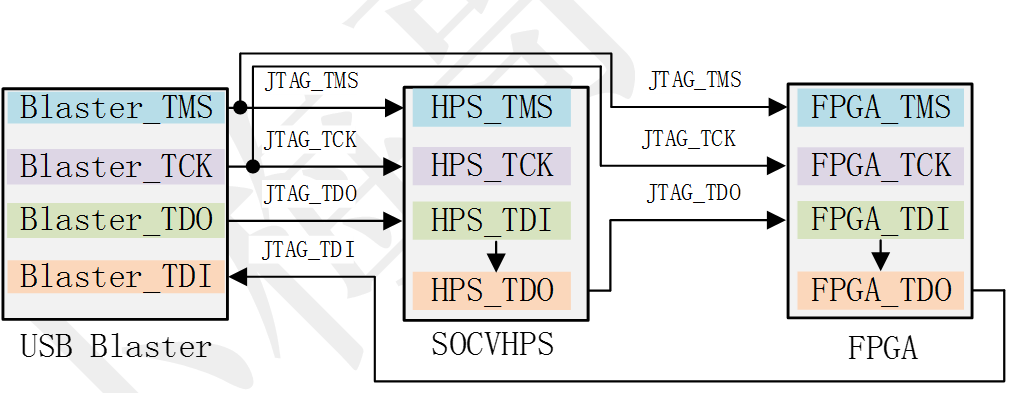

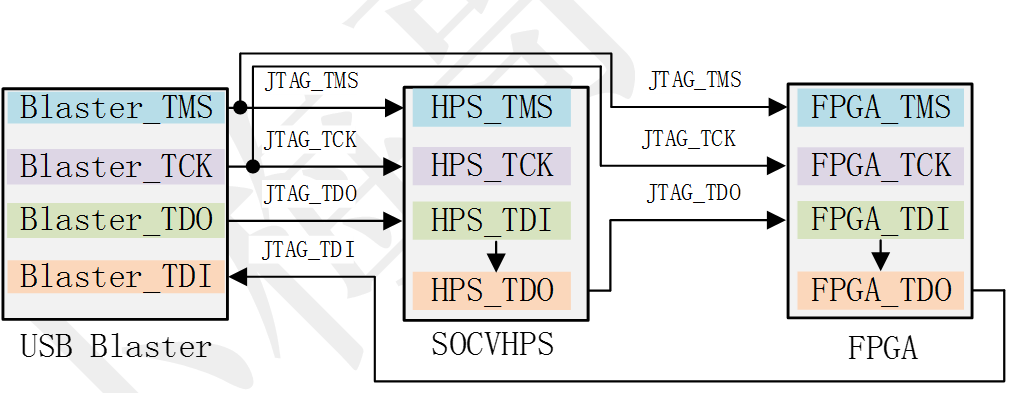

2836 SoC FPGA作為在同一芯片上同時集成了FPGA和HPS的芯片,其JTAG下載和調試電路相較于單獨的FPGA或ARM處理器都有一些差異,但是同時兩者又有緊密的聯系。

2020-08-08 10:08:00 1633

1633

Kintex-7 FPGA的內部結構相比傳統FPGA的內部結構嵌入了DSP48E1,PCIE,GTX,XADC,高速IO口等單元,大大提升了FPGA的性能。

2023-08-24 09:26:56 1393

1393

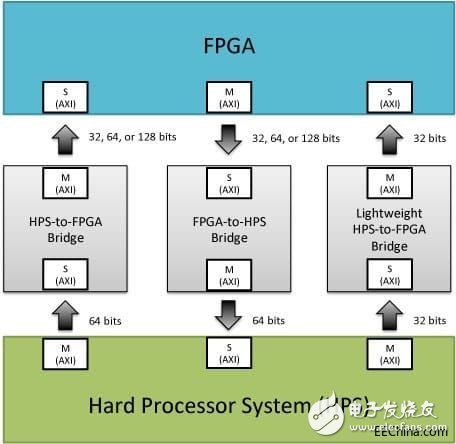

。 值得一提的是Altera SoC使用寬帶干線互聯,在HPS和FPGA架構之間的大吞吐量數據通路實現了雙芯片解決方案無法提供的互聯性能。HPS和FPGA架構的緊密集成提供了100-Gbps的峰值帶寬,在處理器

2014-08-01 14:12:39

下面給大家介紹FPGA LUT的結構

2018-07-09 04:57:10

可編程邏輯(FPGA)與硬核處理器(HPS)之間互聯的結構

2021-04-02 06:03:40

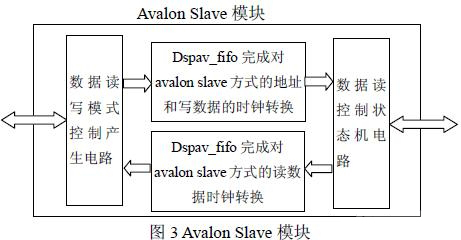

(Flexible static memory controller)接口用于MCU與FPGA之間的通訊最近使用的一款MCU與FPGA之間通訊,FPGA模擬成NAND Flash作為Memory讓MCU讀寫FPGA與MCU之間的連接方式如下所示上述信號定義如下這里可以看到,NAND flash訪問是,Maste

2021-11-01 07:11:31

本帖最后由 rousong1989 于 2015-1-27 11:45 編輯

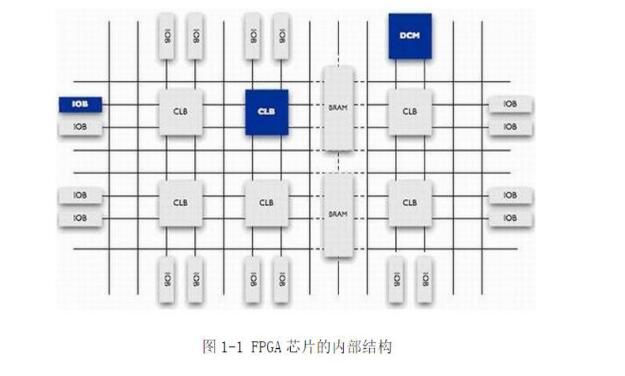

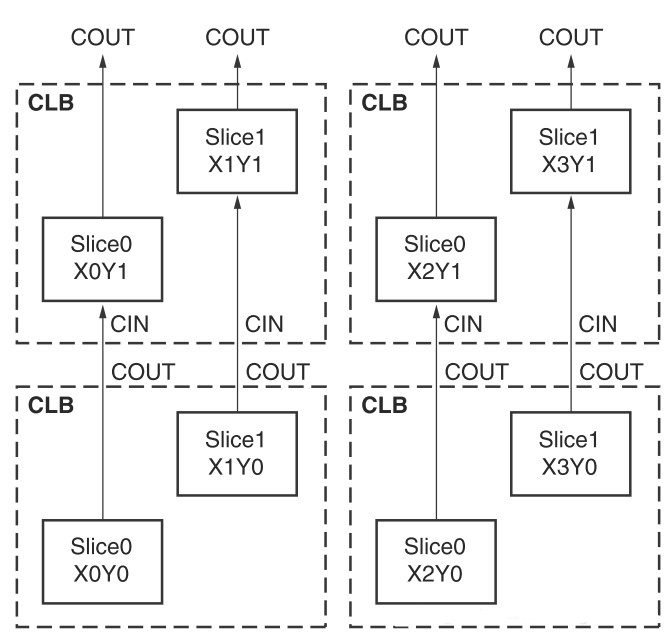

FPGA入門:內里本質探索——器件結構本文節選自特權同學的圖書《FPGA/CPLD邊練邊學——快速入門

2015-01-27 11:43:10

可重構設計是指利用可重用的軟、硬件資源,根據不同的應用需求,靈活地改變自身體系結構的設計方法。FPGA器件可多次重復配置邏輯的特性使可重構系統成為可能,使系統兼具靈活、便捷、硬件資源可復用等性能

2011-05-27 10:22:36

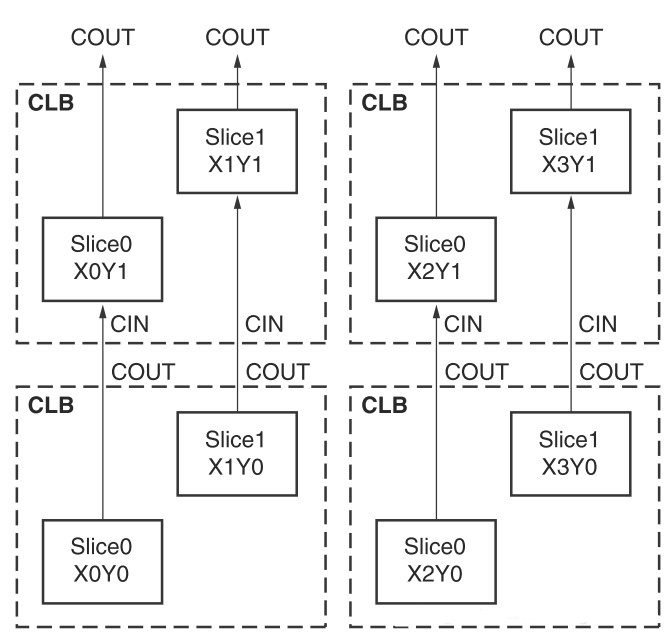

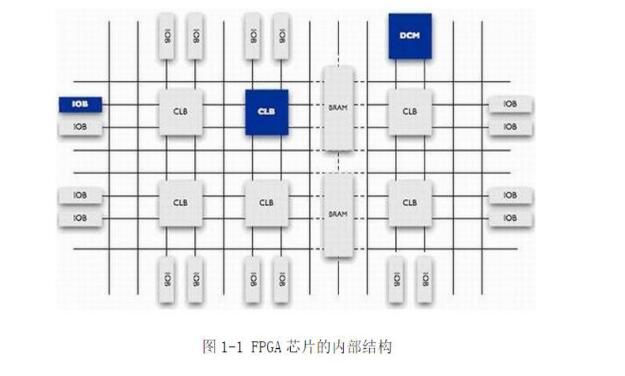

,實際上每一個系列的FPGA都有其相應的內部結構),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內嵌的底層功能單元和內嵌

2017-05-09 15:10:02

FPGA實現邏輯函數用的什么電路結構?

2017-01-01 21:49:23

FPGA的I/O結構的發展的怎么樣了?

2021-04-29 06:12:52

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結構 FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等。 每個單元簡介如下: 1.

2016-10-08 14:43:50

系統架構確定,下一步就是FPGA與各組成器件之間互聯的問題了。通常來說,CPU和FPGA的互聯接口,主要取決兩個要素:(1)CPU所支持的接口。(2)交互的業務。通常來說,FPGA一般支持與CPU

2018-08-06 11:52:32

AD9674與AD9276的數據輸出采用的是LVDS輸出接口,現在準備用AD9674做一個超聲波設備,但是數據采集方案一直沒弄出來,看著英文文檔實在老火啊,對FPGA也不太了解,現在是如何用FPGA采集出AD9674的數據呢,AD9674與FPGA之間如何連接?

2023-12-21 07:31:42

咨詢一個初級A/D問題:AD9684中DCO時鐘的用法(FPGA控制)。AD9684與FPGA用LVDS模式接口互聯時,FPGA端如何使用?手冊中沒有詳細說明,是DCO上升沿捕獲數據,作為數據同步

2023-12-13 09:01:52

求大神幫忙解答下,altera soc 的HPS部分的引腳配置如何自動生成,怎么我改動了下qsys里面的HPS配置,怎么無法生成fitter location 來配置hps部分的引腳

2018-03-14 12:02:41

SoCFPGA器件在一個器件中同時集成了處理器和FPGA體系結構。將兩種技術合并起來具有很多優點,包括更高的集成度、更低的功耗、更小的電路板面積,以及處理器和FPGA之間帶寬更大的通信等等。這一同類最佳的器件發揮了處理器與FPGA系統融合的優勢,同時還保留了獨立處理器和FPGA方法的優點。

2019-09-26 07:59:27

大家好,我現在在畫一塊28335的板子,想實現與FPGA之間的通信,但是不知道該怎樣設計,包括FPGA與DSP連接的引腳、通過內部什么模塊實現數據通信,現在一頭霧水,請大家幫忙。謝謝。

2018-12-03 15:55:34

DSP和FPGA之間串口通信研究

2015-03-16 15:44:52

本帖最后由 mr.pengyongche 于 2013-4-30 03:24 編輯

通用微處理器具有良好的接口功能,便于構建可重構系統。按照MPU與FPGA之間的相互關系以及在系統中所起的作用,主要可以分為兩類:MPU控制FPGA工作的可重構系統和MPU協同FPGA工作的可重構系統

2011-05-27 10:29:16

原諒我記憶力不好。。。花了好久弄明白的東西才十個小時不到就忘記了,所以趁現在記得趕緊記錄下來。本文內容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

件的能力。邊界掃描可以在不使用物理測試探針的情況下測試引腳連接,并在器件正常工作的過程中捕獲運行數據。SoC FPGA作為在同一芯片上同時集成了FPGA和HPS的芯片,其JTAG下載和調試電路相較于單獨

2020-02-25 18:40:45

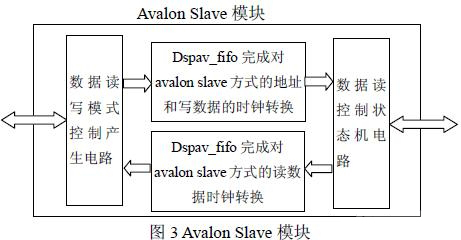

本文由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。Qsys系統和Linux應用程序之間通過一個名為hps_0.h的文件交互硬件信息,例如總線上添加

2020-02-16 18:41:59

\altera\hps\altera_hps\hwlib\include添加路徑D:\intelFPGA\17.1\embedded\ip\altera\hps\altera_hps\hwlib

2020-02-16 18:38:28

兩單板之間1000M網口之間對測,吞吐率只有300M,單板的連接結構博通61735-fpga-wan口,RGMII。

2017-09-18 18:03:59

由于Quartus?II15.0 Update 2及更早版本中的問題,用于將數據從HPS EMAC內核發送到FPGA內核的時鐘缺少時鐘分配。因此,這些HPS EMAC到FPGA路徑將不會進行時序分析。

2018-07-27 14:27:56

可預測性。這是由于FPGA是門級編程,并且CLB之間采用分布式互聯,而CPLD是邏輯塊級編程,并且其邏輯塊之間的互聯是集總式的。七,在編程方式上,CPLD主要是基于E2PROM或FLASH存儲器編程

2009-10-05 16:32:12

SEED-HPS6678(HPS6678)是北京艾睿合眾科技有限公司新推出的新一代高端DSP+FPGA應用方案。DSP采用TI公司首顆最高主頻為10GHz的8核浮點DSP芯片TMS320C6678

2019-09-24 08:29:12

1 CHI的片上互聯總線片上互聯是將SoC內部不同模塊連接起來的結構,如前文提到過的硬件系統結構中, Interconnect Bus就是片上互聯。需要支持模塊之間的高速數據傳輸,高效地互聯

2022-06-29 16:28:32

會有可編程的互連線、LABs內部的各個LEs內部之間也會有可編程的互連線、I/O塊與LABs之間、LABs與存儲塊以及乘法器之間都有著靈活可編程的互連線。圖3.21 LAB互聯結構 `

2017-11-21 22:28:24

如何在兩個FPGA之間通過GPIO口進行通信,不要使用RS232或是RS485接口,可否I告訴技術方案

2013-11-19 10:50:34

)、離散余弦變換(DCT)、小波變換、數字濾波器(有限脈沖響應(FIR)、無限脈沖響應(IIR)和自適應濾波器)以及數字上下變頻器。這些算法中,每一種都有一些結構性的元件可以用并行方法實現。而FPGA

2021-12-15 06:30:00

。以Altera的SoC為例, 簡單的說,該產品(芯片)由CPU,FPGA,以及連接他們的互聯部分(高速/輕量級)組成,如下圖所示,這樣的結構給開發需要同時用到CPU和FPGA產品提供了很大的便利。4.

2016-08-17 13:34:22

如何使用循環結構實現0~99之間所有偶數之和!

2016-04-15 22:33:55

”,而在SBBulkSourceSink固件中沒有顯示這個錯誤,可不可以證明我的FPGA和USB之間通信成功?另外,我該如何排查FPGA與USB之間的芯片通信問題?

2024-02-27 06:46:10

求arm和fpga之間SPI通信的源碼

2014-12-09 16:46:23

各位大神請問FPGA和arm互聯的硬件電路是怎么樣的啊,我想做到高速的數據交換,需要注意什么,還有電路中的總線驅動器是必須的嗎求原理圖,網上原理講很多,可是對我這種菜鳥不頂用

2022-04-28 10:16:13

));......reg [25:0] counter;regled_level;always @(posedge fpga_clk_50 or negedge hps_fpga_reset_n)beginif(~hps_fpga_reset_n)begin counter

2019-04-29 11:31:11

我們設計的系統里面需要實現DSP28377和ARM之間的高速互聯,目前擬定的方案有雙口RAM并行總線互聯和SPI總線互聯,請問還有其它高速總線互聯方式嗎?

2018-09-20 14:14:15

,有沒有相關的資料 ?通過網絡互聯的話 phy 到phy 之間直接連接可不可以 ?就是不使用網絡變壓器互聯?有沒有其他的和FPGA 互聯的方案以供參考 ?

2020-08-18 07:03:22

關于socfpga,還有個疑問: 1) 請問根據sopcinfo可以生成dts和dtb文件,而內核編譯也會生成dts和dtb文件,請問有什么區別啊, 2)我用quartus13.1,工程編譯后,有

2019-07-17 05:55:50

各位大神請問FPGA和arm互聯的硬件電路是怎么樣的啊,我想做到高速的數據交換,需要注意什么,還有電路中的總線驅動器是必須的嗎求原理圖,網上原理講很多,可是對我這種菜鳥不頂用

2022-06-07 15:53:01

大家好好,請問大家有用過FPGA+arm的架構嗎?本人現在做的一個項目就是關于FPGA+ARM用于視頻處理方面,但是不知道ARM和FPGA之間具體怎么工作,或是ARM負責給FPGA發送什么指令

2022-06-02 09:52:32

首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 本文討論了一種可在FPGA 上實現的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

16 The HPS3039 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co, ltd.Optimized Electrical design for 2-6W LED Application

2009-10-28 10:32:40 23

23 The HPS1014 series led driver is designed For Highvoltage led driver applicationOptimized Electrical design ,With active power factorcorection.

2009-11-07 11:41:26 16

16 The HPS1011 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-07 11:44:15 17

17 The HPS2007 series led driver is the new generation leddriver products of WeihawOptoelectronics Co

2009-11-07 11:48:18 19

19 The HPS1010 series is the new generation led driver products of Weihaw Optoelectronics Co

2009-11-10 14:38:40 19

19 The HPS2002 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:41:33 28

28 The HPS1011 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:43:12 13

13 The HPS1004 series led driver is the new generation leddriver products of Weihaw Optoelectronics Co

2009-11-10 14:46:37 20

20 HPS1007X HIGH PERFORMANCE LED POWER SUPPLY

Wide input & output voltage

2010-04-19 15:31:02 13

13 系統(HPS)來評估SoC的特性及性能。Intel Agilex? F系列FPGA開發套件提供了一個完整的設計環境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

基于FPGA實現DSP與RapidIO網絡互聯

1. 引言

隨著通訊系統的數據處理量日益增大,過去總線形式的體系結構逐漸成為約束處理能力進一步提升的瓶頸。本文首

2010-02-25 16:46:46 868

868

高級FPGA設計結構

2011-01-10 10:36:50 293

293 本文介紹了這種基于SRIO互聯技術的高速實時數據處理硬件平臺,并在該平臺上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術。

2012-01-10 15:07:55 3562

3562

SoC FPGA使用寬帶互聯干線鏈接,在FPGA架構中集成了基于ARM的硬核處理器系統(HPS),包括處理器、外設和存儲器接口。Cyclone V SoC FPGA在一個基于ARM的用戶可定制芯片系統(SoC)中集成了

2012-09-04 14:18:14 4604

4604

我經常收到關于各類設備之間的差異的問題,諸如ASIC、ASSP、SoC和FPGA之間的區別問題。例如是SoC是ASIC嗎?或ASIC是SoC嗎?ASIC和ASSP之間的區別是什么?以及高端FPGA應該歸類為SoC嗎?

2014-07-17 09:42:39 42262

42262 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 高級FPGA設計 結構、實現和優化,適合于FPGA的進階學習。

2016-05-11 16:40:55 15

15 高級FPGA設計 結構、實現和優化,適合于學習FPGA的進階學習。

2016-05-11 16:40:55 14

14 引入IP核的三維FPGA結構研

2017-01-07 20:32:20 2

2 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2487

2487

HPS型頂導向高壓單座調節閥是為高溫、高壓工況而設計的。閥體結構緊湊,流體通道呈S 流線型,壓降損失小,允許流通能力大,可調范圍廣。閥芯導向部分的導向面積大,具有抗振性能強的特點。閥座關閉性能符合

2017-09-25 11:17:59 8

8 SoC使用寬帶互聯干線鏈接,在FPGA架構中集成了基于ARM的硬核處理器系統(HPS),包括雙核ARM。處理器、外設和存儲器控制器。

2018-03-22 13:34:21 7

7 本文首先分析了FPGA是否會取代DSP,其次介紹了FPAG結構特點與優勢及DSP的基本結構和特征,最后闡述了FPGA與DSP兩者之間的區別。

2018-05-31 09:51:25 35711

35711

如何在預加載器中調試HPS SDRAM

2018-06-20 00:44:00 3023

3023

霍尼韋爾過程控制部 (HPS) 近日發布一款新型天然氣計量解決方案,為運營、維護和管理團隊提供簡單易用的中游計量系統狀態監控功能。霍尼韋爾互聯工廠天然氣計量IQ解決方案有助于提高計量的可靠性和安全性,同時大幅減少現場檢修需求,從而削減運營成本。

2018-07-09 10:55:00 2030

2030 小梅哥最新款FPGA_SOC

2019-09-02 06:02:00 2139

2139

目前市場上90%以上的FPGA來自于xilinx和altera這兩家巨頭,而這兩家FPGA的實現技術都是基于SRAM的可編程技術,FPGA內部結構基本一致,所以本文僅以xilinx的7系列FPGA介紹。

2019-10-20 09:03:00 2380

2380

電子技術行業里面的攻城師們應該對ASIC、FPGA和單片機這些名字都不陌生,但我相信并不是所有人都清楚ASIC和FPGA之間的區別和關系,下面我們分幾個方面去理清一下他們之間的瓜葛糾紛吧!

2020-06-04 11:36:11 5697

5697 對于FPGA的學習者而言,怎樣學習FPGA是大家爭論不斷的。有的認為要先學習語言,也就是HDL硬件描述語言;也有的說要先學習數電、模電,沒有這些知識,就算學會了語言,以后的學習也會非常艱難。但是唯一大家都認可的是掌握FPGA的基本結構。

2020-06-01 09:07:18 12050

12050 簡單介紹了FPGA器件的發展及基本結構、設計方法,并以PWM電路的FPGA實現為例,說明了FPGA在電力系統中的應用前景.

2020-10-20 16:16:50 11

11 1.項目需求 FPGA :V7-690T兩片 Resource:兩片FPGA通過X12 gth互聯;每片FPGA使用48路serdes走光口與板外連接;每片FPGA使用SIROx4通過VPX與外界

2021-01-07 10:15:31 4645

4645

1、兩塊fpga 之間采用12 根線連接,包括8 根數據線, 2 根同步時鐘線, 2 根使能信號線。

2021-02-25 09:58:00 44

44 最近完成了Arria10的原理圖設計,想做一些記錄,下面是關于FPGA配置的一些方式。 MSEL 將 MSEL 管腳直接連接到VCCPGM 或 GND,不需使用任何的上拉或下拉電阻,即可選擇出所需

2021-03-12 16:26:58 11307

11307

兩塊fpga之間采用12根線連接,包括8根數據線,2根同步時鐘線,2根使能信號線。

2021-04-27 09:35:16 13

13 FPGA各存儲器之間的關系(嵌入式開發工作怎么樣)-該文檔為FPGA各存儲器之間的關系總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 16:35:09 6

6 根據國際電信聯盟(ITU)的定義,物聯網主要解決物品與物品,人與物品,人與人之間的互聯。因為互聯網并沒有考慮到對于任何物品連接的問題,所以我們就使用物聯網來解決傳統意義上的問題。

2021-09-21 17:17:00 8263

8263 設計屬硬件范疇,它的硬件(FPGA)是可編程的,是一個通過硬件描述語言在FPGA芯片上自定義集成電路的過程;二者最大的區別:單片機(無論哈佛總線結構或者馮諾依曼結構)均為取出指令->執行,指令是順序執行的(即使是中斷,其發生后的中斷服務程序也

2021-11-15 16:51:06 24

24 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 2592

2592 系統架構確定,下一步就是FPGA與各組成器件之間互聯的問題了。通常來說,CPU和FPGA的互聯接口,主要取決兩個要素。

2022-10-08 11:37:08 1749

1749 全新英特爾 Agilex D 系列 FPGA 和 SoC 具備多項新特性,例如升級版硬核處理器系統 (HPS)、采用 AI 張量模塊的增強型數字信號處理 (DSP)、MIPI I/O 支持和固核 IP 時間敏感網絡 (TSN) 控制器。

2022-11-23 15:23:35 507

507

電子發燒友App

電子發燒友App

評論