PCIE(PCI express)是用來互聯諸如計算機和通信平臺應用中外圍設備的第三代高性能I/0總線。PCIE體系結構繼承了第二代

2010-10-08 10:19:41 1894

1894

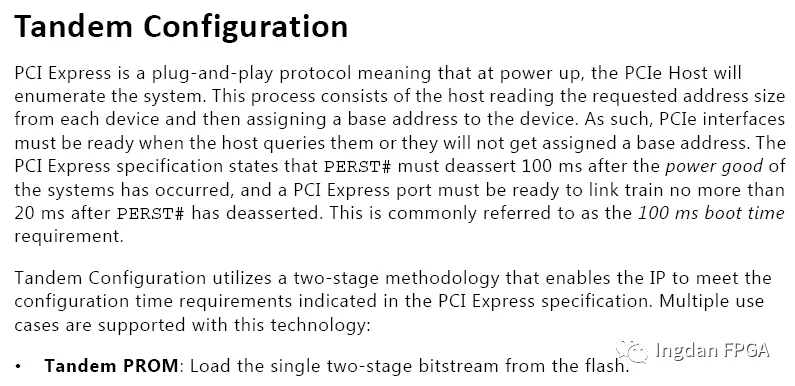

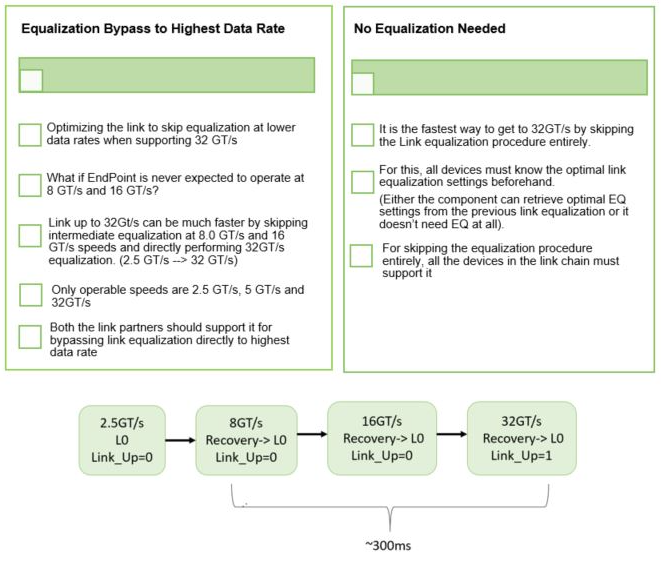

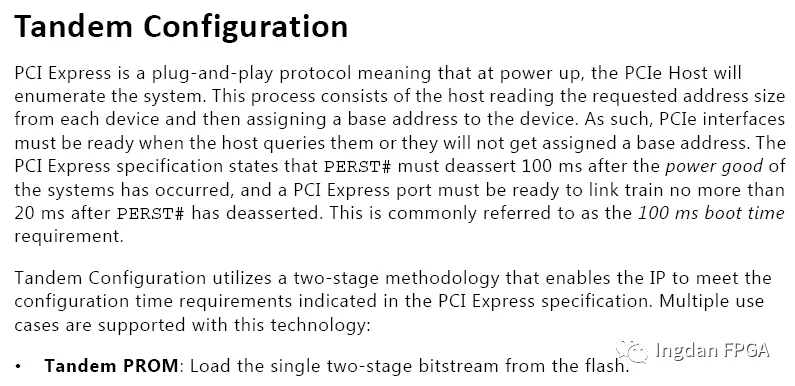

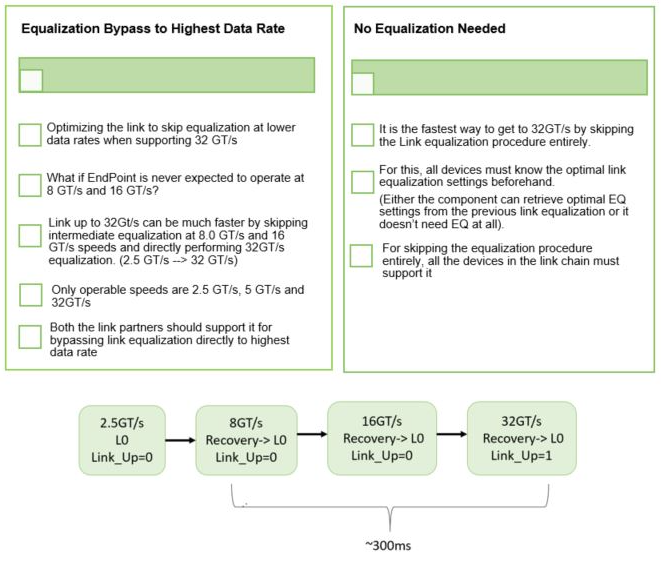

現在大規模FPGA的bitstream比較大導致板卡從上電到FPGA配置完成的時間遠遠超過100MS的要求,從而電腦端無法正常識別到PCIE設備。為此Xilinx的PCIE Tandem功能是專為滿足PCIe設備在100ms之內枚舉起來要求而設計的。

2022-08-02 08:03:43 2455

2455

嗨,我正在嘗試使用KC705板進行PCIE RC和端點測試。1)我將把PCIE RC控制器IP設計和FPGA PCIE PHY放在FPGA中。2)我將在FPGA中放置另一個PCIE端點控制器IP

2020-07-26 13:06:25

您好,

TMDXEVM6678 評估板+ pcie 轉接卡,評估板開關撥至pcie啟動,插在不同的主機,發現有的型號電腦能檢測到設備,有些型號電腦無法檢測到設備。請問我該修改哪些寄存器配置讓無法檢測到設備的主機能夠檢測到設備。是否有相關的寄存器適應不同類型主機?

謝謝

2018-06-21 07:45:09

6678的pcie和fpga的pcie? TX和RX需要交叉接么?DSP的TX接到FPGA的rx,DSP的RX接到FPGA的TX?

?

2018-06-21 15:49:12

、PCIeX163、支持半長卡和全長卡4、4U 19英寸的標準機架式機箱 二、應用場景:1、基于GPU的高性能并行計算節點2、FPGA計算加速擴展3、高性能3D圖形圖像渲染系統4、Pcie 總線和設備外擴展

2017-07-13 17:19:15

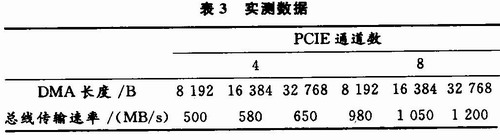

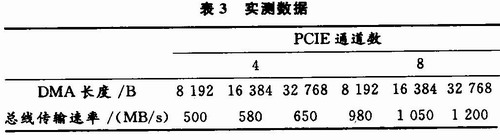

開發環境:windows開發平臺:QT5.11.31.PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2019-12-26 10:27:19

開發環境:windows開發平臺:QT5.11.31、PCIE上位機測試過程FPGA將數據傳到芯片中,通過pcie再將芯片算完的數傳給上位機。目標:1.實現上位機的速度測試,經測試pcie的傳輸速度

2022-01-13 16:44:54

`PCIE總線的FPGA設計方法`

2015-10-30 14:30:52

PCIe-9110IM 是一款兼容 PCI Express r1.0a 規范的單 CAN 口 PCIe-CAN 通訊接口卡。PCIe-9110IM 接口卡支持 PCI Express 多功能設備外圍

2022-10-31 06:11:43

在DSP上運行的代碼量很大,過程繁瑣。

請問有沒有方法將DSP程序直接在DSP上自啟動,不需要通過Host? PC發送。我想是否能實現板卡能通過PCIe模式啟動時,自動加載flash中的DSP程序??

當然只要有方法能滿足 將DSP中的數據通過PCIE傳輸至Host? PC即可!

多謝大家!

2018-06-19 05:08:19

x86處理器如何處理MSI-X中斷請求PCIe設備發出MSI-X中斷請求的方法與發出MSI中斷請求的方法類似,都是向Message Address所在的地址寫Message Data字段包...

2022-02-16 06:36:23

的主動狀態電源管理(ASPM)。一般來說,無論是系統驅動端硬件(RC)還是設備硬件(EP)都可以通過檢測pcie鏈路上的空閑時間,然后啟動電源狀態轉移。有兩種低功率鏈路狀態:L0s,也叫L0

2021-12-28 06:18:35

的主動狀態電源管理(ASPM)。一般來說,無論是系統驅動端硬件(RC)還是設備硬件(EP)都可以通過檢測pcie鏈路上的空閑時間,然后啟動電源狀態轉移。有兩種低功率鏈路狀態:L0s,也叫L0 st...

2022-01-03 08:00:09

embededendpoint(這種設備對外不出PCIe接口)。這么多的設備,CPU啟動后要怎么去找到并認出它們呢?Host對PCIe設備掃描是采用了深度優先算法,其過程簡要來說是對每一個可能的分支路徑深入到

2021-05-25 09:22:48

大佬們通過pcie延長線連接主板pcie插槽和板子上的金手指pcie代碼燒到板子里重啟電腦了但設備管理器其他設備沒出現PCI內存控制器是什么原因呀救救孩子

2023-05-22 09:49:27

Hi ?各位管理好

咨詢下,我使用STK 6657 中的 PCIE_test 例程進行PCIE通信測試, 6657作為RC端口, pcie外接設備

在代碼中有

2018-06-21 18:49:04

獨有的一些Capability結構。PCIe總線規范要求其設備必須支持Capabilities結構。在PCIe總線的基本配置空間中,包含一個Capabilities Pointer寄存器,上圖的0x34

2022-08-16 15:45:06

嗨論壇,我們在我們自己的載板上使用 Variscite 的 i.MX7D SoM。模塊上的 SoC 無法啟動,因為我們的板子沒有 100 MHz外部 PCIe 參考時鐘,并且內核掛起并顯示以下

2023-04-23 08:03:17

我在LS1043A開發板上J12接口接上pcie接口設備,系統啟動后,執行lspci,沒有知道設備被識別請問這是什么問題?需要怎么配置?謝謝

2022-01-05 06:49:29

RK3588的PCIE設置為EP模式設備樹和defconfig需要怎么修改呀?

2023-04-21 11:16:59

插入機箱時能夠查到PCIE設備,但是不使用擴展板,直接將插針式連接器插入機箱則無法識別。想問一下是耦合電容的問題嗎,或者其他什么原因?

pcie連接器原理圖如下

2023-05-16 11:07:40

參考。1.“使用出廠鏡像啟動時發現無法正常啟動”問題描述——客戶自制底板去掉PCIe燒錄出廠鏡像,啟動時出現的卡死信息:?編輯切換為居中添加圖片注釋,不超過 140 字(可選)產生原因——PCIe

2022-09-15 17:04:06

參考。1.“使用出廠鏡像啟動時發現無法正常啟動”問題描述——客戶自制底板去掉PCIe燒錄出廠鏡像,啟動時出現的卡死信息:?編輯切換為居中添加圖片注釋,不超過 140 字(可選)產生原因——PCIe

2022-08-20 14:18:43

/class/pci_epc 中使用 pcie 端點控制器,并在根復合體端 (x86) 上使用 lspci 和 pcitest 測試接口。

問題是,PCIe端點控制器設備不存在(/sys/class

2023-06-09 08:23:25

FPGA實現 PCIE 端點設備,我該如何實現這樣一個功能,PC發送一條消息(比如一個存儲器寫事務),然后FPGA用戶邏輯獲得這個事務包里的內容進行相關操作,比如把一個LED點亮。已知在設計例程中

2016-03-12 10:48:22

實際上有時會出現日志下的問題

但是現在,當我嘗試啟動時,問題總是出現。

是什么原因 ??

bsp: binaries_auto_linux_bsp28.0_s32g274

U-Boot

2023-05-06 08:10:59

求教:應用環境:主機:x86型CPU主板操作系統:win xp設備:IDT生產的PCIE-SRIO橋片 TSI721總線:PCIE 2.0問題描述:1、windows啟動后,用windriver

2015-12-13 11:30:32

項目名稱:FPGA PCIe信號拆分應用領域:計算機參賽計劃:利用FPGA的并行資源,實現在不使用plx硬核芯片的情況下對PCIe信號的拆分。具體有效帶寬視開發板資源而定。使用FPGA相較于使用硬核

2021-05-12 18:05:46

,那就很容易把pcie協議理解徹透徹,當然這里狹義指的是上層交互的TLP協議,數據鏈路層和物理層更復雜的事情是硬核做的,用起來PCIE并不需要深入了解。

如何使用紫光PCIE,首先FPGA端需要一個

2023-11-17 14:35:30

嗨,PCIe-Spec定義在穩定供電后100ms,PCIe設備必須為鏈路訓練做好準備。使用7系列Zynq設備無法達到此時間。我使用了兩種方法來減少啟動時間: - 優化FSBL以達到SPI控制器的最大

2020-06-09 16:42:15

小弟最近在研究PCIE的系統結構。有一點想不明白。如果一個CPU外掛一個系統內存DDR,同時一片FPGA通過PCIE接口連接CPU,CPU做為Host主橋,FPGA做為PCIE設備。那么根據PCIE

2016-04-06 16:24:36

剛接觸PCIe,想用PCIe口與PC通信,EP模式。把板子插到PC上之后,通過windriver能查看到TI設備,但是用PCItree不能看到,這樣正常嗎?我運行的程序

2018-08-07 08:28:19

本人想問下,FPGA的介紹中有些事說帶有PCIe硬核的,那么這個FPGA直接購買后就可以使用這個硬核完成PCIE功能了嗎?不再需要購買其他什么許可文件之類的東西了嗎? 這點不是很清楚,順便問一下帶有這中硬核的FPGA大概要多少錢呢?

2012-12-12 17:52:08

FPGA pcie dma測試

流程:金手指和電腦連接之后,先加載程序,pc重啟;

現象:pc無法開機。

FPGA pcie x8,pc x16,直接連接上去的

請問這是什么情況呀,為什么電腦開不了機呢?

2023-09-13 18:21:28

我們可以將多個 PCIe 設備 (IC) 連接到一般的單個 PCIe 控制器(在我們的案例中更具體地說是 NXP LS20xxA 處理器)嗎?

例如,將四個不同的 PCIe x1 設備 (IC

2023-05-05 07:35:41

個PCIE SSD+1個級聯擴展,是穩定、高性能的PCIe擴展基礎設備。 基于12槽PCIE擴展塢知識資料.zip [/tr]

2018-07-09 09:24:53

PCIe是什么?有什么核心優勢?Xilinx的PCIe端點模塊的顯著優勢包括哪些?基于Virtex-5 LXT FPGA的PCIe端點該怎樣去設計?

2021-05-26 06:39:11

PCIe總線通信過程是怎樣的?是什么原理?如何利用PCIe DMA總線實現一個基于FPGA的PCIe 8位數據采集卡?

2021-09-17 07:16:03

嗨,我正在使用超大規模的FPGA板。我可以通過DMA子系統IP和DDR控制器IP將數據從PC傳輸到DDR。我打算在FPGA中進行一些處理,然后更新數據,以便PC可以讀取。如何通過PCIe指示PC處理

2020-05-08 09:40:04

了主機枚舉PCIE設備的時間。通過測試,LSSM_STATE!=0x11的時間要比PCIEXpress_PM_INT中斷早,差不多早200us左右。為什么會出現上述情況呢?硬件情況如下:2個dsp 6670通過PCIE switch與主機相連。

2018-06-25 03:06:56

需求:兩塊fpga互聯,兩塊fpga分別模擬成特定的pcie設備,兩個設備通過serdes總線互聯通信,fpga僅僅只要模擬特定的設備就可以,不需要負載的邏輯,提供簡單的讀寫,dma,中斷等功能。高價尋高手,請各位多幫忙啊。

2019-02-11 15:31:02

我有一個問題,我必須在使用JTAG將位文件下載到FPGA后重新啟動計算機。否則,我無法使用PCIE讀取寄存器或與PCIE接口有關的任何內容。我該怎么做才能改善我的情況?謝謝。

2020-06-02 15:56:26

Xilinx生成的PCIE核(如xapp1052),如果要使用的話,是必須要自己用C語言編寫控制程序么?對于EDK的PCIE工程(xapp1030),應該在SDK中編寫C驅動就行了吧,還是說也需要另外編寫應用程序? 以上是一些關于PCIE我拿不準的地方,希望大家能夠抽時間看看,給我一些提點,謝謝!!!

2015-06-25 19:21:35

并不理想。本文將討論如何使用一個多點信號來分配PCIe時鐘,而且仍滿足PCIe第二代規范嚴格的抖動要求。

2019-09-26 07:56:41

我很想學習WDM PCIE驅動開發,但是我沒有PCIE設備,請問有什么推薦的呢?求前輩指點迷津!!!

2022-09-30 07:43:20

我配置了一個PCIe端點示例設計,但是我在bitfile編程后找不到Ubuntu中的PCIe設備。任何人都有ZCU106的示例設計?非常感謝!

2019-10-21 09:18:09

參考。1.“使用出廠鏡像啟動時發現無法正常啟動”問題描述——客戶自制底板去掉PCIe燒錄出廠鏡像,啟動時出現的卡死信息:產生原因——PCIe影響了啟動,需要在設備樹里把跟PCIe有關的功能關閉

2022-08-20 13:48:33

將這兩塊板卡插入主機PCIE Switch,通過主機CPU驅動程序對兩塊PCIE設備進行配置,實現兩個設備的聯通,可以將USB3.0讀入的數據搬到FPGA的RAM里。這種方案可行嗎?2.直接用PCIE Cable將兩設備連接,FPGA直接對PCIE轉USB3.0板卡進行控制。這個方案可行嗎?求高人指點,謝謝!

2014-12-25 22:54:58

30_AVDD_0V9 和 PCIE30_AVDD_1V8 電壓是否滿足要求。硬件上不使用PCIekernel 的 dts 里把 PCIe disabled。&pcie30phy {status = "

2022-06-07 11:34:55

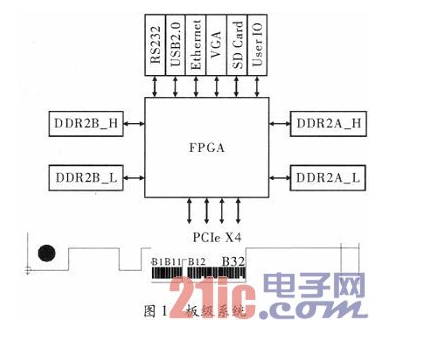

,AD采集到的數據需要經過接口轉換層、FPGA的PCIeIP核、PCIe總線等才能到達計算機IO內存空間。完成內存地址映射后,用戶程序就可以從該內存讀取數據,進行數據處理。在實際多線程的數據傳輸中,還會

2018-11-08 16:22:22

嗨,我將從一個新項目開始。它涉及使用FPGA和GP / GPU加速PCIe板,這些板將被添加到常規計算機或服務器中。 GPU將是NVIDIA特斯拉。 FPGA板......還有待選擇。我確實看到了

2019-01-24 10:55:48

PCIe規范定義了3種類型的AtomicOps事務:“AtomicOps的架構適用于設備到主機,設備到設備和主機到設備的交易。”如果英特爾?至強?處理器可擴展系列支持Pcie AtomicOps主機

2018-10-15 11:23:49

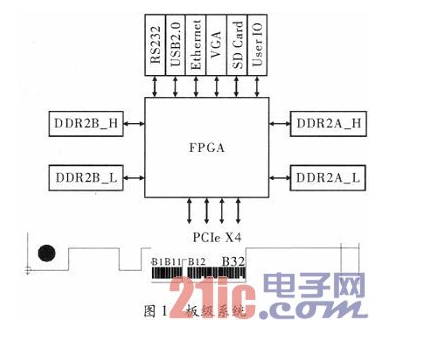

系列FPGA實現PCIe接口所涉及的硬件板卡參數、應用層系統方案、DMA仲裁、PCIe硬核配置與讀寫時序等內容。

2019-05-21 09:12:26

在用FPGA開始一個PCIe系統設計,你需要了解PCIe規范、核心和鏈接,終端設備的設計考慮。

2010-12-14 15:06:47 0

0 所有的PCIe SSD在很大程度上看起來都是一樣的,那么用戶如何才能選擇出滿足他們需求的合適的PCIe SSD呢?

2011-12-22 14:17:12 5966

5966 PCIE總線基本資料 與PCI總線不同,PCIe總線使用端到端的連接方式,在一條PCIe鏈路的兩端只能各連接一個設備,這兩個設備互為是數據發送端和數據接收端。PCIe總線除了總線鏈路外,還具

2012-05-10 14:45:47 0

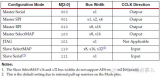

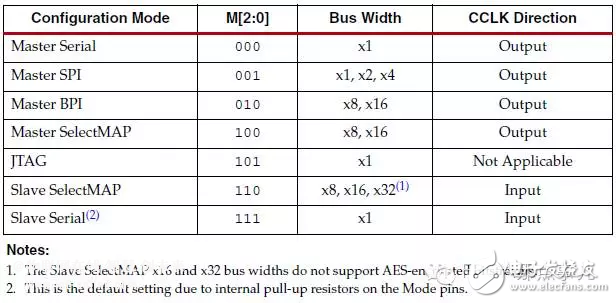

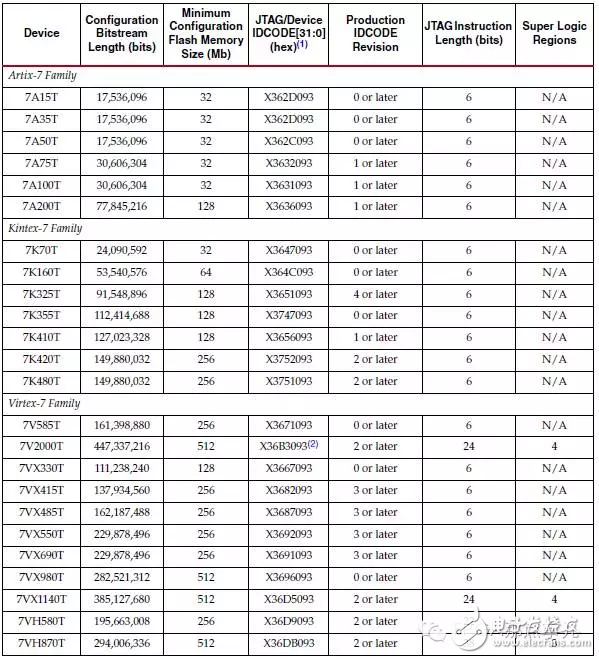

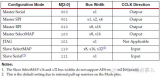

0 的PCIe設備,需要reboot服務器。眾所周知,FPGA芯片規模越來越大,那么如何做才能滿足PCIe設備的啟動時間的要求呢? 7系列FPGA常見的配置模式如下圖所示: SelectMAP和Master

2017-02-07 20:55:41 2914

2914

設備間,其是一種基于數據包、串行、點對點的互連,因此所連接設備獨享通道帶寬。根據使用的版本號和通道數,其性能具有可擴展性。對于PCIe 2.0,每條通道在每個方向上的數據傳輸速率是5.0 Gbits-1。從PCIe1~PCIe16,能滿足一定時間內出現的低速設備和高速設備的需求

2017-10-13 10:41:03 24

24 的不同。在兩個設備間,其是一種基于數據包、串行、點對點的互連,因此所連接設備獨享通道帶寬。根據使用的版本號和通道數,其性能具有可擴展性。對于PCIe 2.0,每條通道在每個方向上的數據傳輸速率是5.0 Gbit·s-1。從PCIe×1~PCIe×16,能滿足一定時間內出現的低速設備和高速設備的需求。

2018-10-30 17:18:59 6237

6237

了解如何使用Vivado在設備啟動時及其周??圍進行調試。

你也會學習

使用Vivado 2014.1中引入的Trigger at Startup功能來配置和預先安裝a

調試核心并觸發設備啟動時或周圍的事件......

2018-11-22 07:05:00 4084

4084 該信號為全局復位信號,由處理器系統提供(RC),處理器系統需要為PCIe插槽和PCIe設備提供該復位信號。PCIe設備使用該信號復位內部邏輯。當該信號有效時,PCIe設備將進行復位操作。

2018-12-22 14:45:41 22377

22377 設備對外不出PCIe接口)。這么多的設備,CPU啟動后要怎么去找到并認出它們呢? Host對PCIe設備掃描是采用了深度優先算法,其過程簡要來說是對每一個可能的分支路徑深入到不能再深入為止,而且每個節點

2019-03-11 15:28:53 18226

18226

,M-PCIe ECN主要的改動在物理層,通過引入M-PHY,旨在獲得更低的功耗以適應嵌入式設備的低功耗要求。 M-PCIe的主要特性如下: M-PCIe的上層協議層、事務層(TL)、數據鏈

2020-11-24 14:51:48 6997

6997 FPGA的bitstream比較大導致板卡從上電到FPGA配置完成的時間遠遠超過100MS的要求,從而電腦端無法正常識別到PCIE設備。 為此Xilinx的PCIE Tandem(詳見PG156)功能

2021-06-18 14:57:17 3064

3064 1?簡介本章包含的話題有啟動時間的測量、分析、人因工程(human factors)、初始化技術和優化技巧等。產品花在啟動方面的時間直接影響終端用戶對該產品的第一印象。一個消費電子設備不管

2021-11-01 16:31:55 13

13 ”,簡寫PCIe。2、AC耦合電容:高速差分信號電氣規范要求PCIe發送端串聯一個電容,進行耦合。3、鏈路類型與差分信號數量:X1:1對時鐘差分信號,1對收發差分信號,單面pin數18pi...

2021-11-06 17:51:01 57

57 的主動狀態電源管理(ASPM)。一般來說,無論是系統驅動端硬件(RC)還是設備硬件(EP)都可以通過檢測pcie鏈路上的空閑時間,然后啟動電源狀態轉移。有兩種低功率鏈路狀態:L0s,也叫L0

2022-01-06 12:43:37 2

2 的主動狀態電源管理(ASPM)。一般來說,無論是系統驅動端硬件(RC)還是設備硬件(EP)都可以通過檢測pcie鏈路上的空閑時間,然后啟動電源狀態轉移。有兩種低功率鏈路狀態:L0s,也叫L0 st...

2022-01-11 15:31:46 1

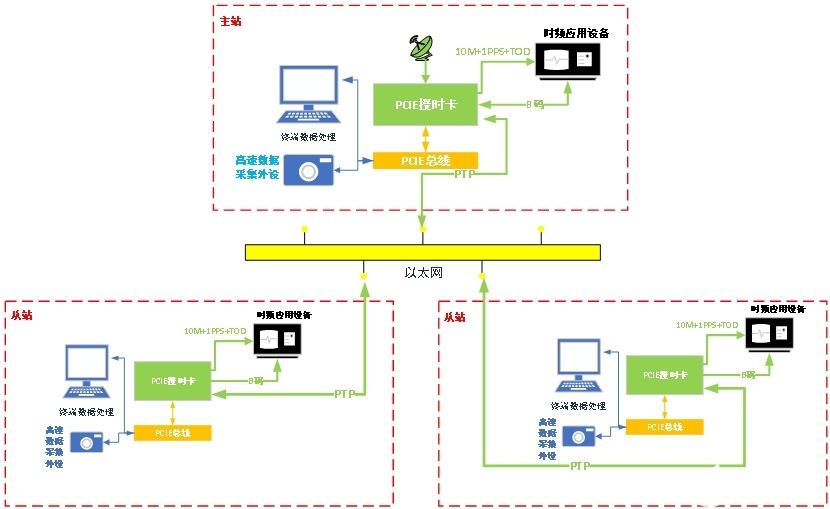

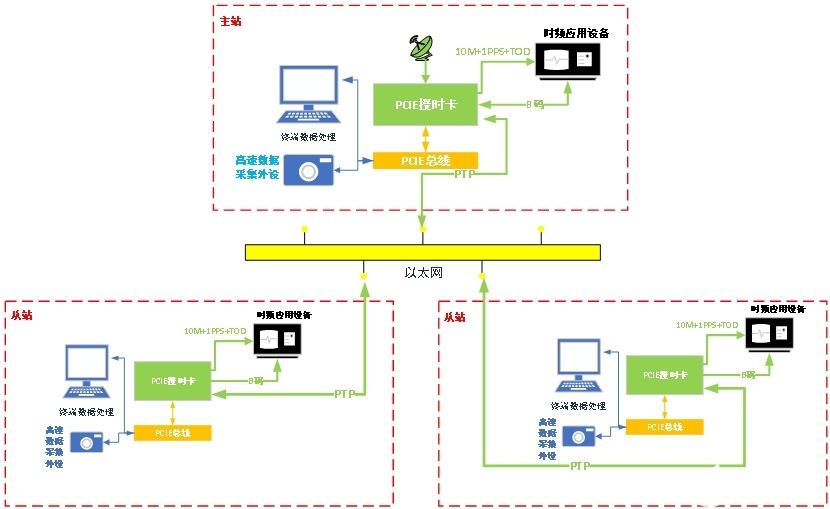

1 PCIe授時卡作為擁有獨立系統的板卡類授時設備,具有安裝簡單、適配性強、時間精度高、信號穩定等優點,可以高效便捷地滿足行業對高精度時間同步系統的要求。

2022-08-25 13:09:15 1703

1703

電子發燒友網站提供《PCIe 9110IM PCIe總線轉CAN設備手冊.pdf》資料免費下載

2022-10-17 10:59:17 1

1 硬盤是大家都很熟悉的設備,一路走來,從HDD到SSD,從SATA到NVMe,作為NVMe SSD的前端接口,PCIe再次進入我們的視野。作為x86體系關鍵的一環,PCIe標準歷經PCI,PCI-X

2022-12-09 10:04:35 3268

3268 PCIe 是用于點對點通信的高速差分串行標準。每一代 PCIe 標準都提供比上一代產品更多的功能和更快的數據傳輸速率。最新一代 PCIe 5.0 將使 PCIe 4.0 的吞吐率翻倍。PCIe

2023-05-26 10:23:14 1133

1133

AMD FPGA自帶PCIE硬核,實現了PCIE協議,把串行數據轉換為并行的用戶數據

2023-07-14 15:53:40 878

878

訪問 PCI/PCIe 設備的流程 PCI/PCIe 設備的配置信息 PCI/PCIe 設備上有配置空間(配置寄存器),用來表明自己"需要多大的地址空間"。 注意,這是 PCI/PCIe 地址空間

2023-07-30 09:44:54 942

942 本文介紹一個FPGA 開源項目:PCIE I/O控制卡。上一篇文章《FPGA優質開源項目– PCIE通信》開源了基于FPGA的PCIE通信Vivado工程,用于實現上位機通過PCIE接口訪問FPGA的DDR3以及RAM內存數據。PCIE I/O控制卡工程是在上一個工程的基礎上進行了部分模塊和參數的修改。

2023-09-01 16:18:36 1296

1296

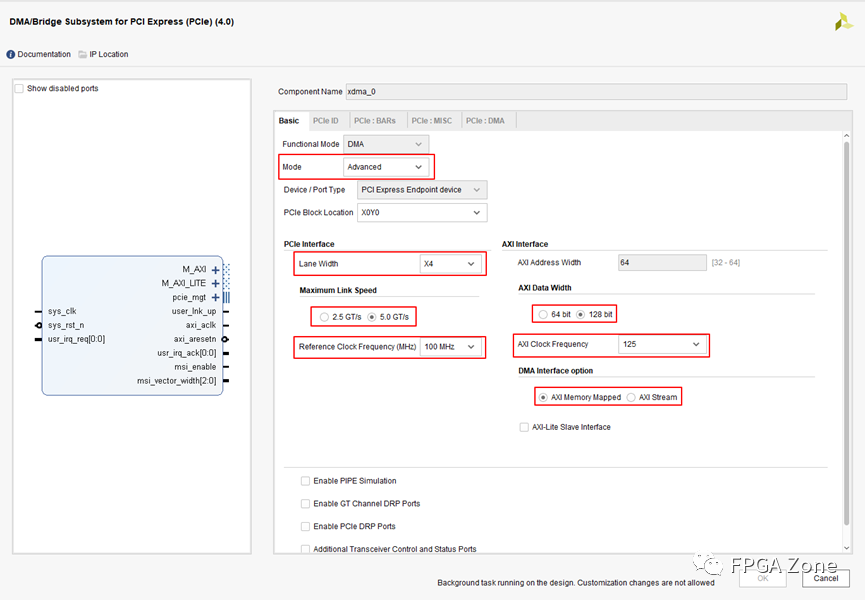

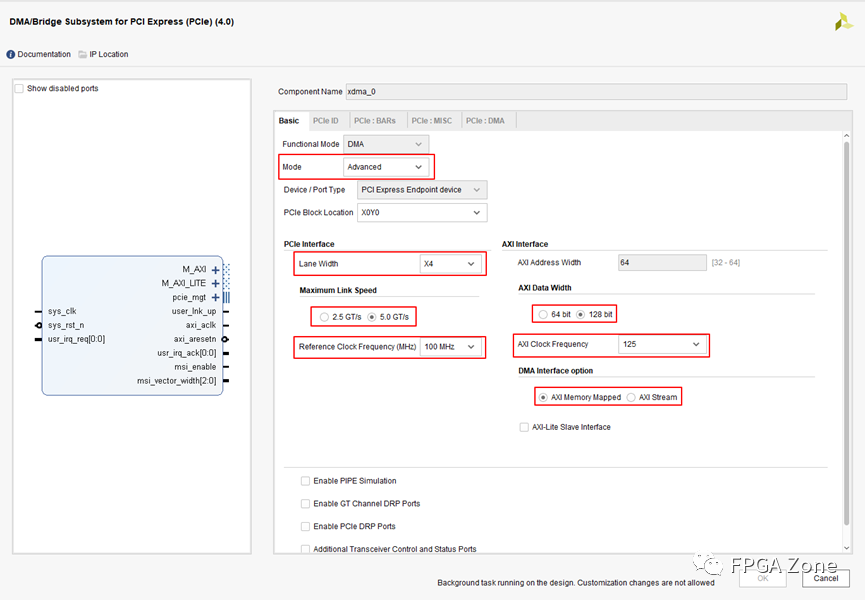

本文介紹一個FPGA開源項目:PCIE通信。該工程圍繞Vivado軟件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的開源驅動程序,可在Windows系統或者Linux系統下使用,因此采用XDMA IP進行PCIE通信是比較簡單直接的。

2023-09-04 16:45:54 1142

1142

,PCIe標準幾經迭代。PCIe最初作為一種串行接口引入,用于替代眾多主板架構使用的并行總線, 但PCIe擁有一項獨特特性:通道數量可從1個擴展至32個。 借助這一并行總線特性,PCIe兼容設備之間可以根據數據傳輸要求,建立寬度為1個、2個、4個、8個、16個甚至高達32個通道的鏈路

2023-11-30 12:15:01 311

311

隨著PCIE版本的不斷升級,其應用范圍也越來越廣泛。除了傳統的顯卡、網卡、聲卡等設備外,SSD、USB控制器、Thunderbolt接口等設備也開始支持PCIE接口。

2024-01-21 10:25:10 577

577 開關電源啟動時間測試是指打開電源后,測試電源輸出電壓開始變化到恢復穩定的這段時間。啟動時間測試用來評估開關電源的啟動性能。在一些需要快速響應的設備中,如果電源啟動時間過長,可能會導致設備無法及時響應,影響使用體驗。

2024-01-22 16:25:18 223

223 一種計算機總線技術,用于連接外圍設備和主板,提供快速的數據傳輸速度。 PCIe有廣泛的應用,包括用于擴展卡、顯卡、網卡等外部設備的連接。與傳統的PCI總

2024-01-30 16:09:25 503

503 Transaction Layer的所有功能特性,不僅內置DMA控制器,而且具備AXI4用戶接口,提供一個高性能,易于使用,可定制化的PCIe-AXI互連解決方案,同時適用于ASIC和FPGA。

2024-02-21 15:15:03 144

144

正在加载...

電子發燒友App

電子發燒友App

評論