FIR濾波器在信號(hào)處理和通信系統(tǒng)中有著極為廣泛的應(yīng)用,全稱(chēng)是有限長(zhǎng)單位沖擊響應(yīng)濾波器。

2023-06-15 15:12:13 2180

2180

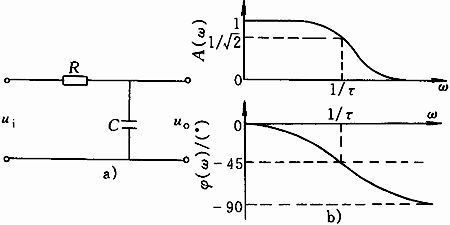

濾波器使用反饋,因此當(dāng)信號(hào)輸入后,輸出是根據(jù)算法循環(huán)的。 5、 FIR濾波器與IIR濾波器比較,每一種都有優(yōu)缺點(diǎn),但總得來(lái)說(shuō), FIR濾波器的優(yōu)點(diǎn)遠(yuǎn)大于缺點(diǎn),因此在實(shí)際運(yùn)用中,FIR濾波器比IIR

2011-09-24 16:05:53

穩(wěn)定。另外,在這種結(jié)構(gòu)中,由于運(yùn)算過(guò)程中對(duì)序列的舍入處理,這種有限字長(zhǎng)效應(yīng)有時(shí)會(huì)引入寄生振蕩。相反,FIR濾波器主要采用非遞歸結(jié)構(gòu),不論在理論上還是在實(shí)際的有限精度運(yùn)算中都不存在穩(wěn)定性問(wèn)題,運(yùn)算誤差也較小。此外,FIR濾波器可以采用快速傅里葉變換算法,在相同階數(shù)的條件下,運(yùn)算速度可以快得多。

2016-08-08 08:49:32

,在這種結(jié)構(gòu)中,由于運(yùn)算過(guò)程中對(duì)序列的舍入處理,這種有限字長(zhǎng)效應(yīng)有時(shí)會(huì)引入寄生振蕩。相反,FIR濾波器主要采用非遞歸結(jié)構(gòu),不論在理論上還是在實(shí)際的有限精度運(yùn)算中都不存在穩(wěn)定性問(wèn)題,運(yùn)算誤差也較小。此外,FIR濾波器可以采用快速付里葉變換算法,在相同階數(shù)的條件下,運(yùn)算速度可以快得多。

2018-03-12 13:21:07

考慮來(lái)加以選擇。從使用要求上來(lái)看,在對(duì)相位要求不敏感的場(chǎng)合,如語(yǔ)言通信等,選用IIR較為合適,這樣可以充分發(fā)揮其經(jīng)濟(jì)高效的特點(diǎn);對(duì)于圖像信號(hào)處理,數(shù)據(jù)傳輸?shù)纫圆ㄐ螖y帶信息的系統(tǒng),則對(duì)線性相位要求較高,采用FIR濾波器較好。當(dāng)然,在實(shí)際應(yīng)用中可能還要考慮更多方面的因素。

2019-06-27 04:20:31

我在長(zhǎng)度為2500的信號(hào)上執(zhí)行46階FIR低通濾波器;在16 MIPS下使用PIC24FJ256GB206。所有的值都是浮動(dòng)的。使用該鏈路實(shí)現(xiàn)算法。目前,正在執(zhí)行2.76秒來(lái)執(zhí)行對(duì)我的應(yīng)用程序不可

2019-10-17 06:28:21

FIR濾波器的實(shí)現(xiàn)方法有哪幾種?基于Verilog HDL的FIR數(shù)字濾波器設(shè)計(jì)與仿真

2021-04-09 06:02:50

;FIR 濾波器的系統(tǒng)函數(shù)為多項(xiàng)式;FIR 濾波器具有線性相位。實(shí)現(xiàn)同樣參數(shù)的濾波器,FIR比IIR需要的階數(shù)高,因此計(jì)算量大。目前,FIR 數(shù)字濾波器的設(shè)計(jì)方法主要是建立在對(duì)理想濾波器頻率特性做某種近似的基礎(chǔ)上。設(shè)計(jì)方法有窗函數(shù)法,等波紋設(shè)計(jì)法(Equiripple)和最小二乘法 (Least

2021-08-17 06:19:17

本文講解FIR濾波器的幅度特性,再理論聯(lián)系實(shí)際的看看FIR濾波器到底長(zhǎng)什么樣?有什么用?聽(tīng)我慢慢道來(lái)。在MATLAB函數(shù)中,有FIR1和FIR2函數(shù),前者是用于處理一維數(shù)組,后者是用于二維數(shù)組的處理

2021-08-08 07:00:00

對(duì)于fir濾波器,已經(jīng)在前面的文章中記錄了仿制DIY&關(guān)于MATLAB中濾波器設(shè)計(jì)工具的使用心得記錄),其設(shè)計(jì)和實(shí)現(xiàn)都非常簡(jiǎn)單。如果在嵌入式系統(tǒng)中可以滿(mǎn)足且有必要實(shí)時(shí)iir運(yùn)算,那么

2021-12-22 08:29:40

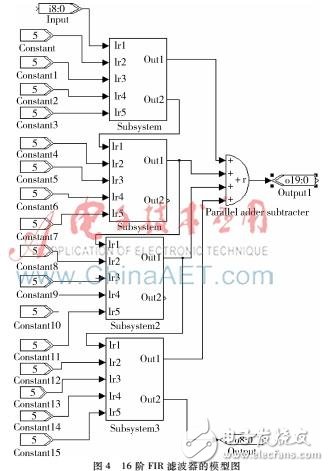

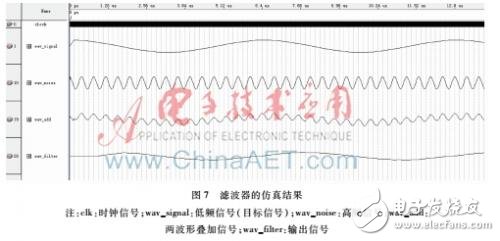

fpga實(shí)現(xiàn)濾波器fpga實(shí)現(xiàn)濾波器在利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理方面,分布式算法發(fā)揮著關(guān)鍵作用,與傳統(tǒng)的乘加結(jié)構(gòu)相比,具有并行處理的高效性特點(diǎn)。本文研究了一種16階FIR濾波器的FPGA設(shè)計(jì)方法

2012-08-12 11:50:16

。本文研究了一種16階FIR濾波器的FPGA設(shè)計(jì)方法,采用Verilog HDI語(yǔ)言描述設(shè)計(jì)文件,在Xilinx ISE 7.1i及ModelSim SE 6.1b平臺(tái)上進(jìn)行了實(shí)驗(yàn)仿真及時(shí)序分析,并探討了實(shí)際工程中硬件資源利用率及運(yùn)算速度等問(wèn)題。

2012-08-11 18:27:41

)、離散余弦變換(DCT)、小波變換、數(shù)字濾波器(有限脈沖響應(yīng)(FIR)、無(wú)限脈沖響應(yīng)(IIR)和自適應(yīng)濾波器)以及數(shù)字上下變頻器。這些算法中,每一種都有一些結(jié)構(gòu)性的元件可以用并行方法實(shí)現(xiàn)。而FPGA

2021-12-15 06:30:00

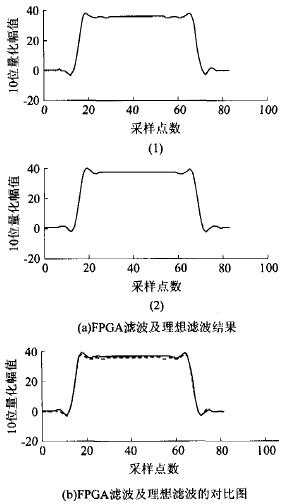

濾波器結(jié)構(gòu)圖:在時(shí)鐘允許信號(hào)的控制下,將數(shù)據(jù)以1/8系統(tǒng)時(shí)鐘頻率存入16個(gè)移位寄存器中,然后將對(duì)稱(chēng)系數(shù)的輸入數(shù)據(jù)相加,比如X(0)*X(N),X(1)*X(N-1),X(2)*X(N-2),同時(shí)將對(duì)應(yīng)的濾波器系數(shù)送入乘法器中得到結(jié)果mult_s,再對(duì)此乘法結(jié)果進(jìn)行累加sum

2017-08-02 17:35:24

最近在做一個(gè)FPGA的課程設(shè)計(jì),遇到一個(gè)比較煩人的問(wèn)題,希望大神們可以指點(diǎn)迷律。一個(gè)16階的FIR濾波器,采用分布式算法實(shí)現(xiàn)的,采樣率1M,fc=100K,頻率到了30K以上時(shí)就會(huì)出現(xiàn)那些尖刺,很

2018-02-25 19:25:50

性相位要求較高。如果有條件,采用FIR濾波器較好。當(dāng)然,在實(shí)際應(yīng)用中可能還要考慮更多方面的因素。 不論IIR和FIR,階數(shù)越高,信號(hào)延遲越大;同時(shí)在IIR濾波器中,階數(shù)越高,系數(shù)的精度要求越高,否則很容易造成

2019-09-29 14:06:31

是FIR濾波器模塊和加法器模塊和乘法器模塊。1.FIR濾波器模塊具有線性相位的半串行FIR濾波器結(jié)構(gòu)圖:在時(shí)鐘允許信號(hào)的控制下,將數(shù)據(jù)以1/8系統(tǒng)時(shí)鐘頻率存入16個(gè)移位寄存器中,然后將對(duì)稱(chēng)系數(shù)的輸入

2017-04-14 15:20:31

FIR濾波器如何定義?為什么要使用FIR濾波器?

2021-04-06 07:48:45

最近進(jìn)行FPGA學(xué)習(xí),使用FIR濾波器過(guò)程中出現(xiàn)以下問(wèn)題:使用FIR濾波器IP核中,輸入數(shù)據(jù)為1~256,濾波器系數(shù)為,coef =-1469,-14299 ,-2185,10587

2018-11-02 17:17:57

里面詳細(xì)的說(shuō)明了FIR原理,以及在MATLAB上仿真和在FPGA上實(shí)現(xiàn)FIR的過(guò)程。

2019-07-22 11:52:43

限脈沖響應(yīng)濾波器,又稱(chēng)為非遞歸型濾波器,是數(shù)字信號(hào)處理系統(tǒng)中最基本的元件,它可以在保證任意幅頻特性的同時(shí)具有嚴(yán)格的線性相頻特性,同時(shí)其單位抽樣響應(yīng)是有限長(zhǎng)的,因而濾波器是穩(wěn)定的系統(tǒng)。因此,FIR濾波器

2019-07-16 17:24:22

本帖最后由 eehome 于 2013-1-5 09:50 編輯

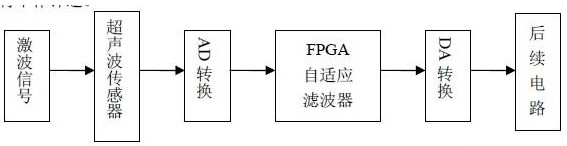

基于FPGA的FIR濾波器設(shè)計(jì)與實(shí)現(xiàn) 文章研究基于FPGA、采用分布式算法實(shí)現(xiàn)FIR濾波器的原理和方法,用

2012-08-11 15:32:34

基于FPGA的FIR數(shù)字濾波器的優(yōu)化設(shè)計(jì)

2012-08-17 23:55:09

在信息信號(hào)處理過(guò)程中,數(shù)字濾波器是信號(hào)處理中使用最廣泛的一種方法。通過(guò)濾波運(yùn)算,將一組輸入數(shù)據(jù)序列轉(zhuǎn)變?yōu)榱硪唤M輸出數(shù)據(jù)序列,從而實(shí)現(xiàn)時(shí)域或頻域中信號(hào)屬性的改變。常用的數(shù)字濾波器可分為有限脈沖響應(yīng)

2019-09-29 07:45:43

基于FPGA的fir濾波器實(shí)現(xiàn)

2017-08-28 19:57:36

1.引言數(shù)字濾波器在通信、自動(dòng)控制、雷達(dá)、軍事、航空航天、醫(yī)療、家用電器等眾多領(lǐng)域得到了廣泛的應(yīng)用。其中IIR數(shù)字濾波器和FIR數(shù)字濾波器是目前人們使用較多的兩種。數(shù)字濾波器通常采用計(jì)算機(jī)軟件、專(zhuān)用

2019-07-08 07:18:25

本帖最后由 eehome 于 2013-1-5 09:59 編輯

基于FPGA的高階FIR濾波器設(shè)計(jì)

2012-08-20 18:42:15

本帖最后由 eehome 于 2013-1-5 09:50 編輯

基于fpga的fir濾波器的實(shí)現(xiàn)

2012-08-17 16:42:33

脈沖響應(yīng)(ⅡR)濾波器和有限長(zhǎng)單位脈沖響應(yīng)(FIR)濾波器兩種,其中,FIR濾波器能提供理想的線性相位響應(yīng),在整個(gè)頻帶上獲得常數(shù)群時(shí)延從而得到零失真輸出信號(hào),同時(shí)它可以采用十分簡(jiǎn)單的算法實(shí)現(xiàn),這兩個(gè)

2019-08-30 07:18:39

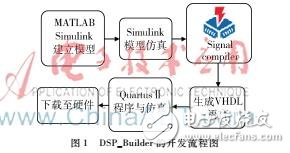

。關(guān)鍵詞:FIR,DSP,數(shù)字濾波器中圖分類(lèi)號(hào):TN7131. 引言數(shù)字濾波器在數(shù)字通信、語(yǔ)音圖象處理、譜分析、模式識(shí)別、自動(dòng)控制等領(lǐng)域得到了廣泛的應(yīng)用。相對(duì)于模擬濾波器,數(shù)字濾波器沒(méi)有漂移,能夠處理低頻

2008-05-14 23:30:12

FIR數(shù)字濾波器能夠滿(mǎn)足濾波器對(duì)幅度和相位特性的嚴(yán)格要求,避免模擬濾波器的溫漂和噪聲等問(wèn)題,具有精確的線性相位、易于硬件實(shí)現(xiàn)和系統(tǒng)穩(wěn)定等優(yōu)點(diǎn),可廣泛應(yīng)用于現(xiàn)代電子通信系統(tǒng)。實(shí)際信號(hào)處理應(yīng)用往往要求

2019-11-04 08:08:24

在電子設(shè)備中,到處都可以看到數(shù)字信號(hào)處理(DSP )的應(yīng)用,從MP3播放器、數(shù)碼相機(jī)到手機(jī)。DSP設(shè)計(jì)人員的工具箱的支柱之一是有限脈沖響應(yīng)(FIR )濾波器。FIR濾波器越長(zhǎng)(有大量的抽頭),濾波器

2019-07-08 08:01:03

信號(hào)處理算法與結(jié)構(gòu)的設(shè)計(jì)、發(fā)展都集成在一塊小的芯片上。?數(shù)字濾波器作為信號(hào)處理中最為常見(jiàn)的元件,被廣泛地應(yīng)用于無(wú)線通信的各個(gè)部分中。如何利用3G移動(dòng)通信中脈沖成形FIR濾波器實(shí)現(xiàn)ASIC? 就得先明白什么是基于分布式運(yùn)算(DA)結(jié)構(gòu)的查表法?

2019-08-02 07:16:02

本文提出一種基于Stratix系列FPGA器件的新的實(shí)時(shí)高速脈動(dòng)FIR濾波器的快速實(shí)現(xiàn)方法。

2021-05-06 09:50:42

在現(xiàn)代電子系統(tǒng)中,到處都可以看到數(shù)字信號(hào)處理( DSP )的應(yīng)用,從MP3播放器、數(shù)碼相機(jī)到手機(jī)。DSP設(shè)計(jì)人員的工具箱的支柱之一是有限脈沖響應(yīng)( FIR )濾波器。FIR濾波器越長(zhǎng)(有大量的抽頭

2019-08-06 07:12:39

本文首先介紹了FIR濾波器和脈動(dòng)陣列的原理,然后設(shè)計(jì)了脈動(dòng)陣列結(jié)構(gòu)的FIR濾波器,畫(huà)出電路的結(jié)構(gòu)框圖,并進(jìn)行了時(shí)序分析,最后在FPGA上進(jìn)行驗(yàn)證。結(jié)果表明,脈動(dòng)陣列的模塊化和高度流水線的結(jié)構(gòu)使FIR

2021-04-20 07:23:59

設(shè)計(jì)實(shí)現(xiàn)低通FIR濾波器一步設(shè)計(jì)和實(shí)現(xiàn)過(guò)濾器獲得濾波器系數(shù)可調(diào)諧低通FIR濾波器高級(jí)設(shè)計(jì)選項(xiàng):最佳非等效低通濾波器Equiripple設(shè)計(jì)增加阻帶衰減最小相位低通濾波器設(shè)計(jì)使用多級(jí)技術(shù)的最小

2018-08-23 10:00:16

在現(xiàn)代電子系統(tǒng)中,到處都可以看到數(shù)字信號(hào)處理( DSP )的應(yīng)用,從MP3播放器、數(shù)碼相機(jī)到手機(jī)。DSP設(shè)計(jì)人員的工具箱的支柱之一是有限脈沖響應(yīng)( FIR )濾波器。FIR濾波器越長(zhǎng)(有大量的抽頭

2019-10-22 06:55:44

設(shè)計(jì)FIR的方法。數(shù)字濾波器數(shù)字濾波器從實(shí)現(xiàn)結(jié)構(gòu)上劃分,有FIR和IIR兩種。FIR的特點(diǎn)是:線性相位、消耗資源多;IIR的特點(diǎn)是:非線性相位、消耗資源少。由于FIR系統(tǒng)的線性相位特點(diǎn),設(shè)計(jì)中絕大多數(shù)情況

2020-09-25 17:44:38

目前FIR濾波器的硬件實(shí)現(xiàn)的方式有哪幾種?怎么在FPGA上實(shí)現(xiàn)FIR濾波器的設(shè)計(jì)?

2021-05-07 06:03:13

并行流水結(jié)構(gòu)FIR的原理是什么基于并行流水線結(jié)構(gòu)的可重配FIR濾波器的FPGA實(shí)現(xiàn)

2021-04-29 06:30:54

本文以實(shí)現(xiàn)抽取率為2的具有線性相位的3階FIR抽取濾波器為例,介紹了一種用XC2V1000型FPGA實(shí)現(xiàn)FIR抽取濾波器的設(shè)計(jì)方法。

2021-05-07 06:02:47

相對(duì)無(wú)限沖擊響應(yīng)(IIR)濾波器,有限沖擊響應(yīng)(FIR)能夠在滿(mǎn)足濾波器幅頻響應(yīng)的同時(shí)獲得嚴(yán)格的線性相位特性,而數(shù)據(jù)通信、語(yǔ)音信號(hào)處理等領(lǐng)域往往要求信號(hào)在傳輸過(guò)程中不能有明顯的相位失真,所以FIR

2019-08-23 06:39:46

相對(duì)無(wú)限沖擊響應(yīng)(IIR)濾波器,有限沖擊響應(yīng)(FIR)能夠在滿(mǎn)足濾波器幅頻響應(yīng)的同時(shí)獲得嚴(yán)格的線性相位特性,而數(shù)據(jù)通信、語(yǔ)音信號(hào)處理等領(lǐng)域往往要求信號(hào)在傳輸過(guò)程中不能有明顯的相位失真,所以FIR

2019-08-27 07:16:54

分方程如下所示:由差分方程可知IIR濾波器存在反饋,因此在FPGA設(shè)計(jì)時(shí)要考慮到有限字長(zhǎng)效應(yīng)帶來(lái)的影響。差分方程中包括兩個(gè)部分:輸入信號(hào)x(n)的M節(jié)延時(shí)網(wǎng)絡(luò),相當(dāng)于FIR的網(wǎng)絡(luò)結(jié)構(gòu),實(shí)現(xiàn)系統(tǒng)的零點(diǎn)

2020-09-27 09:22:58

最近在學(xué)習(xí)全相位濾波器,請(qǐng)問(wèn)有人做過(guò)全相位FIR濾波器嗎?能不能用matlab程序來(lái)比較一下全相位FIR濾波器與傳統(tǒng)方法設(shè)計(jì)的FIR濾波器有什么區(qū)別??希望有人能幫我解答。。。感激不盡。。。。

2011-05-10 15:34:03

和相位特性。4、了解各種不同窗函數(shù)對(duì)濾波器性能的響應(yīng)二、實(shí)驗(yàn)原理和方法(一)FIR濾波器的設(shè)計(jì)在前面的實(shí)驗(yàn)中,我們介紹了IIR濾波器的設(shè)計(jì)方法并實(shí)踐了其中的雙線性變換法,IIR具有許多誘人的特性;但

2009-05-12 01:47:22

的作用;即DF(Digital Filter)是由差分方程描述的一類(lèi)特殊的離散時(shí)間系統(tǒng)。它的功能是把輸入序列通過(guò)一定的運(yùn)算變換成輸出序列。不同的運(yùn)算處理方法決定了濾波器的實(shí)現(xiàn)結(jié)構(gòu)的不同。35.1.2

2016-09-29 08:23:26

轉(zhuǎn)dsp系列教程 本章節(jié)講解FIR濾波器的低通,高通,帶通和帶阻濾波器的實(shí)現(xiàn)。 37.1 FIR濾波器介紹 37.2 Matlab工具箱生成C頭文件 37.3 FIR低通濾波器設(shè)計(jì) 37.4 FIR

2016-09-29 08:32:34

統(tǒng)計(jì)意義上最優(yōu)的現(xiàn)代濾波器(維納濾波器、自適應(yīng)濾波器等)等各種各樣的濾波器的理論與設(shè)計(jì)方法,新的理論也在不斷提出。讀者學(xué)習(xí)了本教程中的基礎(chǔ)后,就為掌握新的內(nèi)容打好了基礎(chǔ)。41.2 總結(jié) 本章節(jié)的內(nèi)容比較少,主要是總結(jié)性的說(shuō)明實(shí)際應(yīng)用中濾波器的選擇。

2016-09-30 10:47:59

選擇。從使用要求上來(lái)看,在對(duì)相位要求不敏感的場(chǎng)合,如語(yǔ)言通信等,選用IIR較為合適,這樣可以充分發(fā)揮其經(jīng)濟(jì)高效的特點(diǎn);對(duì)于圖像信號(hào)處理,數(shù)據(jù)傳輸?shù)纫圆ㄐ螖y帶信息的系統(tǒng),則對(duì)線性相位要求較高,采用FIR濾波器較好。當(dāng)然,在實(shí)際應(yīng)用中可能還要考慮更多方面的因素。

2023-05-29 16:47:16

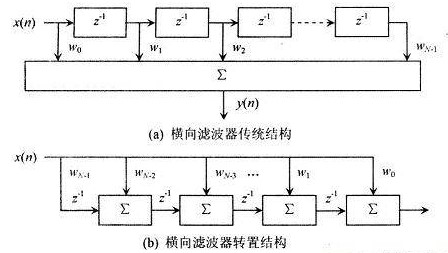

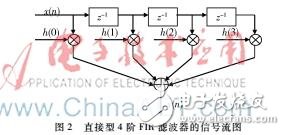

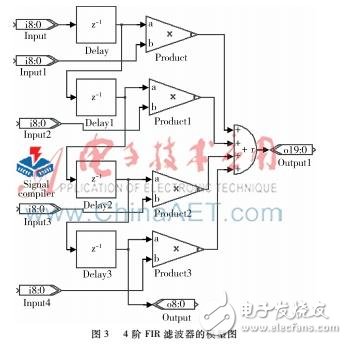

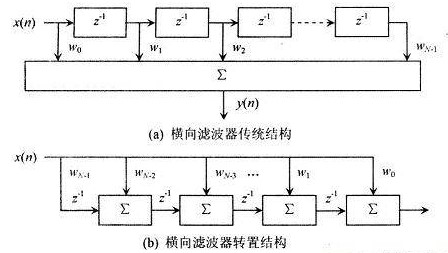

根據(jù)FIR濾波器的結(jié)構(gòu)形式,分為直接型、級(jí)聯(lián)型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)、分布式結(jié)構(gòu)。本案例實(shí)現(xiàn)了具有線性相位的半串行結(jié)構(gòu)的FIR濾波器。所謂串行結(jié)構(gòu),即串行實(shí)現(xiàn)

2017-05-23 10:11:26

、FIR濾波器的FPGA實(shí)現(xiàn)好了,matlab仿真成功,剩下的就需要在FPGA上實(shí)現(xiàn)了,在FPGA上實(shí)現(xiàn)什么呢?前面我們已經(jīng)得到了濾波器的系數(shù),只要有了濾波器系數(shù),剩下的不就是乘積累加了么,所以,我們需要

2015-06-16 19:25:35

用窗函數(shù)設(shè)計(jì)FIR濾波器一、實(shí)驗(yàn)?zāi)康?、熟悉FIR濾波器設(shè)計(jì)的基本方法。2、掌握用窗函數(shù)設(shè)計(jì)FIR數(shù)字濾波器的原理及方法,熟悉相應(yīng)的計(jì)算機(jī)高級(jí)語(yǔ)言編程。3、熟悉線性

2009-05-10 10:02:15 97

97 本文提出了一種采用現(xiàn)場(chǎng)可編程門(mén)陣列器件 FPGA 實(shí)現(xiàn)FIR 字濾波器硬件電路的方案,該方案基于只讀存儲(chǔ)器ROM 查找表的分布式算法。并以一個(gè)十六階低通FIR 數(shù)字濾波電路在ALTERA 公

2009-08-31 16:47:47 44

44 本文介紹了能高效實(shí)現(xiàn)固定常數(shù)乘法的分布式算法原理,給出了在FPGA 中用查找表實(shí)現(xiàn)FIR濾波器的算法設(shè)計(jì),并以一個(gè)16 階低通濾波器為例說(shuō)明了設(shè)計(jì)過(guò)程。該設(shè)計(jì)通過(guò)Altera 公司的EP

2009-09-02 10:10:02 10

10 基于FPGA對(duì)稱(chēng)型FIR濾波器的設(shè)計(jì)與實(shí)現(xiàn):在基于FPGA的對(duì)稱(chēng)型FIR數(shù)字濾波器設(shè)計(jì)中,為了提高速度和運(yùn)行效率,提出了使用線性I相位結(jié)構(gòu)和加法樹(shù)乘法器的方法,并利用Altera公I(xiàn)司的FPG

2009-09-25 15:38:38 30

30 高效FIR濾波器的設(shè)計(jì)與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(yīng)(FIR)數(shù)字濾波器理論及常見(jiàn)實(shí)現(xiàn)方法的基礎(chǔ)上,提出了一種基于FPGA的高效實(shí)現(xiàn)方案。

2008-01-16 09:56:02 1456

1456

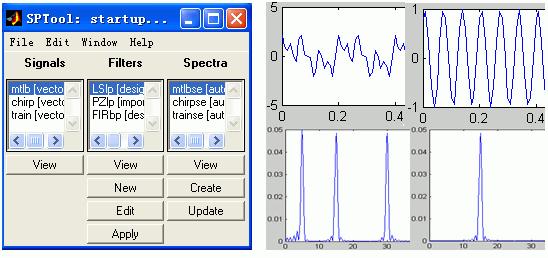

用MATLAB設(shè)計(jì)FIR濾波器的方法

摘? 要 介紹了利用MATLAB信號(hào)處理工具箱進(jìn)行FIR濾波器設(shè)計(jì)的三種方法:程序設(shè)計(jì)法、FDATool設(shè)計(jì)法和SPTool設(shè)計(jì)法,給

2008-01-16 18:12:15 14763

14763

如何用用FPGA實(shí)現(xiàn)FIR濾波器

你接到要求用FPGA實(shí)現(xiàn)FIR濾波器的任務(wù)時(shí),也許會(huì)想起在學(xué)校里所學(xué)的FIR基礎(chǔ)知識(shí),但是下一步該做什么呢?哪些參數(shù)是重

2009-03-30 12:25:45 4503

4503

摘要: 針對(duì)在FPGA中實(shí)現(xiàn)FIR濾波器的關(guān)鍵--乘法運(yùn)算的高效實(shí)現(xiàn)進(jìn)行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設(shè)計(jì)了FIR濾波器。通過(guò)FPGA仿零點(diǎn)驗(yàn)證

2009-06-20 14:09:36 677

677

FIR帶通濾波器的FPGA實(shí)現(xiàn)

引 言??? 在FPGA應(yīng)用中,比較廣泛而基礎(chǔ)的就是數(shù)字濾波器。根據(jù)其單位沖激響應(yīng)函數(shù)的時(shí)域特性可分為無(wú)限沖擊響應(yīng)(Infinite

2009-11-13 09:55:18 6564

6564

基于流水線技術(shù),利用FPGA進(jìn)行并行可重復(fù)配置高精度的 FIR濾波器 設(shè)計(jì)。使用VHDL可以很方便地改變濾波器的系數(shù)和階數(shù)。在DSP中采用這種FIR濾波器的設(shè)計(jì)方法可以充分發(fā)揮FPGA的優(yōu)勢(shì)。

2011-07-18 17:09:28 63

63 目前數(shù)字濾波器的硬件實(shí)現(xiàn)方法通常采用專(zhuān)用DSP芯片或FPGA,本文從FIR濾波器的系數(shù)考慮,采用CSD編碼,對(duì)FIR數(shù)字濾波器進(jìn)行優(yōu)化設(shè)計(jì)。

2011-08-16 10:54:41 3632

3632

描述了基于FPGA的FIR濾波器設(shè)計(jì)。根據(jù)FIR的原理及嚴(yán)格線性相位濾波器具有偶對(duì)稱(chēng)的性質(zhì)給出了FIR濾波器的4種結(jié)構(gòu),即直接乘加結(jié)構(gòu)、乘法器復(fù)用結(jié)構(gòu)、乘累加結(jié)構(gòu)、DA算法。在本文中給

2012-11-09 17:32:37 121

121 FIR(Finite Impulse Response,有限沖擊響應(yīng))數(shù)字濾波器具有穩(wěn)定性高、可以實(shí)現(xiàn)線性相位等優(yōu)點(diǎn),廣泛被應(yīng)用于信號(hào)檢測(cè)與處理等領(lǐng)域。由于FPGA(Field Programmable Gate Array,現(xiàn)場(chǎng)可編程門(mén)陣

2012-12-03 11:50:23 5499

5499 基于matlab和fpga的FIR濾波器設(shè)計(jì),有興趣的同學(xué)可以下載學(xué)習(xí)

2016-04-27 15:51:58 56

56 基于FPGA的FIR濾波器設(shè)計(jì)與實(shí)現(xiàn),下來(lái)看看

2016-05-10 11:49:02 38

38 基于FPGA實(shí)現(xiàn)變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 中心頻率可調(diào)的FIR數(shù)字帶通濾波器設(shè)計(jì),下來(lái)看看

2017-01-07 21:24:42 13

13 研究了一種采用FPGA實(shí)現(xiàn)32階FIR濾波器硬件電路方案;討論了窗函數(shù)的選擇、濾波器的結(jié)構(gòu)以及系數(shù)量化問(wèn)題;研究了FIR濾波器的FPGA實(shí)現(xiàn),各模塊的設(shè)計(jì)以及如何優(yōu)化硬件資源,提高運(yùn)行

2017-11-10 16:41:57 15

15 累加,實(shí)現(xiàn)了FIR 濾波功能。該濾波器具有占用極少的資源、提高濾波速度和高速靈活性等優(yōu)點(diǎn)。在通信系統(tǒng)、航空航天系統(tǒng)、雷達(dá)系統(tǒng)、遙感遙測(cè)系統(tǒng)等工程技術(shù)領(lǐng)域,無(wú)論是在信號(hào)的獲取、傳輸,還是信號(hào)的處理和轉(zhuǎn)換

2017-11-22 07:39:45 2735

2735

本文針對(duì)快速、準(zhǔn)確選擇參數(shù)符合項(xiàng)目要求的濾波器設(shè)計(jì)方法的目的,通過(guò)系統(tǒng)的介紹有限脈沖響應(yīng)( Finite Impulse Response,FIR)濾波器的原理、結(jié)構(gòu)形式以及幾種FIR濾波器設(shè)計(jì)方法

2017-12-21 14:53:14 14

14 文介紹了FIR抽取濾波器的工作原理,重點(diǎn)闡述了用XC2V1000實(shí)現(xiàn)FIR抽取濾波器的方法,并給出了仿真波形和設(shè)計(jì)特點(diǎn)。

2018-04-19 11:34:00 1846

1846

用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號(hào)處理方面有了長(zhǎng)足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計(jì)方法。

2018-04-28 11:50:00 1073

1073

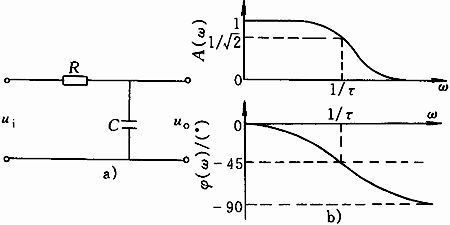

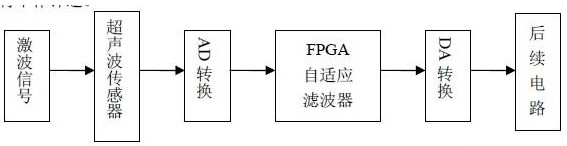

自適應(yīng)濾波器的常用實(shí)現(xiàn)形式有 FIR和IIR兩種,而 FIR濾波器是實(shí)際應(yīng)用較為廣泛的一種,FIR濾波器只有可調(diào)的零點(diǎn),因此它沒(méi)有 IIR因兼有可調(diào)的零點(diǎn)和極點(diǎn)而帶來(lái)的不穩(wěn)定問(wèn)題,此外,LMS計(jì)算量小,易于硬件實(shí)現(xiàn),故本文采用的濾波器是基于FIR基礎(chǔ)之上構(gòu)建的 LMS自適應(yīng)濾波器。

2019-04-02 09:31:00 2372

2372

在數(shù)字信號(hào)處理領(lǐng)域,濾波器無(wú)疑是個(gè)非常重要的環(huán)節(jié)。而在數(shù)字濾波器中,有限脈沖響應(yīng)(FIR)濾波器因?yàn)槠渚€性相位的特點(diǎn),應(yīng)用尤為廣泛。實(shí)際應(yīng)用中FIR濾波器分為常系數(shù)FIR濾波器和變系數(shù)FIR濾波器

2019-04-22 08:07:00 5006

5006

用FPGA實(shí)現(xiàn)抽取濾波器比較復(fù)雜,主要是因?yàn)樵?b class="flag-6" style="color: red">FPGA中缺乏實(shí)現(xiàn)乘法運(yùn)算的有效結(jié)構(gòu),現(xiàn)在,FPGA中集成了硬件乘法器,使FPGA在數(shù)字信號(hào)處理方面有了長(zhǎng)足的進(jìn)步。本文介紹了一種采用Xilinx公司的XC2V1000實(shí)現(xiàn)FIR抽取濾波器的設(shè)計(jì)方法。

2020-09-25 10:44:00 3

3 提出一種新的高階FIR濾波器的FPGA實(shí)現(xiàn)方法。該方法運(yùn)用多相分解結(jié)構(gòu)對(duì)高階FIR濾波器進(jìn)行降階處理,采用改進(jìn)的分布式算法來(lái)實(shí)現(xiàn)降階后的FIR濾波器。設(shè)計(jì)了一系列階數(shù)從8到1 024的FIR濾波器

2021-03-23 15:44:54 30

30 數(shù)字濾波器從實(shí)現(xiàn)結(jié)構(gòu)上劃分,有FIR和IIR兩種。FIR的特點(diǎn)是:線性相位、消耗資源多;IIR的特點(diǎn)是:非線性相位、消耗資源少。由于FIR系統(tǒng)的線性相位特點(diǎn),設(shè)計(jì)中絕大多數(shù)情況都采用FIR濾波器。

2022-04-24 14:40:16 2492

2492 引言 目前,用FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)實(shí)現(xiàn)FIR(有限沖擊響應(yīng)) 濾波器 的方法大多利用FPGA中LUT(查找表)的特點(diǎn)采用DA(分布式算法)或CSD碼等方法,將乘加運(yùn)算操作轉(zhuǎn)化為位與、加減

2022-12-01 10:20:05 698

698 FIR濾波器設(shè)計(jì)方法主要有窗函數(shù)法、線性最小均方差法、最大似然法、自適應(yīng)濾波法、線性預(yù)測(cè)法等。窗函數(shù)法是一種簡(jiǎn)單的設(shè)計(jì)方法,它可以通過(guò)選擇合適的窗函數(shù)來(lái)實(shí)現(xiàn)濾波器的設(shè)計(jì);而線性最小均方差法則是一種更加復(fù)雜的設(shè)計(jì)方法,它可以通過(guò)最小化濾波器的均方差來(lái)實(shí)現(xiàn)濾波器的設(shè)計(jì)。

2023-02-15 14:58:37 1199

1199 FIR濾波器設(shè)計(jì)方法主要有窗函數(shù)法、線性最小均方差法、最大似然法、自適應(yīng)濾波法、線性預(yù)測(cè)法等。窗函數(shù)法是一種簡(jiǎn)單的設(shè)計(jì)方法,它可以通過(guò)選擇合適的窗函數(shù)來(lái)實(shí)現(xiàn)濾波器的設(shè)計(jì);而線性最小均方差法則是一種更加復(fù)雜的設(shè)計(jì)方法,它可以通過(guò)最小化濾波器的均方差來(lái)實(shí)現(xiàn)濾波器的設(shè)計(jì)。

2023-02-15 15:29:19 2794

2794 本文介紹了設(shè)計(jì)濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書(shū)籍中的串行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計(jì),對(duì)書(shū)中的架構(gòu)做了簡(jiǎn)單的優(yōu)化,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:56:34 552

552

本文介紹了設(shè)計(jì)濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書(shū)籍中的并行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計(jì),對(duì)書(shū)中的架構(gòu)做了復(fù)現(xiàn)以及解讀,并進(jìn)行了仿真驗(yàn)證。

2023-05-24 10:57:36 653

653

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 本文將回顧對(duì)稱(chēng) F IR ? 濾波器 的高效 FPGA 實(shí)現(xiàn)的注意事項(xiàng)。 本文將推導(dǎo)對(duì)稱(chēng) FIR 濾波器的模塊化流水線結(jié)構(gòu)。我們將看到派生結(jié)構(gòu)可以使用? Xilinx

2023-05-26 01:20:02 441

441

電子發(fā)燒友網(wǎng)站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費(fèi)下載

2023-06-14 15:28:49 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論