ARM(Advanced RISC Machines)是微處理器行業(yè)的一家知名企業(yè),設(shè)計(jì)了大量高性能、廉價(jià)、耗能低的RISC處理器、相關(guān)技術(shù)及軟件。ARM也是單片機(jī)。ARM架構(gòu)是面向低預(yù)算市場(chǎng)設(shè)計(jì)的第一款RISC微處理器,基本是32位單片機(jī)的行業(yè)標(biāo)準(zhǔn),它提供一系列內(nèi)核、體系擴(kuò)展、微處理器和系統(tǒng)芯片方案,四個(gè)功能模塊可供生產(chǎn)廠商根據(jù)不同用戶的要求來配置生產(chǎn)。

由于所有產(chǎn)品均采用一個(gè)通用的軟件體系,所以相同的軟件可在所有產(chǎn)品中運(yùn)行。目前ARM在手持設(shè)備市場(chǎng)占有90以上的份額,可以有效地縮短應(yīng)用程序開發(fā)與測(cè)試的時(shí)間,也降低了研發(fā)費(fèi)用。

DSP(digital singnal processor)是 一種獨(dú)特的微處理器,有自己的完整指令系統(tǒng),是以數(shù)字信號(hào)來處理大量信息的器件。一個(gè)數(shù)字信號(hào)處理器在一塊不大的芯片內(nèi)包括有控制單元、運(yùn)算單元、各種寄 存器以及一定數(shù)量的存儲(chǔ)單元等等,在其外圍還可以連接若干存儲(chǔ)器,并可以與一定數(shù)量的外部設(shè)備互相通信,有軟、硬件的全面功能,本身就是一個(gè)微型計(jì)算機(jī)。

DSP采 用的是哈佛設(shè)計(jì),即數(shù)據(jù)總線和地址總線分開,使程序和數(shù)據(jù)分別存儲(chǔ)在兩個(gè)分開的空間,允許取指令和執(zhí)行指令完全重疊。也就是說在執(zhí)行上一條指令的同時(shí)就可 取出下一條指令,并進(jìn)行譯碼,這大大的提高了微處理器的速度 。另外還允許在程序空間和數(shù)據(jù)空間之間進(jìn)行傳輸,因?yàn)樵黾恿似骷撵`活性。其工作原理是接收模擬信號(hào),轉(zhuǎn)換為0或1的數(shù)字信號(hào),再對(duì)數(shù)字信號(hào)進(jìn)行修改、刪除、強(qiáng)化,并在其他系統(tǒng)芯片中把數(shù)字?jǐn)?shù)據(jù)解譯回模擬數(shù)據(jù)或?qū)嶋H環(huán)境格式。它不僅具有可編程性,而且其實(shí)時(shí)運(yùn)行速度可達(dá)每秒數(shù)以千萬條復(fù)雜指令程序,遠(yuǎn)遠(yuǎn)超過通用微處理器,是數(shù)字化電子世界中日益重要的電腦芯片。

它的強(qiáng)大數(shù)據(jù)處理能力和高運(yùn)行速度,是最值得稱道的兩大特色。由于它運(yùn)算能力很強(qiáng),速度很快,體積很小,而且采用軟件編程具有高度的靈活性,因此為從事各種復(fù)雜的應(yīng)用提供了一條有效途徑。根據(jù)數(shù)字信號(hào)處理的要求,DSP芯片一般具有如下主要特點(diǎn):

(1)在一個(gè)指令周期內(nèi)可完成一次乘法和一次加法;

(2)程序和數(shù)據(jù)空間分開,可以同時(shí)訪問指令和數(shù)據(jù);

(3)片內(nèi)具有快速RAM,通常可通過獨(dú)立的數(shù)據(jù)總線在兩塊中同時(shí)訪問;

(4)具有低開銷或無開銷循環(huán)及跳轉(zhuǎn)的硬件支持;

(5)快速的中斷處理和硬件I/O支持;

(6)具有在單周期內(nèi)操作的多個(gè)硬件地址產(chǎn)生器;

(7)可以并行執(zhí)行多個(gè)操作;

(8)支持流水線操作,使取指、譯碼和執(zhí)行等操作可以重疊執(zhí)行。

當(dāng)然,與通用微處理器相比,DSP芯片的其他通用功能相對(duì)較弱些。

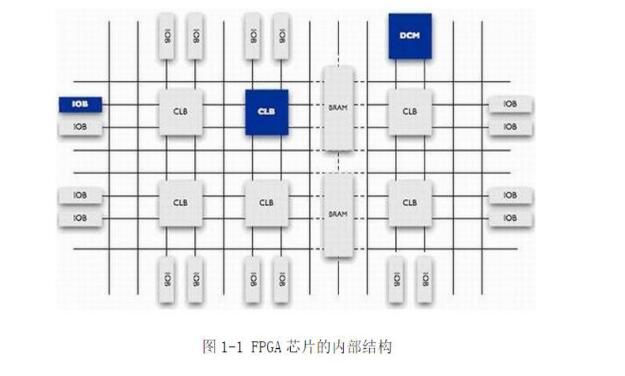

FPGA(Field Programmable Gate Array)(現(xiàn)場(chǎng)可編程門陣列)的縮寫,它是在PAL、GAL、PLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物,是專用集成電路(ASIC)中集成度最高的一種。FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個(gè)新概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個(gè)部分。

用戶可對(duì)FPGA內(nèi)部的邏輯模塊和I/O模塊重新配置,以實(shí)現(xiàn)用戶的邏輯。它還具有靜態(tài)可重復(fù)編程和動(dòng)態(tài)在系統(tǒng)重構(gòu)的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路,F(xiàn)PGA既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。可以毫不夸張的講,F(xiàn)PGA能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用FPGA來實(shí)現(xiàn)。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入法,或是硬件描述語言自由的設(shè)計(jì)一個(gè)數(shù)字系統(tǒng)。通過軟件仿真,我們可以事先驗(yàn)證設(shè)計(jì)的正確性。在PCB完成以后,還可以利用FPGA的在線修改能力,隨時(shí)修改設(shè)計(jì)而不必改動(dòng)硬件電路。使用FPGA來開發(fā)數(shù)字電路,可以大大縮短設(shè)計(jì)時(shí)間,減少PCB面積,提高系統(tǒng)的可靠性。

FPGA是由存放在片內(nèi)RAM中的程序來設(shè)置其工作狀態(tài)的,因此工作時(shí)需要對(duì)片內(nèi)的RAM進(jìn)行編程。用戶可以根據(jù)不同的配置模式,采用不同的編程方式。加電時(shí),F(xiàn)PGA芯片將EPROM中數(shù)據(jù)讀入片內(nèi)編程RAM中,配置完成后,F(xiàn)PGA進(jìn)入工作狀態(tài)。掉電后,F(xiàn)PGA恢復(fù)成白片,內(nèi)部邏輯關(guān)系消失,因此,F(xiàn)PGA能夠反復(fù)使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。當(dāng)需要修改FPGA功能時(shí),只需換一片EPROM即可。這樣,同一片F(xiàn)PGA,不同的編程數(shù)據(jù),可以產(chǎn)生不同的電路功能。因此,F(xiàn)PGA的使用非常靈活。可以說,F(xiàn)PGA芯片是小批量系統(tǒng)提高系統(tǒng)集成度、可靠性的最佳選擇之一。目前FPGA的品種很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FIEX系列等。

那么它們的區(qū)別有哪些呢?

ARM具有比較強(qiáng)的事務(wù)管理功能,可以用來跑界面以及應(yīng)用程序等,其優(yōu)勢(shì)主要體現(xiàn)在控制方面,而DSP主要是用來計(jì)算的,比如進(jìn)行加密解密、調(diào)制解調(diào)等,優(yōu)勢(shì)是強(qiáng)大的數(shù)據(jù)處理能力和較高的運(yùn)行速度。FPGA可以用VHDL或verilogHDL來編程,靈活性強(qiáng),由于能夠進(jìn)行編程、除錯(cuò)、再編程和重復(fù)操作,因此可以充分地進(jìn)行設(shè)計(jì)開發(fā)和驗(yàn)證。當(dāng)電路有少量改動(dòng)時(shí),更能顯示出FPGA的優(yōu)勢(shì),其現(xiàn)場(chǎng)編程能力可以延長產(chǎn)品在市場(chǎng)上的壽命,而這種能力可以用來進(jìn)行系統(tǒng)升級(jí)或除錯(cuò)。

作為Processor,這幾種器件有什么有優(yōu)缺點(diǎn)。

其實(shí)C51,ARM,DSP都不是單獨(dú)作為芯片來提供給用戶的,都要加一些外圍電路來支持。

例如:memory controller,interrupt controller,timer,UART,SPI,I2C等等。

所以要比較最好從processor的角度來比較他們。

(1)。 C51是8位的;ARM是32位的;DSP有16位的,也有更高的。

(2)。所有說從運(yùn)算能力上看,C51最弱,DSP最強(qiáng),ARM居中。

(3)。結(jié)構(gòu)差別較大,C51最簡(jiǎn)單,是一般的馮諾伊曼結(jié)構(gòu);ARM9以上是哈佛結(jié)構(gòu)的RISC;DSP一般使用哈佛結(jié)構(gòu)。

(4).C51一般芯片面積非常小,工作頻率很低(一般是10多MHz,有的是24MHz),所以功耗低。DSP則頻率很高(高的達(dá)到300MHz以上),所以功耗大。ARM芯片面積也很小,ARM7是0.55平方毫米,功耗也比較小。頻率大約在(幾十到200MHz之間)

(5)。所以一般C51主要應(yīng)用于不需要太多計(jì)算量的控制類系統(tǒng)。一般配有豐富的外圍module。DSP則主要應(yīng)用于需要進(jìn)行復(fù)雜計(jì)算的高端系統(tǒng),例如圖像處理,加密解密,導(dǎo)航系統(tǒng)等,外圍module一般較少。ARM是C51和DSP之間的一個(gè)折衷。

(6)。強(qiáng)調(diào)一點(diǎn):C51的性能遠(yuǎn)不如ARM和DSP,但仍然占據(jù)重要的一席之地,原因就是性能價(jià)格比。因?yàn)樗墒炝耍×耍阋肆恕6谝恍┬枰獜?fù)雜計(jì)算的領(lǐng)域,DSP也不可或缺。ARM的成功就是他找到了一個(gè)折衷點(diǎn),并且建立了一個(gè)非常靈活的商業(yè)模型。

CPLD(Complex Programmable Logic Device)復(fù)雜可編程邏輯器件, 是從PAL和GAL器件發(fā)展出來的器件,相對(duì)而言規(guī)模大,結(jié)構(gòu)復(fù)雜,屬于大規(guī)模集成電路范圍。是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。 其基本設(shè)計(jì)方法是借助集成開發(fā)軟件平臺(tái),用原理圖、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,通過下載電纜(“在系統(tǒng)”編程)將代碼傳送到目標(biāo)芯片中,實(shí) 現(xiàn)設(shè)計(jì)的數(shù)字系統(tǒng)。

FPGA和CPLD的區(qū)別

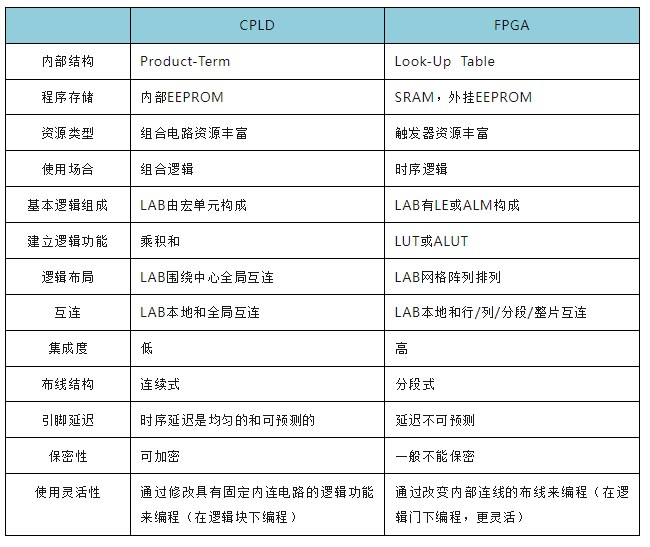

FPGA與 CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點(diǎn)和工作原理。通常的分類方法是:將以乘積項(xiàng)結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD,如Lattice的 ispLSI系列、Xilinx的XC9500系列、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。

將以查表法結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K或ACEX1K系列等。

盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點(diǎn),但由于CPLD和FPGA結(jié)構(gòu)上的差異,具有各自的特點(diǎn):

①CPLD更適合完成各種算法和組合邏輯,F(xiàn)PGA更適合于完成時(shí)序邏輯。換句話說,F(xiàn)PGA更適合于觸發(fā)器豐富的結(jié)構(gòu),而CPLD更適合于觸發(fā)器有限而乘積項(xiàng)豐富的結(jié)構(gòu)。

②CPLD的連續(xù)式布線結(jié)構(gòu)決定了它的時(shí)序延遲是均勻的和可預(yù)測(cè)的,而FPGA的分段式布線結(jié)構(gòu)決定了其延遲的不可預(yù)測(cè)性。

③在編程上FPGA比CPLD具有更大的靈活性。CPLD通過修改具有固定內(nèi)連電路的邏輯功能來編程,F(xiàn)PGA主要通過改變內(nèi)部連線的布線來編程;FPGA可在邏輯門下編程,而CPLD是在邏輯塊下編程。

④FPGA的集成度比CPLD高,具有更復(fù)雜的布線結(jié)構(gòu)和邏輯實(shí)現(xiàn)。

⑤CPLD比FPGA使用起來更方便。CPLD的編程采用E2PROM或FASTFLASH技術(shù),無需外部存儲(chǔ)器芯片,使用簡(jiǎn)單。而FPGA的編程信息需存放在外部存儲(chǔ)器上,使用方法復(fù)雜。

⑥CPLD的速度比FPGA快,并且具有較大的時(shí)間可預(yù)測(cè)性。這是由于FPGA是門級(jí)編程,并且CLB之間采用分布式互聯(lián),而CPLD是邏輯塊級(jí)編程,并且其邏輯塊之間的互聯(lián)是集總式的。

⑦在編程方式上,CPLD主要是基于E2PROM或FLASH存儲(chǔ)器編程,編程次數(shù)可達(dá)1萬次,優(yōu)點(diǎn)是系統(tǒng)斷電時(shí)編程信息也不丟失。CPLD又可分為在編程器上編程和在系統(tǒng)編程兩類。FPGA大部分是基于SRAM編程,編程信息在系統(tǒng)斷電時(shí)丟失,每次上電時(shí),需從器件外部將編程數(shù)據(jù)重新寫入SRAM中。其優(yōu)點(diǎn)是可以編程任意次,可在工作中快速編程,從而實(shí)現(xiàn)板級(jí)和系統(tǒng)級(jí)的動(dòng)態(tài)配置。

⑧CPLD保密性好,F(xiàn)PGA保密性差。

⑨一般情況下,CPLD的功耗要比FPGA大,且集成度越高越明顯。

用戶可對(duì)FPGA內(nèi)部的邏輯模塊和I/O模塊重新配置,以實(shí)現(xiàn)用戶的邏輯。它還具有靜態(tài)可重復(fù)編程和動(dòng)態(tài)在系統(tǒng)重構(gòu)的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路,F(xiàn)PGA既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。可以毫不夸張的講,F(xiàn)PGA能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡(jiǎn)單的74電路,都可以用FPGA來實(shí)現(xiàn)。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入法,或是硬件描述語言自由的設(shè)計(jì)一個(gè)數(shù)字系統(tǒng)。通過軟件仿真,我們可以事先驗(yàn)證設(shè)計(jì)的正確性。在PCB完成以后,還可以利用FPGA的在線修改能力,隨時(shí)修改設(shè)計(jì)而不必改動(dòng)硬件電路。使用FPGA來開發(fā)數(shù)字電路,可以大大縮短設(shè)計(jì)時(shí)間,減少PCB面積,提高系統(tǒng)的可靠性。

FPGA是由存放在片內(nèi)RAM中的程序來設(shè)置其工作狀態(tài)的,因此工作時(shí)需要對(duì)片內(nèi)的RAM進(jìn)行編程。用戶可以根據(jù)不同的配置模式,采用不同的編程方式。加電時(shí),F(xiàn)PGA芯片將EPROM中數(shù)據(jù)讀入片內(nèi)編程RAM中,配置完成后,F(xiàn)PGA進(jìn)入工作狀態(tài)。掉電后,F(xiàn)PGA恢復(fù)成白片,內(nèi)部邏輯關(guān)系消失,因此,F(xiàn)PGA能夠反復(fù)使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。當(dāng)需要修改FPGA功能時(shí),只需換一片EPROM即可。這樣,同一片F(xiàn)PGA,不同的編程數(shù)據(jù),可以產(chǎn)生不同的電路功能。因此,F(xiàn)PGA的使用非常靈活。可以說,F(xiàn)PGA芯片是小批量系統(tǒng)提高系統(tǒng)集成度、可靠性的最佳選擇之一。目前FPGA的品種很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FIEX系列等。

那么它們的區(qū)別有哪些呢?

ARM具有比較強(qiáng)的事務(wù)管理功能,可以用來跑界面以及應(yīng)用程序等,其優(yōu)勢(shì)主要體現(xiàn)在控制方面,而DSP主要是用來計(jì)算的,比如進(jìn)行加密解密、調(diào)制解調(diào)等,優(yōu)勢(shì)是強(qiáng)大的數(shù)據(jù)處理能力和較高的運(yùn)行速度。FPGA可以用VHDL或verilogHDL來編程,靈活性強(qiáng),由于能夠進(jìn)行編程、除錯(cuò)、再編程和重復(fù)操作,因此可以充分地進(jìn)行設(shè)計(jì)開發(fā)和驗(yàn)證。當(dāng)電路有少量改動(dòng)時(shí),更能顯示出FPGA的優(yōu)勢(shì),其現(xiàn)場(chǎng)編程能力可以延長產(chǎn)品在市場(chǎng)上的壽命,而這種能力可以用來進(jìn)行系統(tǒng)升級(jí)或除錯(cuò)。

作為Processor,這幾種器件有什么有優(yōu)缺點(diǎn)。

其實(shí)C51,ARM,DSP都不是單獨(dú)作為芯片來提供給用戶的,都要加一些外圍電路來支持。

例如:memory controller,interrupt controller,timer,UART,SPI,I2C等等。

所以要比較最好從processor的角度來比較他們。

(1). C51是8位的;ARM是32位的;DSP有16位的,也有更高的。

(2).所有說從運(yùn)算能力上看,C51最弱,DSP最強(qiáng),ARM居中。

(3).結(jié)構(gòu)差別較大,C51最簡(jiǎn)單,是一般的馮諾伊曼結(jié)構(gòu);ARM9以上是哈佛結(jié)構(gòu)的RISC;DSP一般使用哈佛結(jié)構(gòu)。

(4).C51一般芯片面積非常小,工作頻率很低(一般是10多MHz,有的是24MHz),所以功耗低。DSP則頻率很高(高的達(dá)到300MHz以上),所以功耗大。ARM芯片面積也很小,ARM7是0.55平方毫米,功耗也比較小。頻率大約在(幾十到200MHz之間)

(5).所以一般C51主要應(yīng)用于不需要太多計(jì)算量的控制類系統(tǒng)。一般配有豐富的外圍module。DSP則主要應(yīng)用于需要進(jìn)行復(fù)雜計(jì)算的高端系統(tǒng),例如圖像處理,加密解密,導(dǎo)航系統(tǒng)等,外圍module一般較少。ARM是C51和DSP之間的一個(gè)折衷。

(6).強(qiáng)調(diào)一點(diǎn):C51的性能遠(yuǎn)不如ARM和DSP,但仍然占據(jù)重要的一席之地,原因就是性能價(jià)格比。因?yàn)樗墒炝耍×耍阋肆恕6谝恍┬枰獜?fù)雜計(jì)算的領(lǐng)域,DSP也不可或缺。ARM的成功就是他找到了一個(gè)折衷點(diǎn),并且建立了一個(gè)非常靈活的商業(yè)模型。

CPLD(Complex Programmable Logic Device)復(fù)雜可編程邏輯器件, 是從PAL和GAL器件發(fā)展出來的器件,相對(duì)而言規(guī)模大,結(jié)構(gòu)復(fù)雜,屬于大規(guī)模集成電路范圍。是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。 其基本設(shè)計(jì)方法是借助集成開發(fā)軟件平臺(tái),用原理圖、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,通過下載電纜(“在系統(tǒng)”編程)將代碼傳送到目標(biāo)芯片中,實(shí) 現(xiàn)設(shè)計(jì)的數(shù)字系統(tǒng).

FPGA和CPLD的區(qū)別

FPGA與 CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點(diǎn)和工作原理。通常的分類方法是:將以乘積項(xiàng)結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD,如Lattice的 ispLSI系列、Xilinx的XC9500系列、Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。

將以查表法結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為FPGA,如Xilinx的SPARTAN系列、Altera的FLEX10K或ACEX1K系列等。

盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點(diǎn),但由于CPLD和FPGA結(jié)構(gòu)上的差異,具有各自的特點(diǎn):

①CPLD更適合完成各種算法和組合邏輯,FPGA更適合于完成時(shí)序邏輯。換句話說,FPGA更適合于觸發(fā)器豐富的結(jié)構(gòu),而CPLD更適合于觸發(fā)器有限而乘積項(xiàng)豐富的結(jié)構(gòu)。

②CPLD的連續(xù)式布線結(jié)構(gòu)決定了它的時(shí)序延遲是均勻的和可預(yù)測(cè)的,而FPGA的分段式布線結(jié)構(gòu)決定了其延遲的不可預(yù)測(cè)性。

③在編程上FPGA比CPLD具有更大的靈活性。CPLD通過修改具有固定內(nèi)連電路的邏輯功能來編程,FPGA主要通過改變內(nèi)部連線的布線來編程;FPGA可在邏輯門下編程,而CPLD是在邏輯塊下編程。

④FPGA的集成度比CPLD高,具有更復(fù)雜的布線結(jié)構(gòu)和邏輯實(shí)現(xiàn)。

⑤CPLD比FPGA使用起來更方便。CPLD的編程采用E2PROM或FASTFLASH技術(shù),無需外部存儲(chǔ)器芯片,使用簡(jiǎn)單。而FPGA的編程信息需存放在外部存儲(chǔ)器上,使用方法復(fù)雜。

⑥CPLD的速度比FPGA快,并且具有較大的時(shí)間可預(yù)測(cè)性。這是由于FPGA是門級(jí)編程,并且CLB之間采用分布式互聯(lián),而CPLD是邏輯塊級(jí)編程,并且其邏輯塊之間的互聯(lián)是集總式的。

⑦在編程方式上,CPLD主要是基于E2PROM或FLASH存儲(chǔ)器編程,編程次數(shù)可達(dá)1萬次,優(yōu)點(diǎn)是系統(tǒng)斷電時(shí)編程信息也不丟失。CPLD又可分為在編程器上編程和在系統(tǒng)編程兩類。FPGA大部分是基于SRAM編程,編程信息在系統(tǒng)斷電時(shí)丟失,每次上電時(shí),需從器件外部將編程數(shù)據(jù)重新寫入SRAM中。其優(yōu)點(diǎn)是可以編程任意次,可在工作中快速編程,從而實(shí)現(xiàn)板級(jí)和系統(tǒng)級(jí)的動(dòng)態(tài)配置。

⑧CPLD保密性好,FPGA保密性差。

⑨一般情況下,CPLD的功耗要比FPGA大,且集成度越高越明顯。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論