目前,圖像監控系統大多采用PC和視頻采集卡作為系統主要部分,基于嵌入式技術的圖像監控系統設備在我國還只是起步階段,沒有成熟的產品應用。這一現狀的根本原因就是我國在開發這類產品時,沒有統一的開發標準和共用的開發平臺,而且沒有可靠的功能和性能測試標準,各個企業的開發技術力量分散,極大的影響了該類產品開發的效率和可靠性。而制造出來的產品同國外同類產品相比,功能相差太大,沒有競爭力,市場基本上被國外公司所占領。因此,開發一個該類嵌入式系統勢在必行。

系統總體方案

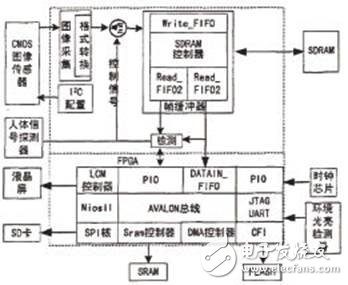

為了實現自動圖像報警和圖像采集,本文設計了動體檢測算法,這是因為絕大多數情況下我們只對監控區域中運動的物體感興趣,這樣可以過濾掉只包含靜態背景的圖像,從而降低了對有限的嵌入式硬件資源的消耗。由于活動物體大多是人,而且這也是圖像監控的目標,為此加入了人體信號探測器,用以輔助動體檢測,以達到降低圖像報警誤報率的目的。本系統主要集成了圖像采集、控制和存儲等器件或芯片,組成了以FPGA為控制核心的實時圖像監控系統。系統的總體方案如圖1所示。

圖1 圖像監控系統結構圖

系統工作流程為:系統上電后,FPGA從外部EEPROM自動加載程序,I2C模塊對CIS進行初始化工作參數配置。CIS向FPGA輸入圖像數據信號,FPGA將采集的原始數據(RAW)轉換成RGB格式,幀緩沖模塊(Frame Buffer)每次將相鄰兩幀圖像數據寫入SDRAM,然后比較這兩幀圖像的差值,如果差值大于設定的閾值,并且人體探測器輸出高電平,就認為檢測到了外界場景的運動,系統會自動將捕獲的圖像輸出到SD卡進行存儲。圖2給出了系統的工作流程。

圖2 系統工作流程圖

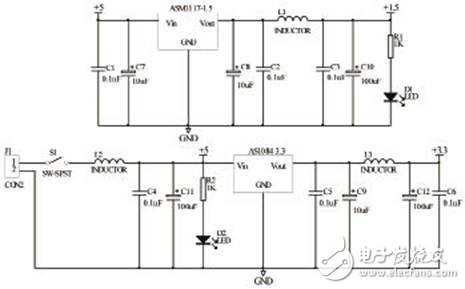

圖3 電源電路原理圖

系統硬件設計與實現

圖像監控系統處理的數據量較大,同時還要滿足實時性要求,因此板載電路需要選用容量較大,速度較快的器件。本系統采集的一幀圖像分辨率大小為640×480,色深是24位,檢測時需要在SDRAM緩存兩幀,因此SDRAM的容量必須大于1.8M字節(640×480×3×2=1843200字節),由于每個像素位寬為24位,同時NIOS是32位的處理器,所以SDRAM的位寬最好是32位。外部提供給FPGA的晶振頻率必須大于CIS的像素時鐘25MHz。考慮到檢測算法需要較多的邏輯資源,因此FPGA的片內LE要很豐富,另外FPGA的管腳必須要滿足外部器件連接的要求,在本系統中要實現所有器件的I/O口相連,FPGA的I/O管腳必須大于150個。由于電路原理圖較多,這里只給出其中的一部分。

主控制芯片電路

本系統選用的Cyclone系列FPGA器件的具體型號是EPlCl2Q240C8。邏輯資源達12060個邏輯單元(LE,Logic Elements),片內RAM的容量為239616bits。完全可以滿足圖像采集的設計要求。其內核供電采用1.5V、0.13um工藝,功耗較低。Cyclone器件支持各種單端I/O接口標準,如3.3V、2.5V、1.8V、LVTTL、LVCMOS、SSTL。Cyclone器件具有兩個可編程鎖相環(PLL)和八個全局時鐘線,提供健全的時鐘管理和頻率合成功能,實現最大的系統性能。Cyclone器件具有高級外部存儲器接口,允許設計者將外部單數據率(SDR)SDRAM,雙數據率(DDR)、SDRAM和DDR FCRAM器件集成到復雜系統設計中,而不會降低數據訪問的性能。Cyclone系列FPGA器件基于一種全新的低成本架構,從設計之初就充分考慮了成本的節省,因此可以為價格敏感的應用提供全新的可編程的解決方案。

電源電路

一般而言,FPGA器件出于芯片設計、多電平接口的需要,電源都分為兩組:VCCINT和VCCIO,即內核電源和I/O電源,隨著芯片內部連線尺度的逐漸減小,核心電源電壓和接口電壓也越來越低。本設計中EPlCl2器件的VCCINT為1.5V,VCCIO為3.3V。目前總的來說有三種電源解決方案,分別是線性穩壓器電源(LDO)、開關穩壓器電源和電源模塊。

LDO線性穩壓器適用于降壓變換,具體效果與輸入/輸出電壓比有關。從基本原理來說,LDO根據負載電阻的變化情況來調節自身的內電阻,從而保證穩壓輸出端的電壓不變。其變換效率可以簡單地看作輸出與輸入電壓之比。

由于采用線性調節原理,LDO本質上沒有輸出紋波。與LDO相比,DC/DC調整器輸出紋波電壓較大、瞬時恢復時間較慢、容易產生電磁干擾(EMI)。系統電源輸入電壓為5V,3.3V電壓供電部分采用了ASl084;此外,對于FPGA的PLL工作需要的1.5V電源部分,采用AMS1117-1.5 LDO來實現。

由于Altera的PLL是模擬電路實現的,其對電源噪聲比較敏感,所以在設計PCB的時候,對給PU的供電部分要做一些特殊的處理。即使在設計中沒有用到PLL也必須給其供電。

本系統中選用的EPlCl2F400C8芯片的輸入輸出接口電壓為3.3V,內核電壓降低到1.5V,這樣可以降低功耗,有利于系統的穩定,但也給電源供電和其它芯片的選擇帶來了麻煩,系統中其它芯片的接口電壓必須為3.3V,至少也要兼容3.3V,電源設計中需要考慮的主要問題是功率是否滿足的問題。

SD卡接口電路

在各種存儲設備中,SD卡不僅小巧,而且功耗很低,另外市面上常見SD卡的容量可達到2GB以上,因此非常適合用于對體積和功耗要求嚴格的嵌入式圖像存儲。如圖4所示,SPI的兩個數據線DAT0、CMD分別接上拉電阻,這是為了使本電路可以與MMC卡的接口兼容。卡的供電采用可控方式,這是為了防止SD/MMC卡進入不確定狀態時,可以通過對卡重新上電使卡復位而無需拔出卡。可控電路采用P型MOS管,由FPGA的GPIO口SDPC進行控制,當SDPC輸出高電平時,MOS管關斷,不給卡供電;當SDPC輸出低電平時,MOS管開通,VCC3V3電源給卡供電。考慮管子開通時,漏極與源極之間的壓降要足夠小(保證SD/MMC卡的工作電壓在允許范圍內),管子允許通過的電流也要滿足卡的要求,一般一張SD/MMC卡工作時的最大電流通常為45mA左右,所以選用的MOS管要求允許通過100mA左右的電流。采用2SJ355的目的是當它開通時,管子上的壓降比較小。

卡檢測電路包括兩部分:卡是否完全插入到卡座中和卡是否寫保護。檢測信號由卡座的兩個引腳以電平的方式輸出。當卡插入到卡座并插入到位時,SDIN(第10腳)由于卡座內部觸點連接到GND,輸出低電平;當卡拔出時,該引腳由于上拉電阻R2的存在而輸出高電平,該輸出由FPGA的輸入引腳來檢測。卡是否寫保護的檢測與卡是否完全插入到卡座中的檢測原理是一樣的。

圖像傳感器電路

圖像的輸入端的采集模塊是CMOS圖像傳感器,與CCD傳感器相比,CMOS傳感器不僅成本遠低于CCD產品。而且CMOS傳感器可輕松實現較高的集成度(比如CMOS被廣泛用于拍攝手機的微型攝像頭),另外CMOS傳感器擁有超低功耗的優點。本系統圖像采集用于監控領域,對于圖像的質量要求不是非常高,而對傳感器的功耗要求必須很低,而且可以直接輸出系統需要的數據格式,因此本系統的圖像采集部分選用了CMOS圖像傳感器。

在本設計中采用美光科技公司的MT9M011型號CMOS圖像傳感器,MT9M011是一塊SXGA(super extended graphics array,超大擴展圖像陣列)制式的1/3英寸主動式數字圖像傳感器,其有效圖像序列范圍為1280×1024,結合了眾多數碼照相機具有的功能如開窗取景、行列跳躍、快照模式等等,可以通過一個兩線的串口來實現可編程操作,并且具有功耗低的特點。片載A/D轉換器將提供每像素I/O位的輸出精度,幀有效和行有效信號將在特定的引腳上輸出,并且還配有像素時鐘同步響應的有效數據。

NiOS系統軟件設計及實現

本系統的軟件設計是以C語言形式在利用Altera公司的軟件集成開發工具IDE所提供的硬件配置模塊(HAL)的函數支持下來完成編寫的。系統啟動后,進行初始化工作,初始化程序主要完成初始化DMA通道及清FIFO控制接口的FIFO緩沖器等。隨后系統進入主循環狀態,并檢測按鍵。當檢測到DETECT時,啟動FIFO控制接口開始保存數據,當檢測到data_avaible有效時,啟動一次DMA傳輸。如此循環,直到檢測到SAVE_DONE為止,就實現了圖像數據的采集功能。

UART傳輸程序設計

uart傳輸程序主要是將圖像數據傳輸到電腦進行顯示,用于調試。在PC端,通過串口接收工具和Matlab將圖像顯示出來。Nios II系統中,可以通過ANSI C文件操作的標準庫函數來執行UART傳輸(uart 0),即將UART作為文件來處理。執行過程為:打開外設UART并獲得外設旬柄——fopen();向外寫入數據——fWrite();關閉外設——fclose()。

SD存儲卡的程序設計

SD卡程序設計包括驅動程序和文件系統兩部分設計。兩部分通過文件系統的接口函數相連接。驅動程序包括硬件配置模塊和命令應用模塊。硬件配置模塊包括訪問SD卡的硬件環境配置、SPI接口實現通訊的基本函數、內存變量初始化以及SPI中斷的處理。命令應用模塊提供訪問SD卡的讀數據函數和寫數據函數。

結論

本文主要完成了嵌入式圖像監控系統的設計,該系統克服了模擬圖像監控技術具有的弊端,在普通家庭、臨時性作業場所中具有很強的應用前景。這些領域一般對視頻傳輸指標的要求不一定很高,但要求便于攜帶,同時功耗較小(例如臨時性場合等),具有體積小、功耗低、成本低、速度快、穩定性好等特點,可以有效地克服傳統的基于計算機的監控系統的缺點。系統可做為一個智能部件“嵌入”到各種應用系統中,如將其配上網絡接口接上計算機系統,即可構成一個監控網絡系統,是一種相對獨立的OEM部件。

電子發燒友App

電子發燒友App

評論