引言

隨著時代和技術的發展,對于數據總線帶寬的要求越來越高,現有的總線標準越來越難以滿足實際應用中對高總線速率的要求。先進的總線技術對于解決系統的瓶頸,提高系統性能起著至關重要的作用,同時為了實現批量數據的傳輸,IEEE又公布了支持更高傳輸速率的IEEE Std 1394b-2002(簡稱1394b)串行總線標準,高速可升級性可支持高達800 Mb/s下的數據傳輸速率,并且能夠向后兼容先前的1394-1995和1394a標準。由于1394b是一種數據傳輸速率更高的串行總線標準,支持異步傳輸和等時傳輸兩種傳輸方式。分層的軟件和硬件模型可使其通信建立在事務層、鏈路層和物理層協議的基礎之上。本文充分利用FPGA和DSP芯片的硬件資源,基丁1394b傳輸協議和規范的基礎上,介紹139 4b數據傳輸系統的硬件設計結構、系統的工作流程和總線的配置過程。

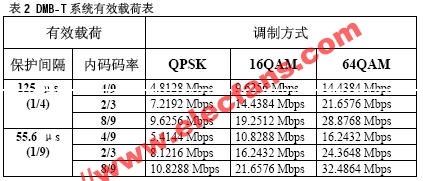

1 1394b的特點

1394b雙向數據傳輸系統的主要特點如下:

(1)高速可升級:支持100 Mb/s、200 Mb/s、400 Mb/s和800 Mb/s的傳輸速率,使用塑料光纖時可以提高到3.2 Gb/s;

(2)支持點到點傳輸:各個節點可脫離主機自主執行事務;

(3)即插即用:可以在任何時候向1394b網絡添加或移除設備,既不用擔心會影響數據的傳輸,也不需要進行重新配置,總線會重新枚舉,節點也可以自動配置,無需主機干預;

(4)熱插拔:無需將系統斷電就可以加入或移除設備;

(5)傳輸距離:采用CAT-5UTP5線(5類非屏蔽雙絞線)時,可以保證傳輸速率在100 Mb/s的前提下將傳輸距離延長至100 m,使用玻璃光纖時可在3.2Gb/s的前提下延長至50 m;

(6)支持兩種傳輸方式:包括等時(Isochronous)和異步(Asynchronous)數據傳輸方式;

(7)拓撲結構:設備間采用樹形或菊花鏈拓撲結構,每條總線最多可以連接63臺設備;

(8)可提供電源:一些低功耗設備可以通過總線取得電源,而不必為每一臺設備配置獨立的供電系統;

(9)公平仲裁:等時傳輸具有較高的優先級,同時異步傳輸也能獲得對總線的公平訪問;

(10)提高系統性能:將資源看作寄存器和內存單元,可以按照CPU內存的傳輸速率進行讀/寫操作,因此具有高速傳輸能力。

2 1394b數據傳輸系統的硬件實現

由于1394b鏈路層芯片必須通過PCI總線接口與FPGA進行相連,實現數據的傳輸。如果只用FPGA和DSP來實現對PCI外設的控制,需要設計復雜的接口邏輯,在1394b高速數據傳輸系統中不僅會影響FPGA本身的性能,而且會給FPGA之外的電路或者系統帶來諸多問題。因此這里采用PCI9054總線接口芯片配合FPGA和DSP來實現1394b雙向數據傳輸系統,將對復雜的PCI總線接口的控制轉換為對相對簡單的本地總線接口的控制,不僅對PCI協議有著良好的支持,而且提供給設計者良好的接口,大大減少了設計者的工作量。PCI9054芯片在PCI總線端支持32位/33 MHz,當本地總線端采用32位數據總線時,其數據傳輸速率可達132 MB/s,故能夠滿足1394b總線上800 Mb/s的數據傳輸速率要求。

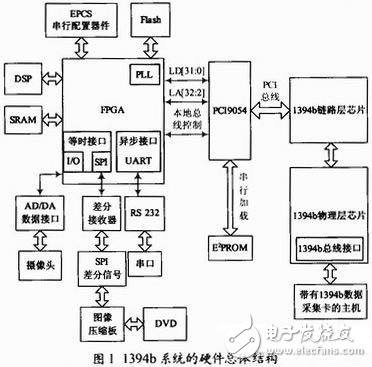

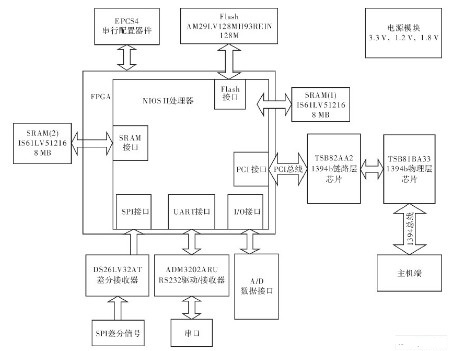

本設計中的主控芯片采用Altera公司的EP2C70F672C6型FPGA主流芯片,DSP選用TI公司的TMS320C6415 DSP芯片,1394b套片選用TI公司的鏈路層芯片TSB82AA2和物理層芯片TSB81BA3,PCI9054采用PLX公司的32位33MHz的PCI總線通用接口芯片。1394b雙向數據傳輸系統的硬件總體結構圖如圖1所示,主要由現場可編程門陣列(FPGA)模塊、DSP模塊、AD/DA數據轉換接口模塊、SPI數據輸入/輸出接口模塊、串口(UART)通信模塊、SRAM存儲模塊、EPCS串行配置器件模塊、FLASH存儲模塊、PCI9054模塊以及1394b套片模塊組成。

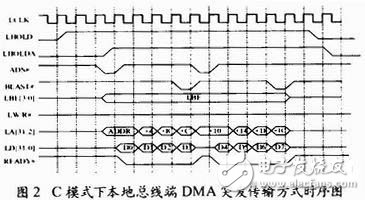

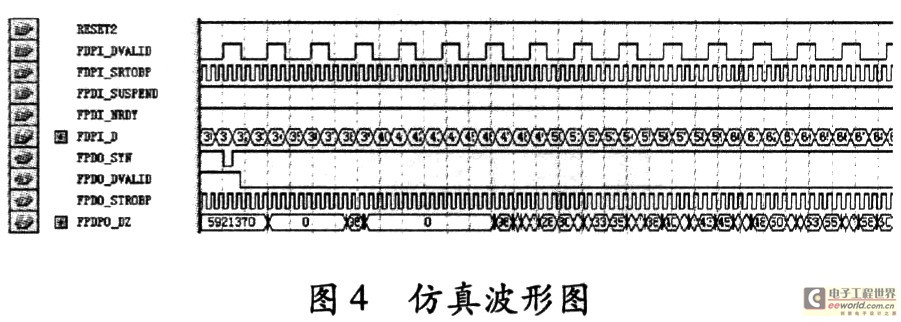

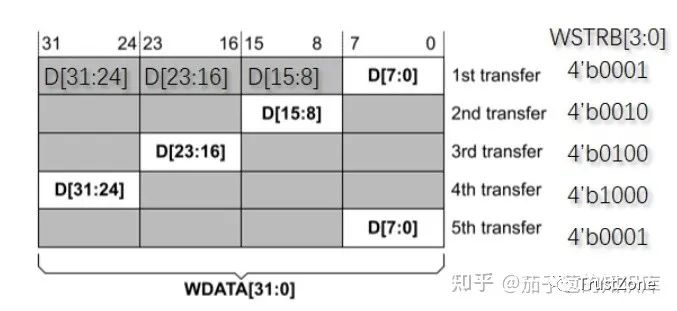

由于PCI9054內部可編程FIFO存儲器的存在,數據可以大批量突發傳輸而不丟失,這樣不儀滿足實時性要求,同時可以根據用戶的需要采用與PCI時鐘異步的本地端時鐘,PCI9054本地總線工作在C模式時,通過芯片內邏輯控制,將PCI的數據線和地址線分開,很方便地為本地端總線工作時序提供各種方式。圖2所示為PCI9054在C模式下與FPGA相連的本地總線數據突發DMA傳輸方式的時序圖,其中,LCCLK為輸入時鐘信號,從圖2中可以看出,在本地端總線上讀寫數據時,可以不間斷地進行突發傳輸,當數據不能連續傳輸時,則可以插入等待狀態,這樣可以大大提高數據的吞吐量。

3 1394b數據傳輸系統的數據流向

由于1394b總線標準支持等時子事務和異步子事務兩類子事務,因此,其傳輸的數據類型分為等時數據和異步數據,等時傳輸將數量不定的數據按照規定的時間間隔向某個地址發送,對實時性要求較高,不需要返回確認信號;而異步傳輸是將數據傳送到特定的地址,對數據傳輸的準確性要求較高,需要接收端以多次握手的方式發送返回確認信號。在本系統中由DVD播放器發送的數據經圖像壓縮板壓縮后由SPI口傳入FPGA,或者由攝像頭發送的數據經過A/D轉換,再由FPGA的通用I/O口送入FPGA,兩者均為等時數據;而一些控制命令等異步數據則由串口送入FPGA,并經過DSP進行處理,DSP和FPGA相結合可以提高數據傳輸的效率。FPGA實現數據的串并轉換以及數據的拼接并對數據打包成符合1394b協議的數據包類型以及配置數據包的包頭信息,經過讀/寫FIFO并在外部的SRAM進行緩存,通過DMA仲裁模塊進行仲裁處理,用DMA這一快速數據傳輸機制將數據寫入PCI9054的FIFO中。PCI9054作為一種橋接芯片,在本地總線和PCI總線之間提供信息傳遞,通過PCI9054芯片將本地端數據總線標準轉換成能被1394b鏈路層芯片傳輸的PCI總線數據標準,再通過1394b的鏈路層芯片實現對等時和異步數據包的地址和信道號的解碼、數據校驗、數據分析等,最后由物理層芯片通過仲裁邏輯實現對總線的存取,并對本地節點要發送的數據進行編碼,由物理層芯片提供的電氣和機械接口將數據位發送到與之相連的1394b線纜上去,最終送入接有1394b板卡的主機進行DVD發送的數據解壓縮和播放,以便對攝像頭發送的視頻進行播放以及異步數據的顯示等操作。讀出的數據則由接有1394b板卡的主機發送,并通過1394b物理層芯片、1394b鏈路層芯片、FPGA、外部SRAM等進行數據處理,根據數據包類型由相應的端口送出去,在這期間與發送數據相比進行了相反的操作,這樣就實現了1394b雙向數據傳輸系統。

FPGA作為整個系統的控制管理模塊,主要完成以下任務:

(1)對SPI端口、UART端口和AD/DA端口數據的發送和接收;

(2)將待發送的數據進行串并轉換和數據拼接;

(3)將數據進行打包、解包處理并通過SRAM進行數據的緩存;

(4)與PCI9054芯片進行通信,以完成數據的傳送。

本系統中DSP的主要功能是:

(1)與PCI9054芯片和1394b鏈路層芯片通信實現設備的自舉和身份的確認;

(2)發送和接收一些控制命令,控制數據的傳輸;

(3)實現異步數據的發送和接收功能,根據異步請求數據的類型對其進行相應的處理;

(4)為等時傳輸申請等時信道和帶寬,傳輸后釋放所申請的信道和帶寬。

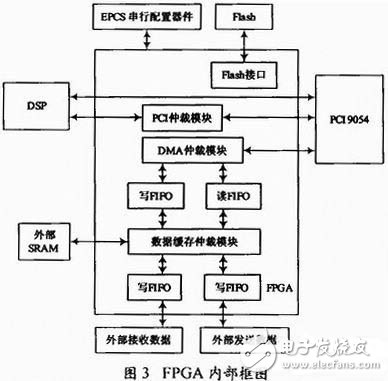

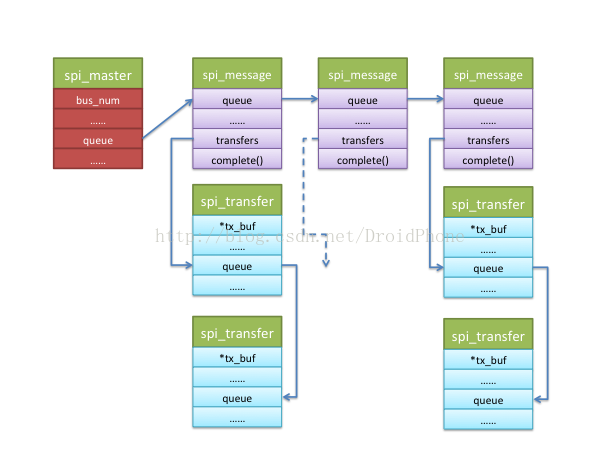

圖3所示是系統中FPGA的內部框圖,由于數據傳輸速率較快,數據的處理需要一定的時間,不能將每一組數據無間斷的傳輸,且FPGA內部FIFO容量有限,采用SRAM與FPGA相結合完成輸入輸出數據的緩存;DSP實現一些輔助的操作如對異步數據的處理、配置PCI9054芯片的內部寄存器和1394b鏈路層寄存器等操作以及PCI的傳輸控制、設備識別、為等時傳輸申請信道和帶寬等;EPCS串行配置芯片實現配置數據的存儲,使系統上電后將配置數據自動下載到FPGA內部,同時可以用FLASH存儲器存放DSP用戶代碼,在DSP上電工作后,利用DSP提供的boot機制,再將程序下載到DSP RAM中,使本系統實現脫機工作。

4 1394b的系統工作流程

1394b總線的配置是自動進行的,它不受任何設備和主機的干擾。總線配置過程主要有三個步驟:

(1)總線初始化;

(2)自標識;

(3)樹標識。

在這三個過程之后,整個系統在邏輯上形成了樹狀拓撲結構,每個節點都被賦予了一個節點號并都發出節點說明信息。總線的初始化過程如下:

(1)設備識別:設備識別可通過E2PROM來完成;

(2)分配I/O空間和Memory空間;

(3)配置PCI9054的DMA寄存器;

(4)對1394b鏈路層和物理層芯片進行配置。

由于1394b OHCI(Open Host Control Interface Specification)協議是1394b串行總線鏈路層協議的一種實現方式。1394bOHCI協議規定1394b的等時傳輸和異步傳輸均為DMA方式,所以需要對PCI9054的DMA寄存器進行配置。PCI9054中有兩個獨立的通道采用DMA方式傳輸數據可以不受主機的干預,同時采用突發方式傳輸數據可以提高數據的傳輸速率,同時也可以充分發揮PCI總線的性能。

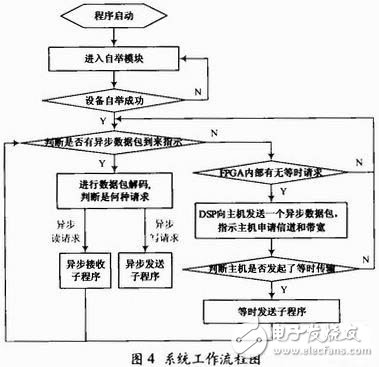

系統上電后,通常需要進行設備的自舉,協助主機完成設備識別和設備身份的確認,設備的自舉主要包括:初始化鏈路層寄存器;初始化配置ROM;判斷電纜是否插入;強制根節點;響應根節點、讀取配置ROM請求直到根節點調用相應驅動程序完成設備識別。圖4所示為本系統的工作流程圖。

設備自舉完成以后,即可等待數據包的到來,根據數據包的類型,如果是異步數據包則進行相應的處理;如果是等時數據包則進行等時信道和帶寬的申請,申請成功后則配置DMA寄存器以DMA方式進行等時數據的發送或等時數據的接收,等時數據傳輸完畢后釋放其信道和帶寬,這樣完成一次數據的傳輸,接下來進行下一次數據的傳輸,如此循環完成整個數據的傳輸。

5 結束語

IEEE 1394b作為一種與平臺無關的技術,可以同時應用在MAC和PC中,本文研究的主要內容是利用FPGA、DSP和PCI9054芯片實現1394b數據傳輸系統。現在國內基本上還停留在1394或1394a總線數據的傳輸上,本系統是在前人的基礎上,實現1394b總線上的數據傳輸,同時本系統兼容1394a實現1394的傳輸,還可以將傳輸速率提高作為驗證1394b協議的通用平臺,1394b能提供800 Mb/s或更高的傳輸速度,雖然市面上還沒有1394b接口的光儲產品出現,但相信在不久之后也必然會出現在用戶眼前,無論是在視頻傳輸還是在計算機外設、網絡互連等方而,都將有廣闊的市場。

電子發燒友App

電子發燒友App

評論