對(duì)于從FPGA外部進(jìn)來的信號(hào),我們通常采用“異步復(fù)位同步釋放的策略”,具體電路如下圖所示。

2023-07-20 09:04:21 1219

1219

“全局時(shí)鐘和第二全局時(shí)鐘資源”是FPGA同步設(shè)計(jì)的一個(gè)重要概念。合理利用該資源可以改善設(shè)計(jì)的綜合和實(shí)現(xiàn)效果;如果使用不當(dāng),不但會(huì)影響設(shè)計(jì)的工作頻率和穩(wěn)定性等,甚至?xí)?dǎo)致設(shè)計(jì)的綜合、實(shí)現(xiàn)過程出錯(cuò)

2023-07-24 11:07:04 655

655

(10)FPGA跨時(shí)鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時(shí)鐘域處理5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè)FPGA初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。這里主要介紹三種跨時(shí)鐘域

2021-03-04 09:22:51

摘要:FPGA異步時(shí)鐘設(shè)計(jì)中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個(gè)必須考慮的問題。本文介紹了FPGA異步時(shí)鐘設(shè)計(jì)中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時(shí)根據(jù)實(shí)踐經(jīng)驗(yàn)給出了解決這些問題的幾種同步策略。關(guān)鍵詞

2009-04-21 16:52:37

換、流水線操作及數(shù)據(jù)同步等;第三階段 時(shí)序理論基本模型;時(shí)序理論基本參數(shù);如何解決時(shí)序中的問題:關(guān)鍵路徑的處理;跨時(shí)鐘域的處理:異步電路同步化;亞穩(wěn)態(tài)的出現(xiàn)及解決方法;利用QuarutsII提供的時(shí)序

2012-09-13 20:07:24

FPGA設(shè)計(jì)中有多個(gè)時(shí)鐘域時(shí)如何處理?跨時(shí)鐘域的基本設(shè)計(jì)方法是:(1)對(duì)于單個(gè)信號(hào),使用雙D觸發(fā)器在不同時(shí)鐘域間同步。來源于時(shí)鐘域1的信號(hào)對(duì)于時(shí)鐘域2來說是一個(gè)異步信號(hào)。異步信號(hào)進(jìn)入時(shí)鐘域2后,首先

2012-02-24 15:47:57

EDA技術(shù)具有什么特征?FPGA是什么原理?FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略基于VHDL的FPGA系統(tǒng)行為級(jí)設(shè)計(jì)

2021-04-15 06:33:58

問題,異步時(shí)鐘域同步化是FPGA設(shè)計(jì)者最基本的技能。[size=11.818181991577148px]我發(fā)現(xiàn)很多初學(xué)者沒有進(jìn)行同步化處理,設(shè)計(jì)的案例也能工作。[size

2014-08-13 15:36:55

同一個(gè)時(shí)鐘域中。如果時(shí)鐘是非整數(shù)除法,它們不在同一個(gè)時(shí)鐘域中,或者來自不同的源(即使它們具有相同的時(shí)鐘頻率)

在將信號(hào)同步到 FPGA 或不同的時(shí)鐘域時(shí),有多種設(shè)計(jì)可供選擇。在xilinx fpga中

2023-11-03 10:36:15

時(shí)鐘,并且需要處理跨時(shí)鐘域問題(在視頻應(yīng)用中尤其常見)。這意味著我們有一個(gè)復(fù)雜的時(shí)鐘環(huán)境——一個(gè)很容易出現(xiàn)時(shí)鐘錯(cuò)誤的環(huán)境。這將導(dǎo)致時(shí)序很難收斂或更產(chǎn)生糟糕的情況,例如引入無意的時(shí)鐘域交叉錯(cuò)誤,從而導(dǎo)致

2022-10-08 15:28:35

設(shè)計(jì)包含 8 個(gè)讀寫模塊,這 8 個(gè)讀寫模塊需要訪問 8 個(gè) GDDR6 通道,這樣就需要一個(gè) 8x8 的 AXI interconnect 模塊,同時(shí)需要有跨時(shí)鐘域的邏輯去將每個(gè) GDDR6 用戶接口時(shí)鐘

2020-09-07 15:25:33

你好,我在Viv 2016.4上使用AC701板。我需要同步從一個(gè)時(shí)鐘域到另一個(gè)時(shí)鐘域的多位信號(hào)(33位)。對(duì)我來說,這個(gè)多位信號(hào)的3階段流水線應(yīng)該足夠了。如果將所有觸發(fā)器放在同一個(gè)相同的切片

2020-08-17 07:48:54

基站的內(nèi)部,都有自己獨(dú)立的時(shí)鐘模塊:晶振(晶體振蕩器),在沒有外部時(shí)鐘源時(shí),就處于自由震蕩狀態(tài)。

可想而知,在自由震蕩狀態(tài)的各個(gè)基站間的時(shí)鐘沒有同步,每個(gè)基站都只是一個(gè)孤島,只能獨(dú)立運(yùn)行無法協(xié)同

2023-05-10 17:09:50

同步是基本需求,那么時(shí)鐘同步怎樣組網(wǎng)?

2021-03-11 07:48:34

出現(xiàn)了題目中的跨時(shí)鐘域的同步問題?怎么辦?十年不變的老難題。為了獲取穩(wěn)定可靠的異步時(shí)鐘域送來的信號(hào),一種經(jīng)典的處理方式就是雙寄存器同步處理(double synchronizer)。那為啥要雙寄存器呢

2020-08-20 11:32:06

->Core Cock Setup:pll_c0為(Latch Clock) 這兩個(gè)是跨時(shí)鐘域時(shí)鐘,于是根據(jù)文中總結(jié):對(duì)于跨時(shí)鐘域的處理用set_false_path,約束語句如下

2018-07-03 11:59:59

1、IC設(shè)計(jì)中的多時(shí)鐘域處理方法簡析我們?cè)贏SIC或FPGA系統(tǒng)設(shè)計(jì)中,常常會(huì)遇到需要在多個(gè)時(shí)鐘域下交互傳輸?shù)膯栴},時(shí)序問題也隨著系統(tǒng)越復(fù)雜而變得更為嚴(yán)重。跨時(shí)鐘域處理技術(shù)是IC設(shè)計(jì)中非常重要的一個(gè)

2022-06-24 16:54:26

的特色之一,但MDO4000 絕不是以上羅列的五種測(cè)試工具的簡單組合,這五種功能工作在同一時(shí)鐘、同一觸發(fā)機(jī)制下,使得MDO4000 具有創(chuàng)新的時(shí)域、頻域、調(diào)制域時(shí)間相關(guān)的跨域分析功能。為此,我們將

2019-07-19 07:02:07

在看u***,書上說u***數(shù)據(jù)包的同步域可以同步主機(jī)端和從機(jī)端的時(shí)鐘,這個(gè)怎么理解u***接口沒有時(shí)鐘線,我又想到了單片機(jī)串口的波特率,不知道有沒有關(guān)系,向大家請(qǐng)教了這個(gè)簡單的問題,很想知道答案

2019-07-02 18:06:13

如何克服ajax跨域

2020-04-30 13:25:07

雙口RAM如何實(shí)現(xiàn)跨時(shí)鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。[hide] [/hide]

2012-03-05 14:42:09

跨越時(shí)鐘域FPGA設(shè)計(jì)中可以使用多個(gè)時(shí)鐘。每個(gè)時(shí)鐘形成一個(gè)FPGA內(nèi)部時(shí)鐘域“,如果需要在另一個(gè)時(shí)鐘域的時(shí)鐘域產(chǎn)生一個(gè)信號(hào),需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標(biāo)志第3部分:穿越

2012-03-19 15:16:20

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè)FPGA初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。這里主要介紹三種跨時(shí)鐘域

2021-02-21 07:00:00

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè)FPGA初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。 這里主要介紹三種跨

2021-01-08 16:55:23

異步bus交互(一)— 兩級(jí)DFF同步器跨時(shí)鐘域處理 & 亞穩(wěn)態(tài)處理1.問題產(chǎn)生現(xiàn)在的芯片(比如SOC,片上系統(tǒng))集成度和復(fù)雜度越來越高,通常一顆芯片上會(huì)有許多不同的信號(hào)工作在不同的時(shí)鐘頻率

2022-02-17 06:34:09

位同步時(shí)鐘的提取原理是什么?位同步時(shí)鐘的提取電路該怎樣去設(shè)計(jì)?

2021-05-07 06:51:36

本帖最后由 zhihuizhou 于 2012-2-7 10:33 編輯

轉(zhuǎn)自特權(quán)同學(xué)。 特權(quán)同學(xué)原創(chuàng) 這邊列舉一個(gè)異步時(shí)鐘域中出現(xiàn)的很典型的問題。也就是要用一個(gè)反例來說明沒有足夠重視異步

2012-02-07 10:32:38

同一個(gè)時(shí)鐘域中,或者來自不同的源(即使它們具有相同的時(shí)鐘頻率)在將信號(hào)同步到 FPGA 或不同的時(shí)鐘域時(shí),有多種設(shè)計(jì)可供選擇。在xilinx fpga中,最好的方法是使用xilinx參數(shù)化宏,創(chuàng)建這些

2022-10-18 14:29:13

關(guān)于cdc跨時(shí)鐘域處理的知識(shí)點(diǎn),不看肯定后悔

2021-06-21 07:44:12

關(guān)于iFrame特性總計(jì)和iFrame跨域解決辦法

2020-05-15 14:26:43

關(guān)于異步時(shí)鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時(shí)鐘域吧?大俠幫解決下我的心結(jié)呀,我這樣的理解對(duì)嗎?

2012-02-27 15:50:12

不能滿足高性能嵌入式系統(tǒng)的要求。在此,提出一種雙向同步自適應(yīng)時(shí)鐘技術(shù),在仿真器與目標(biāo)處理器之間穩(wěn)定可靠地實(shí)現(xiàn)了跨時(shí)鐘域JTAG信號(hào)的雙向時(shí)序匹配,并在此基礎(chǔ)上設(shè)計(jì)了一種TCK時(shí)鐘信號(hào)產(chǎn)生算法,從而

2019-05-21 05:00:22

到數(shù)據(jù)。所以這種電路中的信號(hào),我們依然把他稱之為同步信號(hào)。在跨時(shí)鐘域時(shí),由于兩個(gè)時(shí)鐘之間沒有任何關(guān)系,無論怎么調(diào)整周期,都不一定能滿足下級(jí)寄存器采樣到數(shù)據(jù),肯定不能調(diào)成一致周期,那就變成了同步設(shè)計(jì)。例

2023-02-28 16:38:14

、野外試驗(yàn)以及生產(chǎn)應(yīng)用,證明結(jié)合FPGA技術(shù),時(shí)鐘恢復(fù)和系統(tǒng)同步技術(shù)在地震勘探儀器中具有獨(dú)到的優(yōu)勢(shì),其精度可達(dá)us級(jí),而且穩(wěn)定,實(shí)現(xiàn)方便。地震勘探儀器是一個(gè)高度集成的網(wǎng)絡(luò)采集系統(tǒng),在這些地震勘探儀器中

2019-06-18 08:15:35

的co-simulink 接口,將搭建的離散域控制模型進(jìn)行編譯,并自動(dòng)生成代碼,下載到FPGA,生成一個(gè)bit 流文件,將含有bit 文件的協(xié)議同仿真模塊與諧波電壓源的主電路連接。當(dāng)在Simulink

2018-10-18 16:33:25

域傳遞的信號(hào)有兩種,其一為控制信號(hào),其二為數(shù)據(jù)流信號(hào)。針對(duì)這兩種不同的信號(hào),分別采取不同方案遏制系統(tǒng)墮入亞穩(wěn)態(tài)。對(duì)控制信號(hào)采用同步器裝置,即在2個(gè)不同的時(shí)鐘域之間插入同步器;而對(duì)于不同獨(dú)立時(shí)鐘域之間

2011-09-07 09:16:40

時(shí)鐘)的邏輯。在真正的ASIC設(shè)計(jì)領(lǐng)域,單時(shí)鐘設(shè)計(jì)非常少。2、控制信號(hào)從快時(shí)鐘域同步到慢時(shí)鐘域與同步器相關(guān)的一個(gè)問題是來自發(fā)送時(shí)鐘域的信號(hào)可能在被慢時(shí)鐘域采樣之前變化。將慢時(shí)鐘域的控制信號(hào)同步到快時(shí)鐘域

2022-04-11 17:06:57

我想做多個(gè)FPGA的時(shí)鐘同步,目前的想法是用一個(gè)FPGA的內(nèi)部時(shí)鐘,復(fù)制到外接IO口,接到另一個(gè)FPGA的外部時(shí)鐘引腳,波形有較小的相移但是可以保證同步。想問一下可以復(fù)制多次,驅(qū)動(dòng)多個(gè)FPGA的同步嗎。對(duì)驅(qū)動(dòng)能力有什么要求?其中每一個(gè)FPGA都用的是一個(gè)EP4CE的最小系統(tǒng)板。

2019-01-21 15:07:41

數(shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。

2012-05-23 19:59:34

最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。 FPGA設(shè)計(jì)的第一步是決定需要什么樣的時(shí)鐘速率,設(shè)計(jì)中最快的時(shí)鐘將確定FPGA必須能處理的時(shí)鐘速率。最快時(shí)鐘速率

2015-05-22 17:19:26

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時(shí)鐘信號(hào)不僅用于監(jiān)測(cè)輸入碼元信號(hào),確保收發(fā)同步,而且在獲取幀同步及對(duì)接收的數(shù)字碼元進(jìn)行各種處理的過程中也為系統(tǒng)提供了一個(gè)基準(zhǔn)

2019-08-05 06:43:01

interconnect模塊,同時(shí)需要有跨時(shí)鐘域的邏輯去將每個(gè)GDDR6用戶接口時(shí)鐘轉(zhuǎn)換到邏輯主時(shí)鐘。除了圖1中的8個(gè)讀寫模塊外,紅色區(qū)域的邏輯都需要用FPGA的可編程邏輯去實(shí)現(xiàn)。 圖1 傳統(tǒng)FPGA實(shí)現(xiàn)架構(gòu)對(duì)于AXI

2020-10-20 09:54:00

在串行數(shù)據(jù)傳輸?shù)倪^程中,如何在FPGA中利用低頻源同步時(shí)鐘實(shí)現(xiàn)LVDS接收字對(duì)齊呢?

2021-04-08 06:39:42

跨時(shí)鐘域處理是 FPGA 設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè) FPGA 初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。這里主要介紹三種跨

2020-09-22 10:24:55

跨時(shí)鐘域處理是FPGA設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè)FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。在本篇文章中,主要

2021-07-29 06:19:11

跨時(shí)鐘域處理是什么意思?如何處理好跨時(shí)鐘域間的數(shù)據(jù)呢?有哪幾種跨時(shí)鐘域處理的方法呢?

2021-11-01 07:44:59

把握DCM、PLL、PMCD和MMCM知識(shí)是穩(wěn)健可靠的時(shí)鐘設(shè)計(jì)策略的基礎(chǔ)。賽靈思在其FPGA中提供了豐富的時(shí)鐘資源,大多數(shù)設(shè)計(jì)人員在他們的FPGA設(shè)計(jì)中或多或少都會(huì)用到。不過對(duì)FPGA設(shè)計(jì)新手來說,什么時(shí)候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

你好,我很難理解如何正確設(shè)計(jì)一個(gè)時(shí)鐘使能信號(hào),以促進(jìn)兩個(gè)同步時(shí)鐘之間的時(shí)鐘域交叉,其中一個(gè)是慢速,一個(gè)是快速。我所擁有的情況與下圖所示的情況非常相似(取自UG903圖5-18)。如何確保CLK2產(chǎn)

2019-04-15 08:36:30

我自己寫了一個(gè)FIFO,但是我總是不理解Paper中講的要把讀寫指針同步,如果我將兩個(gè)不同時(shí)鐘產(chǎn)生的讀寫地址直接比較,產(chǎn)生讀寫,請(qǐng)問這個(gè)亞穩(wěn)態(tài)是怎么產(chǎn)生的,不要復(fù)制網(wǎng)上的那些東西,我都看了買就是不太

2016-04-11 23:13:45

親愛的朋友們, 我有一個(gè)多鎖設(shè)計(jì)。時(shí)鐘為50MHz,200MHz和400Mhz。如果僅使用400MHz時(shí)鐘并使用時(shí)鐘使能產(chǎn)生200Mhz和50Mhz時(shí)鐘域。現(xiàn)在我需要將信號(hào)從一個(gè)時(shí)鐘域傳遞到另一個(gè)

2019-03-11 08:55:24

你好 ,我有2個(gè)時(shí)鐘域(125和100MHz),我必須同步它們而不使用FIFO,請(qǐng)建議我一些替代方案。謝謝。問候sureshkumar

2020-06-17 11:43:12

跨時(shí)鐘域處理是 FPGA 設(shè)計(jì)中經(jīng)常遇到的問題,而如何處理好跨時(shí)鐘域間的數(shù)據(jù),可以說是每個(gè) FPGA 初學(xué)者的必修課。如果是還在校生,跨時(shí)鐘域處理也是面試中經(jīng)常常被問到的一個(gè)問題。這里主要介紹三種跨

2020-10-20 09:27:37

1 直接鎖存法控制信號(hào)從慢時(shí)鐘域到快時(shí)鐘域轉(zhuǎn)換時(shí),由于控制信號(hào)的有效寬度為慢時(shí)鐘域周期,需要做特殊處理,保證跨時(shí)鐘域后有效寬度為一個(gè)快時(shí)鐘周期,否則信號(hào)轉(zhuǎn)換到快時(shí)鐘域后可能被誤解釋為連續(xù)的多個(gè)控制

2016-08-14 21:42:37

我對(duì)使用源同步時(shí)鐘將大量數(shù)據(jù)從一個(gè)FPGA移動(dòng)到另一個(gè)FPGA感興趣。但由于設(shè)計(jì)的性質(zhì),我沒有很多可用的PLL,因此我無法發(fā)送許多時(shí)鐘數(shù)據(jù)對(duì)。假設(shè)所有跡線具有相同的延遲,是否可以將一個(gè)源同步時(shí)鐘與多個(gè)數(shù)據(jù)線相關(guān)聯(lián)?非常感謝你

2020-08-07 09:14:30

本文主要研究了一種基于FPGA、自頂向下、模塊化、用于提取位同步時(shí)鐘的全數(shù)字鎖相環(huán)設(shè)計(jì)方法。

2021-05-06 08:00:46

上圖是我的系統(tǒng)結(jié)構(gòu),FPGA使用AD產(chǎn)生的120M差分時(shí)鐘作為時(shí)鐘,通過一個(gè)DCM生成120M,240M的時(shí)鐘,使用DCM生成的時(shí)鐘作為AD采樣時(shí)鐘來采樣并行14bit差分?jǐn)?shù)據(jù)。每次修改了FPGA

2016-08-14 16:58:50

很多都是串轉(zhuǎn)并。。用10倍的時(shí)鐘(1KHZ)采樣。每個(gè)碼元采出來的10組數(shù)據(jù)。來判定類型。這個(gè)和我前面的設(shè)計(jì)思路哪個(gè)好點(diǎn)啊??我想著是1KHZ和IRIG_B是不同時(shí)鐘域的。會(huì)不會(huì)采樣不準(zhǔn)?有說利用PPS來同步這個(gè)1KHZ。但沒看懂怎么同步的。求解答。問題有點(diǎn)多。。謝謝了。。希望有人可以解答一下。。

2016-11-05 09:30:35

。StreamCCByToggleWithoutBuffer除了StreamCCByToggle,另一個(gè)握手處理跨時(shí)鐘域的例子便是StreamCCByToggleWithoutBuffer了:粗略一看,切莫以為只是少了一個(gè)

2022-07-07 17:25:02

知識(shí)轉(zhuǎn)移策略的跨域故障診斷背景轉(zhuǎn)移學(xué)習(xí)概述轉(zhuǎn)移學(xué)習(xí)方法研究動(dòng)機(jī)和問題設(shè)置跨域方法在故障診斷中的應(yīng)用開源故障數(shù)據(jù)集背景數(shù)據(jù)驅(qū)動(dòng)診斷方法的常用驗(yàn)證方式為通過將一個(gè)數(shù)據(jù)集分為訓(xùn)練集和測(cè)試集來保證這兩個(gè)

2021-07-12 07:37:58

transform to gray codereg[AddrWidth:0]wptr_gray1;reg[AddrWidth:0]rptr_gray1;//用寄存器輸出的原因是,因?yàn)樵?b class="flag-6" style="color: red">同步到另一個(gè)時(shí)鐘域

2016-07-04 16:48:19

1、高級(jí)FPGA設(shè)計(jì)技巧 有一個(gè)有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個(gè)設(shè)計(jì)最好采用唯一的時(shí)鐘域。換句話說,只有一個(gè)獨(dú)立的網(wǎng)絡(luò)可以驅(qū)動(dòng)一個(gè)設(shè)計(jì)中所有觸發(fā)器的時(shí)鐘端口

2022-10-14 15:43:00

域中添加同步器來避免亞穩(wěn)態(tài)問題。同步器允許振蕩在足夠的時(shí)間穩(wěn)定下來,并確保在目標(biāo)時(shí)鐘域獲得穩(wěn)定的輸出。一個(gè)常用的同步器是一個(gè)級(jí)聯(lián)觸發(fā)器,如下圖所示。該結(jié)構(gòu)主要用于設(shè)計(jì)中的控制信號(hào)和單比特?cái)?shù)據(jù)信號(hào)。多位

2022-06-23 15:34:45

)System Synchronous inputs系統(tǒng)同步輸入,指由同一時(shí)鐘傳輸和捕獲數(shù)據(jù),如下圖所示。上圖可以看出,FPGA和輸入源設(shè)備是同源的,共用一個(gè)系統(tǒng)時(shí)鐘。這一個(gè)系統(tǒng)時(shí)鐘在源設(shè)備觸發(fā)輸出數(shù)據(jù)

2019-07-09 09:14:48

小弟最近在研究FPGA時(shí)鐘資源的手冊(cè),遇到一個(gè)問題想請(qǐng)教各位大神。在Virtex6系列FPGA中,Bank分為top層和bottom層,請(qǐng)問我怎么查看一個(gè)Bank到底是在top層還是在bottom層

2015-02-10 10:30:25

Vue加入withCredentials后無法進(jìn)行跨域請(qǐng)求

2020-11-06 06:39:42

1、跨時(shí)鐘域信號(hào)的約束寫法 問題一:沒有對(duì)設(shè)計(jì)進(jìn)行全面的約束導(dǎo)致綜合結(jié)果異常,比如沒有設(shè)置異步時(shí)鐘分組,綜合器對(duì)異步時(shí)鐘路徑進(jìn)行靜態(tài)時(shí)序分析導(dǎo)致誤報(bào)時(shí)序違例。 約束文件包括三類,建議用戶應(yīng)該將

2022-11-15 14:47:59

40Nginx的反向代理功能解決跨域問題

2019-10-10 10:58:03

單元(觸發(fā)器、同步RAM塊以及流水乘法器等)都使用同一個(gè)網(wǎng)絡(luò)作為時(shí)鐘。假如設(shè)計(jì)中所有的觸發(fā)器都使用一個(gè)全局網(wǎng)絡(luò),比如FPGA的主時(shí)鐘輸入,那么我們說這個(gè)設(shè)計(jì)只有一個(gè)時(shí)鐘域。假如設(shè)計(jì)有兩個(gè)輸入時(shí)鐘,如圖1

2023-06-02 14:26:23

在介紹了GPS 同步時(shí)鐘基本原理和FPGA 特點(diǎn)的基礎(chǔ)上,提出了一種基于FPGA 的GPS同步時(shí)鐘裝置的設(shè)計(jì)方案,實(shí)現(xiàn)了高精度同步時(shí)間信號(hào)和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 40

40 摘 要: 本文利用FPGA完成了8路同步話音及16路異步數(shù)據(jù)的復(fù)接與分接過程,并且實(shí)現(xiàn)了復(fù)接前的幀同步捕獲和利用DDS對(duì)時(shí)鐘源進(jìn)行分頻得到所需時(shí)鐘的過程。該設(shè)計(jì)

2009-06-20 13:38:43 565

565

大型設(shè)計(jì)中FPGA的多時(shí)鐘設(shè)計(jì)策略

利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率

2009-12-27 13:28:04 645

645

基于FPGA的提取位同步時(shí)鐘DPLL設(shè)計(jì)

在數(shù)字通信系統(tǒng)中,同步技術(shù)是非常重要的,而位同步是最基本的同步。位同步時(shí)鐘信號(hào)不僅用于監(jiān)測(cè)輸入碼元信號(hào),確保收發(fā)

2010-01-25 09:36:18 2890

2890

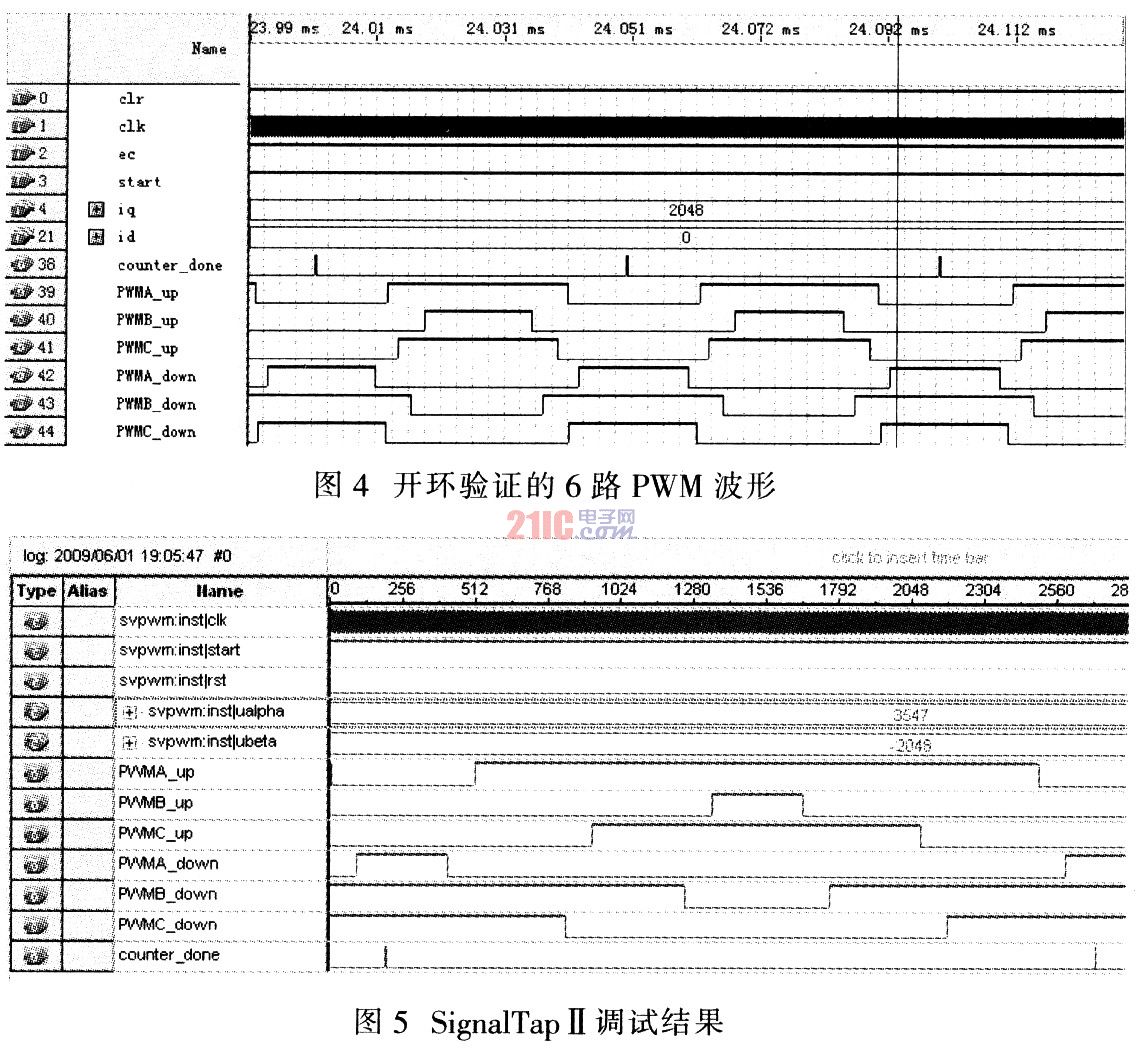

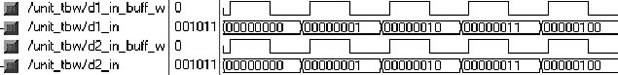

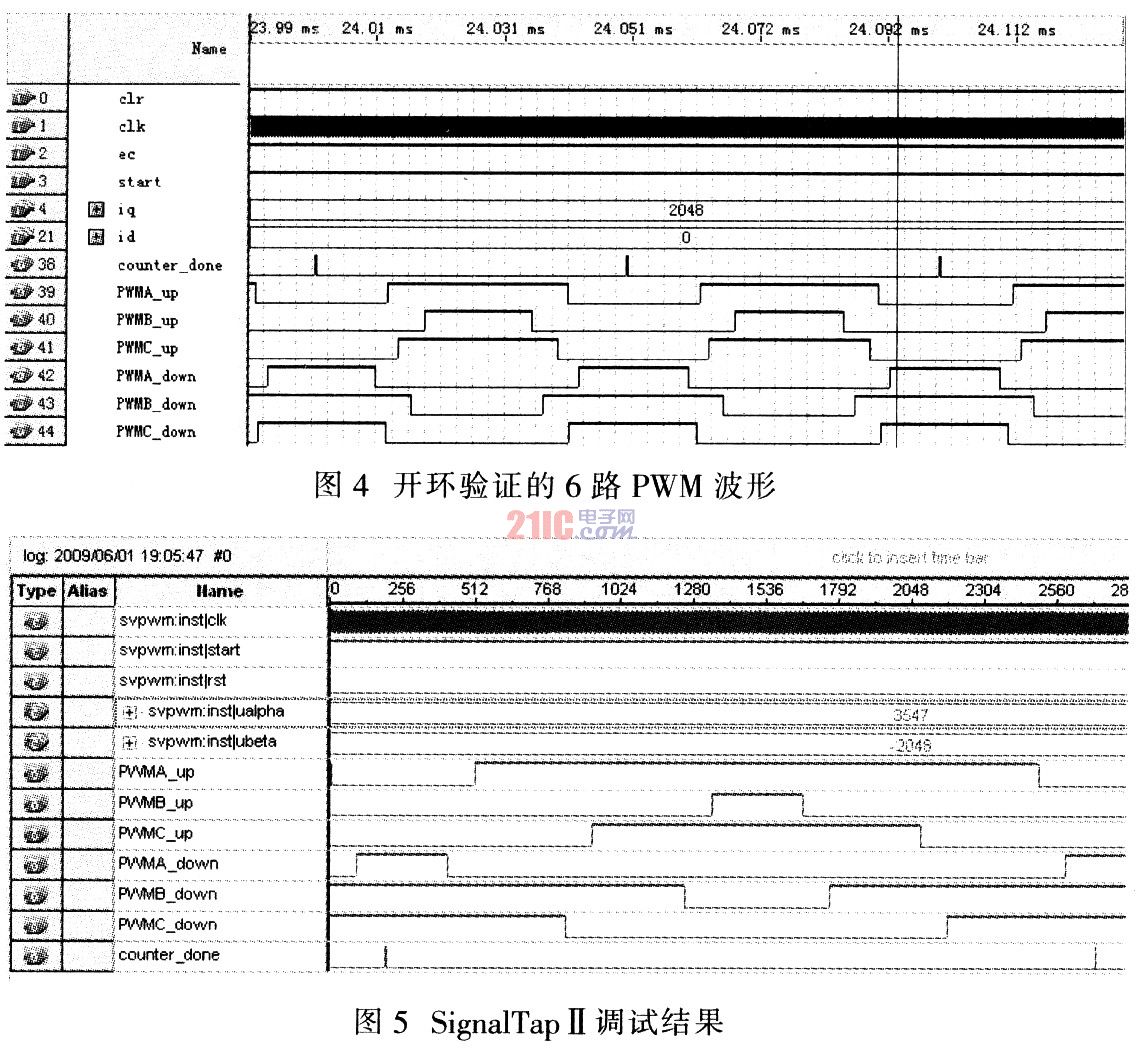

利用FPGA的永磁同步電機(jī)控制器原理及設(shè)計(jì)

概述:提出一種基于FPGA的永磁同步電機(jī)控制器的設(shè)計(jì)方案,該設(shè)計(jì)可應(yīng)用于具有高動(dòng)態(tài)性能要求的永磁同

2010-03-17 11:43:08 2951

2951

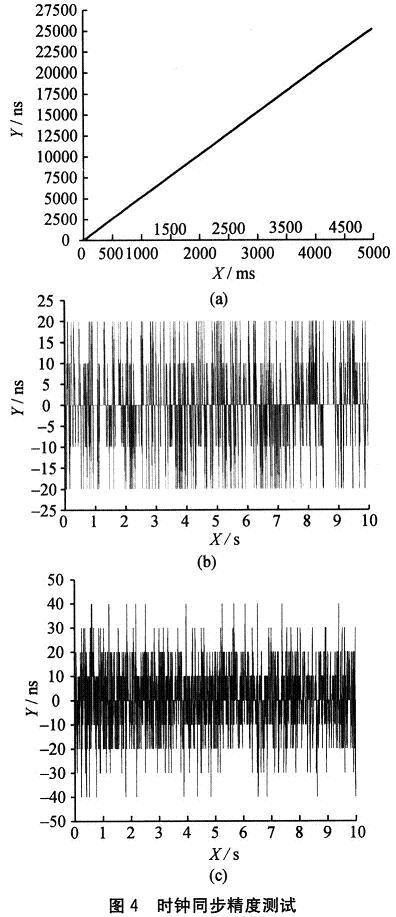

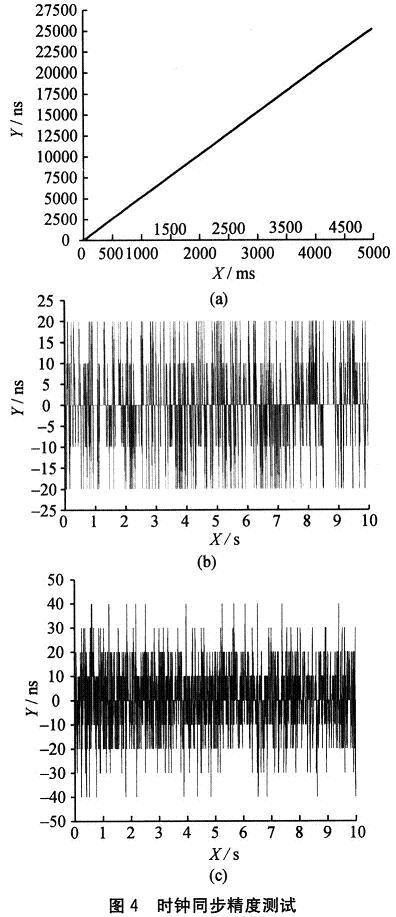

FPGA的時(shí)鐘頻率同步設(shè)計(jì)

網(wǎng)絡(luò)化運(yùn)動(dòng)控制是未來運(yùn)動(dòng)控制的發(fā)展趨勢(shì),隨著高速加工技術(shù)的發(fā)展,對(duì)網(wǎng)絡(luò)節(jié)點(diǎn)間的時(shí)間同步精度提出了更高的要求。如造紙機(jī)械,運(yùn)行速

2010-01-04 09:54:32 2762

2762

FPGA 異步時(shí)鐘設(shè)計(jì)中如何避免亞穩(wěn)態(tài)的產(chǎn)生是一個(gè)必須考慮的問題。本文介紹了FPGA 異步時(shí)鐘設(shè)計(jì)中容易產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象及其可能造成的危害,同時(shí)根據(jù)實(shí)踐經(jīng)驗(yàn)給出了解決這些問題的

2011-12-20 17:08:35 63

63 利用FPGA實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)

2012-05-21 11:26:10 1100

1100

介紹了精密時(shí)鐘同步協(xié)議(PTP)的原理。本文精簡了該協(xié)議,設(shè)計(jì)并實(shí)現(xiàn)了一種低成本、高精度的時(shí)鐘同步系統(tǒng)方案。該方案中,本地時(shí)鐘單元、時(shí)鐘協(xié)議模塊、發(fā)送緩沖、接收緩沖以及系統(tǒng)打時(shí)標(biāo)等功能都在FPGA

2017-11-17 15:57:18 6196

6196

基于FPGA的數(shù)字系統(tǒng)設(shè)計(jì)中大都推薦采用同步時(shí)序的設(shè)計(jì),也就是單時(shí)鐘系統(tǒng)。但是實(shí)際的工程中,純粹單時(shí)鐘系統(tǒng)設(shè)計(jì)的情況很少,特別是設(shè)計(jì)模塊與外圍芯片的通信中,跨時(shí)鐘域的情況經(jīng)常不可避免。如果對(duì)跨時(shí)鐘

2018-09-01 08:29:21 5302

5302

對(duì)于 FPGA 來說,要盡可能避免異步設(shè)計(jì),盡可能采用同步設(shè)計(jì)。 同步設(shè)計(jì)的第一個(gè)關(guān)鍵,也是關(guān)鍵中的關(guān)鍵,就是時(shí)鐘樹。 一個(gè)糟糕的時(shí)鐘樹,對(duì) FPGA 設(shè)計(jì)來說,是一場無法彌補(bǔ)的災(zāi)難,是一個(gè)沒有打好地基的樓,崩潰是必然的。

2020-11-11 09:45:54 3656

3656 利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。

2021-01-13 17:00:00 11

11 利用 FPGA 實(shí)現(xiàn)大型設(shè)計(jì)時(shí),可能需要FPGA 具有以多個(gè)時(shí)鐘運(yùn)行的多重?cái)?shù)據(jù)通路,這種多時(shí)鐘FPGA 設(shè)計(jì)必須特別小心,需要注意最大時(shí)鐘速率、抖動(dòng)、最大時(shí)鐘數(shù)、異步時(shí)鐘設(shè)計(jì)和時(shí)鐘/數(shù)據(jù)關(guān)系。設(shè)計(jì)過程中最重要的一步是確定要用多少個(gè)不同的時(shí)鐘,以及如何進(jìn)行布線,本文將對(duì)這些設(shè)計(jì)策略深入闡述。

2021-01-15 15:57:00 14

14 電子發(fā)燒友網(wǎng)為你提供時(shí)鐘同步怎樣組網(wǎng)?資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-16 08:43:28 11

11 時(shí)鐘信號(hào)的同步 在數(shù)字電路里怎樣讓兩個(gè)不同步的時(shí)鐘信號(hào)同步? 在數(shù)字電路中,時(shí)鐘信號(hào)的同步是非常重要的問題。因?yàn)樵谛盘?hào)處理過程中,如果不同步,就會(huì)出現(xiàn)信號(hào)的混淆和錯(cuò)誤。因此,在數(shù)字電路中需要采取一些

2023-10-18 15:23:48 771

771 fpga與dsp通訊怎樣同步時(shí)鐘頻率?dsp和fpga通信如何測(cè)試? 在FPGA與DSP通訊時(shí),同步時(shí)鐘頻率非常重要,因?yàn)椴煌脑O(shè)備有不同的時(shí)鐘頻率,如果兩者的時(shí)鐘頻率不同步,會(huì)導(dǎo)致通訊數(shù)據(jù)的錯(cuò)誤

2023-10-18 15:28:13 1060

1060 時(shí)鐘同步怎樣組網(wǎng)? 時(shí)鐘同步是計(jì)算機(jī)網(wǎng)絡(luò)中的重要問題,主要用于確保在多個(gè)節(jié)點(diǎn)之間保持時(shí)間的一致性。時(shí)鐘同步對(duì)于網(wǎng)絡(luò)的可靠性和性能至關(guān)重要,因此組網(wǎng)時(shí)時(shí)鐘同步必須仔細(xì)考慮。 在計(jì)算機(jī)網(wǎng)絡(luò)中,各個(gè)節(jié)點(diǎn)

2024-01-16 15:10:13 168

168

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論