引言

在地質勘探、工業環境監測、大型科學實驗等領域中需要將實時采集到的大量數據以較高的速率傳輸距離較遠,復雜而龐大的數據傳輸任務給傳輸系統的設計帶來極大的挑戰。目前常見的遠距離高速傳輸方案多采用較為復雜的光纖通道等方案,系統的成本、設計難度、體積和功耗都相對較大,限制了其應用場合。

LVDS(Low Voltage Differential Signaling)是一種小振幅差分信號技術,它允許單個信道傳輸速率達到每秒數百兆比特,其特有的低振幅及恒流源模式驅動只產生極低的噪聲,消耗非常小的功率。LVDS 是目前常見的高速數據傳輸方案,但其多用于芯片間、背板間或設備間進行近距離的數據傳輸。

本文中提出的高速數據遠距離傳輸系統方案以Altera 公司Cyclone III 系列低成本FPGA 芯片EP3C5E144C8 的為核心,以LVDS 信號為基礎,通過增加信道編碼、數據時鐘恢復、預加重和均衡等技術,保證了數據傳輸的穩定性和同步性。保證采用UTP-5 雙絞線為傳輸介質時傳輸速率不低于400Mbps,傳輸距離為50 米時上的,實現低成本的遠距離高速數據傳輸。

1、方案總體設計

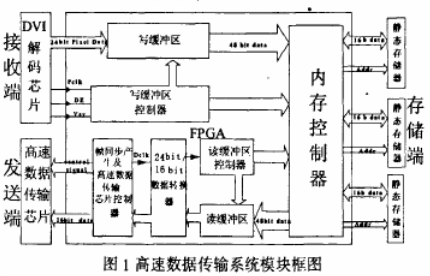

LVDS 信號一種低振幅高速差分信號,由于其電氣特性決定了其傳輸距離有限。為了滿足系統使用UTP-5 雙絞線實現距離50m 的數據傳輸要求,需要通過增加預加重和均衡技術來恢復線路上傳輸的信號波形。由于傳輸距離較遠且傳輸速率較高,無法直接采用傳送位時鐘信號和幀同步脈沖來保證系統同步。本系統采取接收端從接收數據中恢復時鐘信號的方法簡化系統設計方案。

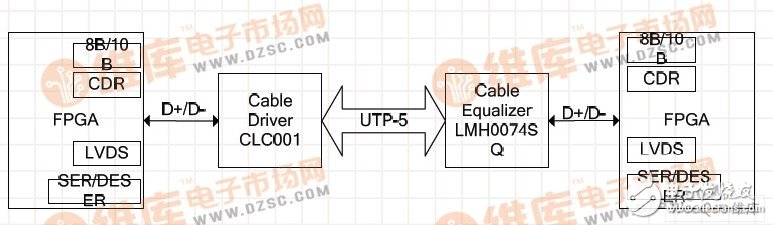

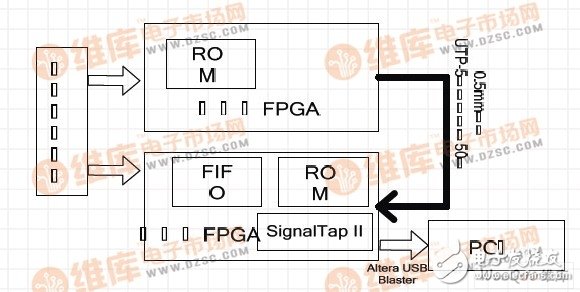

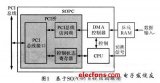

系統整體設計框圖如圖1 所示,整個系統的核心模塊包括了8B/10B 編碼、CDR(時鐘恢復)、并-串/串-并轉換模塊、LVDS 接口電路、電纜驅動器(Cable Driver)和電纜均衡器(Cable Equalizer)等。數據在發送端的FPGA 內經過8B/10B 編碼,并-串轉換經LVDS 模式的I/O 端口轉化為LVDS 信號,然后經過線路驅動器芯片CLC001 預加重后,通過UTP-5 雙絞線傳出數據。接收端收到的信號經過均衡器芯片LMH0074SQ 均衡后進入FPGA,在接收端FPGA 內,數據先經過CDR 模塊提取時鐘信號,然后字對齊后經過串-并轉換產生并行數據流,最后經過8B/10B 解碼模塊得到傳輸數據。

整個系統除電纜驅動器和電纜均衡器采用專用芯片外其它功能均在FPGA內部實現,從而極大的減小了系統的復雜度和PCB 板的面積。

圖1 系統整體框圖

2.FPGA 關鍵模塊設計

FPGA 作為系統的核心芯片,根據系統整體方案的設計思路,FPGA 中含有的模塊主要有信道編解碼模塊、數據時鐘恢復模塊、串/并轉換模塊。

2.1 信道編解碼模塊

在高速數據傳輸過程中,為了使數據時鐘恢復模塊中的數字鎖相環能夠得到足夠充足的跳變沿信息,需要采用信道編解碼技術消除或減少數字電信號中的直流和低頻分量。8B/10B 編碼是其中最常用的一種編碼方式。

8B/10B 編碼被廣泛應用于多種高速串行通信協議中。它將8bits 的基帶信號映射成10bits 的數據進行發送,防止在基帶數據中過多的0 碼流或1 碼流。通過8B/10B 編碼可以提高數據在鏈路上的傳輸的性能;使接收器可以正確地恢復時鐘;提高碼流中一個或者多個比特錯誤的檢測能力;定義特定的碼元使接收器能夠正確地對齊碼元。在本系統中分別在兩塊FPGA 中實現了8B/10B 編碼模塊和8B/10B 解碼模塊。

8B/10B 編碼模塊如圖2 所示,該模塊在邏輯上又分成3B/4B 編碼模塊、5B/6B 編碼模塊、RD 控制模塊等3 部分。編碼器首先將接收到的8B 數據分成3 bit 和5 bit 兩部分,然后分別編碼成4 bit 和6 bit,編碼完成的4 bit 和6 bit 再按順序組合成10B 碼。整個系統首先將3 bit 編碼成4 bit,RD 控制器讀出4 bit 數據的RD 值,然后反饋控制5B/6B 編碼模塊選擇合適的編碼。最終RD 控制器判斷10B 數據的RD 值,若滿足要求則輸出,否則將報錯。

圖2 8B/10B 編碼模塊邏輯框圖

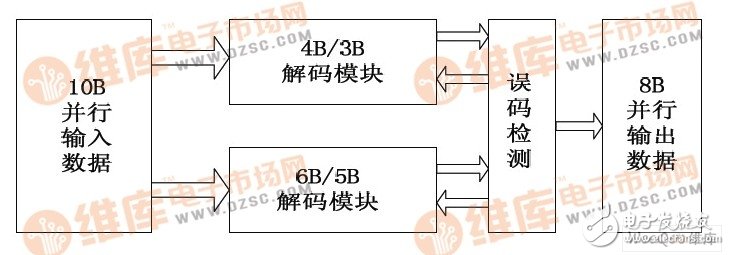

解碼模塊如圖3 所示,可分為6B/5B 解碼模塊、4B/3B 解碼模塊和誤碼檢測模塊。解碼模塊相對編碼模塊而言邏輯過程要簡單的多,該模塊首先將10 bit 信號分割成4 bit 和6bit 兩部分(高低位必須和編碼端對應),然后4 bit 和6 bit 數據根據編碼列表分別解碼成3 bit 和5 bit,在解碼過程中判斷是否有誤碼產生有則報錯,無則并行輸出。

圖3 8B/10B 解碼模塊邏輯框圖

2.2.數據時鐘恢復模塊

在單向數據傳輸中,串行通信通常需要同時提供數據、位時鐘、幀同步脈沖三路信號。在本系統說要求的高速率、長距離的數據傳輸要求下,這種三線連接方式不但浪費導線,而且往往受環境的影響很難實現三路信號間的同步。在本系統中由于輸入信號頻率已知,因此可以在FPGA 芯片內部產生與之同頻的時鐘信號。通過數字鎖相環電路鎖定輸入信號的相位,并使用此時鐘信號對輸入數據進行采樣,從而完成信號的接收。因而,利用數據時鐘恢復模塊可以從串行位流數據中恢復出接收位同步時鐘、幀同步脈沖和接收的數據。

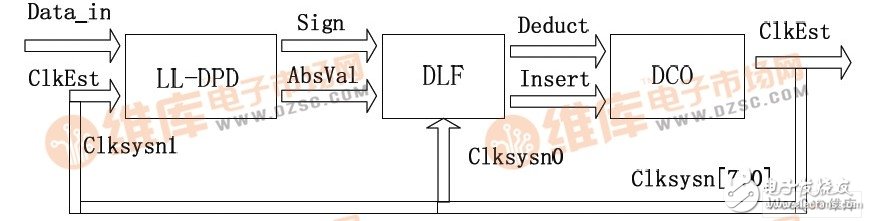

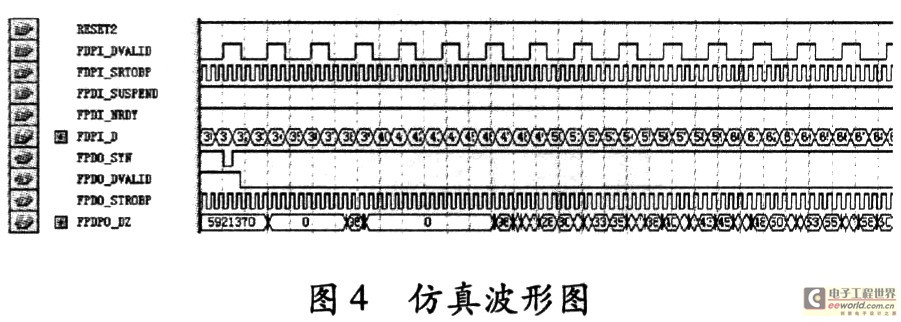

數字鎖相環(DPLL)是一種相位反饋控制系統。它根據輸入信號與本地估算時鐘之間的相位誤差對本地估算時鐘的相位進行連續不斷的反饋調節,從而達到使本地估算時鐘相位跟蹤輸入信號相位的目的。DPLL 通常有三個組成模塊:數字鑒相器(DPD)、數字環路濾波器(DLF)、 數控振蕩器(DCO)。根據各個模塊組態的不同,DPLL 可以被劃分出許多不同的類型。根據設計的要求,本文采用超前滯后型數字鎖相環(LL-DPLL)作為解決方案,圖5 是其實現結構。在LL-DPLL 中,DPD 采用微分型超前-滯后數字鑒相器,DLF 用雙向計數邏輯和比較邏輯實現,DCO 采用加扣脈沖式數控振蕩器。這樣設計出來的DPLL 具有結構簡潔明快,參數調節方便,工作穩定可靠的優點,其結構框圖如圖4 所示。

圖4 超前滯后型數字鎖相環

環路的工作原理如下:超前滯后型數字鑒相器LL-DPD 比較輸入位流數據DataIn 與本地估算時鐘ClkEst 的相位,給出相位誤差信號Sign 和AbsVal。DLF 對相位誤差信號進行平滑濾波,并生成控制DCO 動作的控制信號Deduct 和Insert。DCO 根據控制信號給出的指令,調節內部高速振蕩器的震蕩頻率,使其輸出時鐘ClkEst(同時反饋給LL-DPD)的相位跟蹤輸入數據DataIn 的相位。

3.板級電路設計

本系統核心芯片采用Altera 公司的Cyclone III 系列FPGA 中的EP3C5E144C8, Altera 公司的Cyclone III FPGA 系列組合了高性能,低功耗和低成本,邏輯單元(LE) 從5K 到200K,存儲器從0.5Mb 到8Mb,靜態功耗小于1/4 瓦.

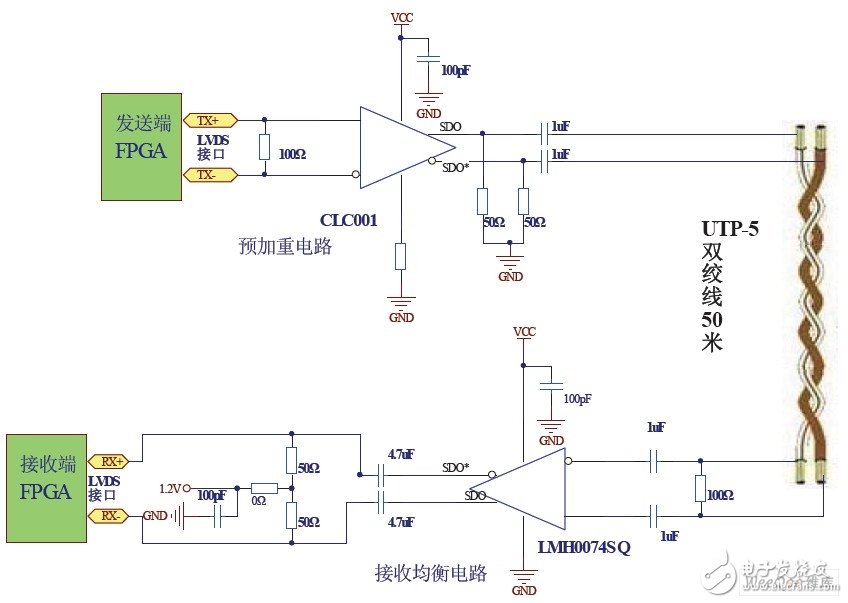

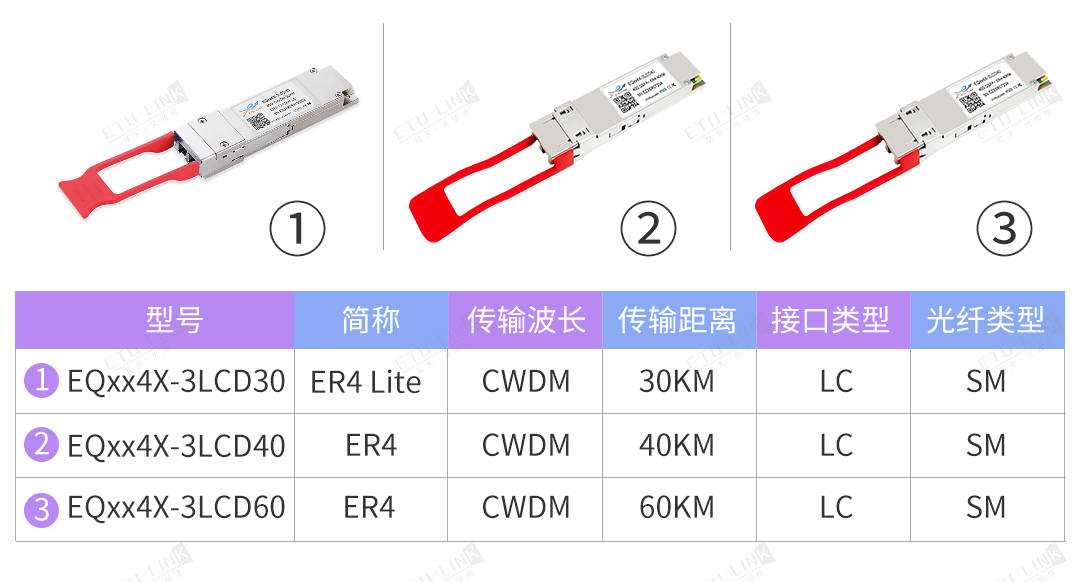

由于設計要求達到高速率、50 米的傳輸距離,傳統的LVDS 接口雖然可以達到較高的傳輸速率卻不能支持長距離傳輸。所以本系統采用高速串行數字接口(SDI)自適應電纜均衡器及電纜驅動器芯片來實現數據高速率、長距離的傳輸。

預加重是在信號發送前對其進行預扭曲,以使接收器上的信號質量如同原始發送的質量。當信號在直流電平上保持超過一個比特的時間時,預加重就會抬高高頻分量而降低低頻分量。本文選用CLC001 電纜驅動芯片,CLC001 采用3.3V 供電,輸出幅度可調,理論數據速率最高可達622Mbps 。

接收均衡通過對輸入數據運用相對頻率特征來補償信號的損耗特征。本文選用LMH0074SQ 接收均衡芯片,LM0074SQ 是標準清晰度SDI 電纜均衡器,可在540 Mbps 的速度范圍內操作,輸出抖動典型值為0.2UI。

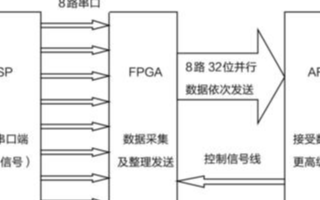

FPGA 外部電路如圖5所示,在發送端,FPGA 產生的LVDS 信號經CLC001 預加重后通過UTP-5 雙絞線傳輸;在接收端,信號先經過LMH0074SQ 均衡后隔直輸出。由于LVDS 接口電平標準要求輸入電壓直流偏置為1.2V,因此需要通過偏置電路在引入1.2V 的直流偏置后再傳給FPGA。

圖5 FPGA 外圍電路

4.數據測試及系統性能分析

4.1 系統測試方案

測試方案主要對系統的靜態功耗、動態功耗以及在50 米傳輸距離時的數據傳輸速率及相應的誤碼率進行測試。測試方案連接框圖如圖6所示。測試所用數據存在發送端例化的ROM 中,接收端FPGA 中例化有FIFO 和ROM,FIFO 用來存儲接收的數據,ROM 中則存儲有和發送端ROM 中相同的數據,用來計算誤碼率。同時,在接收端FPGA 中有接收數據計數器和錯誤比特計數器模塊,通過設置SignalTap II 的觸發信號和想觀察的信號,就可以在SignalTap II Logic Analyzer 的窗口中實時的看到這些信號。

圖6 系統測試方案

4.2 功耗測試

本系統通過直流穩壓電源供電,方便計算整個系統的功耗。經測試發現,在不同的傳輸速率時系統的功耗差別不大,動態功耗典型值為數據傳輸速率100Mbps 時,系統消耗電流0.24A,供電電壓3.3V,系統功耗為792mW。靜態功耗測量時,不發送數據,但保持50 米雙絞線接入,電流為0.20A,供電電壓為3.3V,靜態功耗為660mW。

4.3 誤碼率測試

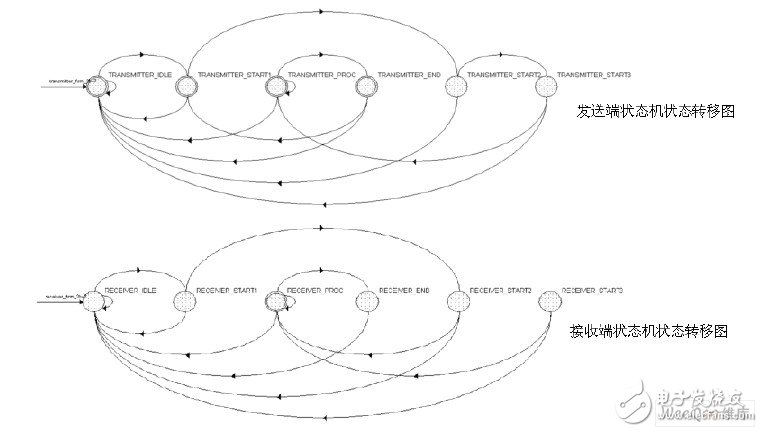

在發送端的FPGA 中采用ROM 來存儲數據,通過狀態機transmitter_fsm_3b 來控制數據的發送,狀態轉移圖如圖7上圖所示。接收端則采用FIFO 來存儲數據,同時接收端ROM 中存有和發送端相同的數據,以實現接受數據與原始數據的對比,計算誤碼率,接收端通過狀態機receiver_fsm_3b 來控制數據的接收以及誤碼率的計算,狀態轉移圖如圖7下圖所示。由于EP3C15F144C8 的RAM 大小總共只有512kbits,再加上signal tap 的開銷,所以例化的ROM 和FIFO 比較小,ROM 大小為8Kbyte,內部存儲數據由00H~FFH 一直重復,把一次ROM 數據的發送當成一個幀。每發送一次ROM 數據即比較一次FIFO 中與原始ROM 中的數據。重復發送20000 次,總bit 數等于20000 次*(8192*8)bit= 1469120000bit。因為接收端的數據時鐘恢復和字對齊需要一定的時間,因而實際成功重復次數不到20000 次,可通過專門的計數器來確定實際重復次數。

圖7 狀態機狀態轉移圖

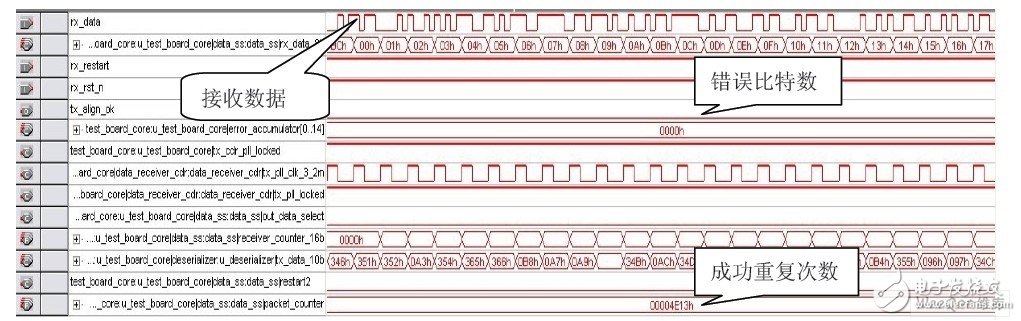

在接收端通過SignalTap II Logic Analyzer 實時查看接收數據rx_data、錯誤比特數error_accumulator 和成功重復次數packet_counter,圖8 為SignalTap II Logic Analyzer 接收數據的窗口顯示。誤碼率可通過式1 求得:

誤碼率=錯誤比特數/(成功重復次數×8192×8) (1)

圖8 SignalTap II Logic Analyzer 數據接收窗口顯示

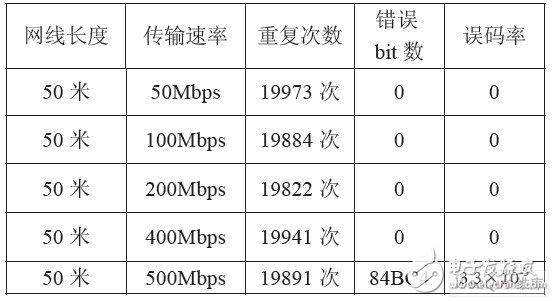

傳輸速率及相應誤碼率如表1 所示,在傳輸數據為400Mbps,傳輸距離為50 米是誤碼率仍為0。由于選用的均衡器LM0074SQ 的極限速率為540Mbps,因而在數據速率為500Mbps 時誤碼率急劇增大。

表1 傳輸速率及相應誤碼率

5.總結

本系統高速數據遠距離傳輸方案以Altera 公司的Cyclone III 系列EP3C5E144C8 為核心,使用LVDS 信號傳輸數據,通過信道編碼、數據時鐘恢復、預加重和均衡等技術的使用,保證了數據傳輸的穩定性和同步性,在傳輸速率為400Mbps,傳輸距離為50 米時,誤碼率為0。可以廣泛的應用于各種高速遠距離數據傳輸的場合。

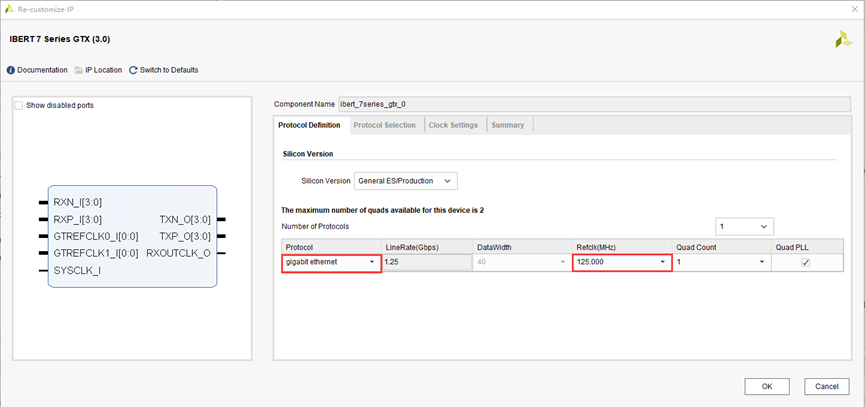

Altera 公司新推出的Cyclone IV GX FPGA 中含有8 個收發器,具有時鐘數據恢復(CDR)功能,并有在片內集成可編程預加重設置和可調差分輸出電壓(VOD)提高了信號完整性。本文的后續工作將在Cyclone IV GX 上實現本系統的所有功能,以進一步提高數據傳輸速率、傳輸距離、誤碼率等指標。

電子發燒友App

電子發燒友App

評論