to my logic My question is: In my .UCF timing constraints for clocking, I have ONLY specified

2019-02-28 06:24:28

:FTM0_Ch0_Ch1_IrqHandler 第 287 行: 如果 (chan0IntFlag && g_ftmChannelRunning[0][0]) { TIMING_Ftm_IrqHandler(0U, 0U

2023-03-29 08:20:52

見 AD5700 DatsSheet Page9,Carrier Detect Off Timing:請問圖中紅圈標(biāo)記的RXD波形是如何來的呢?在示波器上也觀察到了此現(xiàn)象,這個(gè)波形對于UART

2018-12-14 09:22:48

如果沒有 Bluetooth SIG 分配的Company Identifiers , 那么,在廣播數(shù)據(jù)中使用Manufacturer Specific Data(0xFF)會不會違規(guī)呢?

2023-10-24 15:50:21

and/or timing constraints on the callback for receiving vendor commands.I added some debug

2019-06-11 11:03:02

suitable topology and Determine IO choices? Timing margin calculation? Setup constraints? Other

2009-11-19 09:59:04

ISE Timing Anlayzer report 是看post-map 還是 post-place&route我現(xiàn)在有個(gè)工程 post-map 有錯(cuò)post-place&route 通過這該以哪個(gè)為準(zhǔn)

2017-08-24 14:15:26

本帖最后由 beHancock 于 2020-3-8 16:14 編輯

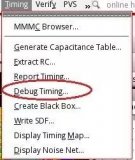

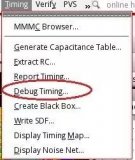

如題。補(bǔ)充幾個(gè)圖//-----------------------------------------這個(gè)目錄上Static Timing的圖標(biāo)都和其它的不一樣了。。。

2020-03-07 22:43:51

seem to be lost. For example, if I click on "Edit timing constraints", no constraints

2018-11-06 11:34:53

最近用到sopc,設(shè)計(jì)片外ram,故整理“SOPC中SDRAM controller 的Timing配置”一文以備忘。Timing選項(xiàng):CAS latency cycles(CAS等待時(shí)間):即為

2012-03-01 10:20:50

在使用庫函數(shù)(3.5版本),將通用定時(shí)器選用TIM_OCMode_Timing模式,同時(shí)使能4個(gè)通道中斷,可是進(jìn)不了定時(shí)器的中斷函數(shù)。當(dāng)選擇TIM_OCMode_Toggle模式時(shí),就能進(jìn)入到中斷

2019-09-19 17:42:20

smartxplorer on a design to get an implementation that meets timing constraints on a Virtex 6 FPGA and I

2018-10-22 10:59:44

Vivado toolchain in batch mode for the same project (everything is identical: scripts, constraints

2018-10-25 15:26:07

本課程主要介紹通過邏輯綜合工具,將Verilog RTL 代碼轉(zhuǎn)換成門級網(wǎng)表的方式,以滿足設(shè)計(jì)的時(shí)序要求。學(xué)習(xí)本課程可以熟悉邏輯綜合工具的使用。邏輯綜合技術(shù)是數(shù)字IC設(shè)計(jì)師必須掌握的一項(xiàng)核心技術(shù)。歡迎參與“啟芯SoC年度培訓(xùn)計(jì)劃”,了解詳情。

2014-07-03 16:52:39

本課程主要介紹通過邏輯綜合工具,將Verilog RTL 代碼轉(zhuǎn)換成門級網(wǎng)表的方式,以滿足設(shè)計(jì)的時(shí)序要求。學(xué)習(xí)本課程可以熟悉邏輯綜合工具的使用。邏輯綜合技術(shù)是數(shù)字IC設(shè)計(jì)師必須掌握的一項(xiàng)核心技術(shù)。歡迎參與“啟芯SoC年度培訓(xùn)計(jì)劃”,了解詳情。

2014-07-03 16:55:20

本課程主要介紹通過邏輯綜合工具,將Verilog RTL 代碼轉(zhuǎn)換成門級網(wǎng)表的方式,以滿足設(shè)計(jì)的時(shí)序要求。學(xué)習(xí)本課程可以熟悉邏輯綜合工具的使用。啟芯SoC年度培訓(xùn)計(jì)劃,可加入啟芯QQ群:275855756,了解詳情。

2014-03-09 16:12:57

fpga_timing技術(shù)文檔 xilinx官方

2016-08-17 09:02:16

niScope Configure Horizontal Timing 的說明中,參數(shù)number of records,根據(jù)我的測試,應(yīng)該是設(shè)置獲取信號的通道數(shù)。但min record

2018-01-09 15:44:28

38-35] Done setting XDC timing constraints.INFO: [Timing 38-2] Deriving generated clocks

2018-11-08 11:38:17

However, after "keep hierarchy = yes" was setted, the timing constraints can not be meeted. Any ways can solve this? Thanks!Best Regardsyhm

2019-03-28 13:38:35

因?yàn)镾partan 6不是PVT壓縮甚至使用了相位檢測。以上來自于谷歌翻譯以下為原文Assuming that there are no timing/coding mistakes =>How

2019-07-17 14:24:02

to!! ---------------+---------+---------+---------+---------+ Timing summary: --------------- Timing errors: 0Score: 0(Setup/Max: 0, Hold: 0) Constraints

2019-02-26 10:15:03

一步了,下面就可以在Constraints里面修改你自己需要的間距了(根據(jù)你們的制版工藝水平)。這樣就只影響鋪銅的間距,不影響各層布線的間距了。

2019-07-08 07:54:19

。以上來自于谷歌翻譯以下為原文Hi, I'm using Virtex II Pro and ISE 8.2.03i. My design don't meet timing constraints

2018-09-28 16:56:30

我想知道你們是如何學(xué)習(xí)計(jì)時(shí)教師的,你有沒有推薦的書或博客或教程?感謝幫助。以上來自于谷歌翻譯以下為原文How to write an advanced Timing constraint? I use

2019-03-27 09:58:42

FPGA開發(fā)板,工程編譯后,Timequest timing analyzer 顯示紅色,是否是錯(cuò)誤,需要改正?編譯結(jié)果中,messages框中,并沒有錯(cuò)誤,只是有一些警告,這樣看來,是不是那個(gè)timequest并不需要改正,也不會影響工程燒錄和運(yùn)行?(見下圖)求指點(diǎn)

2019-04-22 15:37:41

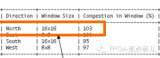

View specific resources regardless if they are used or not, For example I want to see how many

2018-10-30 18:02:58

喜我在Windows XP上安裝了xilinx ISE 10.1。我在地圖中遇到了一些時(shí)間問題,所以我在ISE的tcl窗口中將xil_timing_allow_impossible設(shè)置為1。地圖經(jīng)歷

2019-03-05 07:48:54

run place: ERROR: [Place 30-467] Based on the user constraints, this design needs to place 17 BUFG

2018-10-30 18:02:31

the issue, but to no avail. Are there other timing constraints that I am missing that would have

2019-03-01 11:36:19

shows the failing constraints (preceded with an Asterisk (*)). Please use the Timing Analyzer (GUI

2019-02-21 10:15:31

;Edit Timing Constraints" for Synthesis flow and that runs perfectly (I see the defined

2018-10-29 11:50:01

求一種MCU Specific Package單片機(jī)的具體解決方案

2021-12-10 07:46:15

玩轉(zhuǎn)Vivado之Timing Constraints特權(quán)同學(xué),版權(quán)所有最近在熟悉Xilinx已經(jīng)推出好幾年的Vivado,雖然特權(quán)同學(xué)之前已經(jīng)著手玩過這個(gè)新開發(fā)工具,但只是簡單的玩玩,沒有深入

2016-01-11 16:55:48

MIPI CS2 input timing和CX3 mipi interface configuration 的關(guān)系是什么?

CX3 mipi interface configuration中的值設(shè)置成什么是合理的?

2024-02-29 07:25:02

在quartus的仿真里面有兩種選項(xiàng),functional simulation和timing simulation,請問他們的區(qū)別是什么?

2019-07-29 05:52:59

在TMS320C6748 DSP Technical Reference Manual中看到某一外設(shè)的描寫,然后看到想要查看更多關(guān)于此外設(shè)的介紹,see your device-specific

2020-05-25 07:36:18

請問主機(jī)如何獲取廣播中 GAP_ADTYPE_MANUFACTURER_SPECIFIC后面的數(shù)據(jù)?

2022-08-10 06:06:38

timing and (maybe) area constraints.I am at the feasibility stage of the whole project and I’m looking

2018-09-30 11:09:49

design it says that the timing constraints cant be matched "There are 2 failing constraints

2019-05-08 13:07:02

本手冊主要描述高云半導(dǎo)體時(shí)序約束的相關(guān)內(nèi)容,包含時(shí)序約束編輯器(Timing Constraints Editor)的使用、約束語法規(guī)范以及靜態(tài)時(shí)序分析報(bào)告(以下簡稱時(shí)序報(bào)告)說明。旨在幫助用戶快速

2022-09-29 08:09:58

to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-13 13:33:25 13

13 to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-13 14:16:13 21

21 to use andunderstand. To determine specific timing details, usersneed only compare their paths of interest to the architectural

2009-05-15 13:50:49 8

8 timing and jitter measurements have become crucial

in the design, verification, characterization, and application of electron

2009-07-21 10:21:09 0

0 ISE時(shí)序約束:What effects do timing constraints have on your project?• The implementation tools do

2010-01-11 08:54:06 87

87 Without Timing Constraints• This design had no timingconstraints or pin assignments– Note

2010-01-11 08:54:44 6

6 Timing Groups and OFFSET Constraints:

•Use the Constraints Editor to create groups of path

2010-01-11 08:55:47 4

4 Achieving Timing Closure:Timing Reports• Timing reports enable you to determine how and why

2010-01-11 08:56:19 0

0 Path-Specific Timing Constraints:Constraining Between Risingand Falling Clock Edges•

2010-01-11 08:56:50 10

10 IntroductionUntil now, verifying that timing in 33 MHz 64-bit PCI designs met thesetup and hold

2010-07-13 09:39:34 4

4 Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs

Abstract

2009-04-07 23:43:36 666

666

microcontroller when used with external program memory. Due to the high speed of this device, critical memory interface timing constraints are examined.

2009-04-23 15:38:08 1087

1087

Timing Con

2009-04-24 09:12:31 740

740

The DS31415 is a flexible, high-performance timing IC for diverse frequency conversion

2011-08-01 16:27:04 25

25 本內(nèi)容介紹了邏輯分析儀中Timing-State存儲方式的應(yīng)用

2011-09-22 14:26:50 14

14 ofPERIOD constraints and the specific paths that arecovered by PERIOD constraints. Additionally, examplesof timing reports are included with t

2012-02-17 14:41:54 0

0 TimeQuest_Timing_Analyzer快速入門教程

2015-12-14 14:21:13 22

22 TMS320FC240 DSP Controllers Peripheral Library and Specific Devices Reference

2016-01-19 14:25:12 10

10 Timing,PCB學(xué)習(xí)好資料,歡迎下載學(xué)習(xí)。

2016-03-23 10:06:24 0

0 通常情況下,HoldTiming是由工具自動去檢查并滿足的,人為可以干預(yù)的地方很少。如果你的設(shè)計(jì)在布局布線后,出現(xiàn)了hold timing違例的情況,那么你可以參考下本文提出的3點(diǎn)建議,看看能否改善

2017-02-08 05:22:12 4871

4871

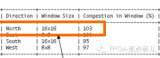

隨著FPGA規(guī)模越來越大,設(shè)計(jì)本身的復(fù)雜度也同樣增加。Xilinx UFDM中也經(jīng)常提到了Design Complexity這樣一個(gè)概念。Timing/Complexity/congestion

2017-02-08 05:46:09 3042

3042

Perfect Timing II Book

2017-10-27 09:23:52 6

6 ” ? “Synthesis Constraints” ? “Timing Constraints” ? “Configuration Constraints”

2017-11-24 19:59:29 2671

2671

” ? “Synthesis Constraints” ? “Timing Constraints” ? “Configuration Constraints”

2017-11-25 01:27:02 4716

4716

時(shí)序分析基本概念介紹——Timing Arc

2018-01-02 09:29:04 23487

23487

Timing.zip 5天前 上傳 下載次數(shù): 6 下載積分: 積分 -1 7.75 MB, 下載次數(shù): 6, 下載積分: 積

2018-08-06 15:08:02 400

400 上面我們講的都是xdc文件的方式進(jìn)行時(shí)序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進(jìn)行時(shí)序約束:時(shí)序約束編輯器(Edit Timing Constraints )和時(shí)序約束向?qū)В?b class="flag-6" style="color: red">Constraints Wizard)。兩者都可以在綜合或?qū)崿F(xiàn)后的Design中打開。

2020-03-08 17:17:00 19067

19067

然后會出現(xiàn)如下窗口, 使用GTD前, 需要有一個(gè)machine readable格式的timing report文件, 該文件可以通過report_timing -machine_readable

2020-05-19 16:14:47 7022

7022

AD9928:雙通道、14位CCD信號處理器,內(nèi)置垂直驅(qū)動器和Precision Timing發(fā)生器

2021-03-19 01:16:56 7

7 AD9923A: CCD 信號處理器,內(nèi)置垂直驅(qū)動器和Precision Timing發(fā)生器 數(shù)據(jù)手冊

2021-03-19 06:53:40 0

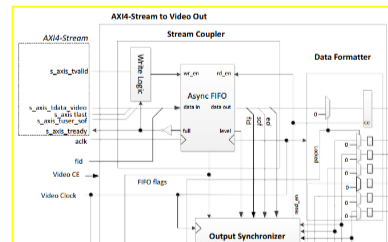

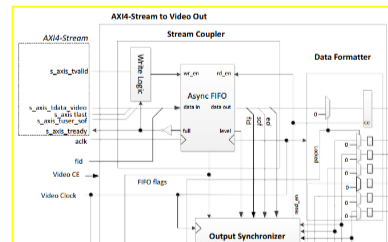

0 本文對Video out IP和Video Timing Controller IP進(jìn)行簡要介紹,為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測試工程做準(zhǔn)備。

2021-05-08 10:03:16 5452

5452

隨著設(shè)計(jì)復(fù)雜度和調(diào)用 IP 豐富度的增加,在調(diào)試時(shí)序約束的過程中,用戶常常會對除了頂層約束外所涉及的繁雜的時(shí)序約束感到困惑而無從下手。舉個(gè)例子,用戶在 XDC 里面并沒有指定 set_false_path,為什么有些路徑在分析時(shí)忽略了?那怎么去定位這些約束是哪里設(shè)定的?

2022-09-15 10:24:37 972

972 Timing Commander 硬件 Interfaces 用戶指南

2023-03-15 19:24:19 1

1 9FGV1005 PhiClock PCIe Timing Commander 軟件 用戶指南

2023-03-21 19:28:49 2

2 9FGV1006 Timing Commander 用戶指南

2023-03-21 19:29:17 1

1 9FGV100x Timing Commander 用戶指南

2023-03-21 19:29:27 0

0 Timing Commander 軟件 for VersaClock 3S - 5P3502x

2023-03-23 19:42:47 1

1 VersaClock 6 Timing Commander 用戶指南

2023-03-29 19:02:31 1

1 默認(rèn)report_timing中會出現(xiàn)換行的情況,如下圖所示,如何避免換行呢?

2023-04-15 10:20:33 2089

2089 Timing Commander 軟件 for Programmable Buffers

2023-05-15 19:16:04 0

0 有些情況下,constraint不能簡單用一行來表達(dá),而是需要復(fù)雜的計(jì)算,如果都寫到constraint block內(nèi)部就比較復(fù)雜,而且很亂,這時(shí)候可以調(diào)用functions來約束隨機(jī)變量。在constraint內(nèi)調(diào)用function就稱為”function in constraints”。

2023-06-21 17:31:28 635

635 今天介紹一下,如何在Vivado中添加時(shí)序約束,Vivado添加約束的方法有3種:xdc文件、時(shí)序約束向?qū)В?b class="flag-6" style="color: red">Constraints Wizard)、時(shí)序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

今天我們要介紹的時(shí)序分析概念是 **時(shí)序路徑** (Timing Path)。STA軟件是基于timing path來分析timing的。

2023-07-05 14:54:43 985

985

今天我們要介紹的時(shí)序基本概念是Timing arc,中文名時(shí)序弧。這是timing計(jì)算最基本的組成元素,在昨天的lib庫介紹中,大部分時(shí)序信息都以Timing arc呈現(xiàn)。

2023-07-06 15:00:02 1397

1397

Timing Commander 硬件 Interfaces 用戶指南

2023-07-06 18:35:05 0

0 9FGV1005 PhiClock PCIe Timing Commander 軟件 用戶指南

2023-07-07 19:27:28 0

0 9FGV1006 Timing Commander 用戶指南

2023-07-07 19:28:06 0

0 9FGV100x Timing Commander 用戶指南

2023-07-07 19:28:21 0

0 Timing Commander 軟件 for VersaClock 3S - 5P3502x

2023-07-10 19:34:18 0

0 VersaClock 6 Timing Commander 用戶指南

2023-07-11 19:27:17 1

1 Timing Commander 軟件 for Programmable Buffers

2023-07-11 20:27:38 0

0 今天想來聊一聊timing model。Top層在做STA的時(shí)候,為了速度的考量,有的時(shí)候不會把所有block都做flatten(展平化)處理

2023-12-06 14:03:13 270

270

電子發(fā)燒友App

電子發(fā)燒友App

評論