開發板有兩路千兆以太網,通過RGMII接口連接,本實驗演示如何使用Vitis自帶的LWIP模板進行PS端千兆以太網TCP通信。

LWIP雖然是輕量級協議棧,但如果從來沒有使用過,使用起來會有一定的困難,建議先熟悉LWIP的相關知識。

2021-01-28 10:01:00 8467

8467

在Zybo上運行時,SDK 2106.3 LWIP實現會發出“警告:不是Marvell或TI以太網PHY。請驗證初始化序列”。我的狹隘問題是,任何人都可以建議核查工作的結果。明顯的搜索沒有提供答案

2020-05-11 07:40:45

嗨,我使用Zynq,我想通過以太網將數據轉儲到DDR RAM。數據大小約為4MByte。我在示例中使用了標準的Lwip應用程序。獲取完整數據大約需要15-20分鐘。我的Lwip BSP設置:我收到

2020-08-21 09:59:01

SDK135D - Embedded SDK (Software Development Kit) - Freescale Semiconductor, Inc

2022-11-04 17:22:44

\ 2015.2 \ bin \ xsct build_sdk.tcl在build_sdk.tcl里面有;....sdk create_app_project -name zynq_f***l

2019-04-26 13:45:07

使用 SDK 示例 lwip_httpsrv_bm 在激活“普通加載圖像”的情況下工作得很好。

因為 RAM 非常有限,所以我需要切換到 XIP 模式并在外部 SPIFI 閃存中執行我的代碼。

但是

2023-04-28 08:57:47

。

SDK軟件部分

打開SDK后,新建application project,這里為了方便lwip設置,可選用使用lwip的相關模板,這里選擇lwip tcp回環測試模板,保存新建工程。

[ ]

編輯

2023-06-15 18:13:03

、輸出管腳,并將Vivado例程頂層模塊的管腳添加進來: 生成下載bit流文件點擊Generate Bitsteam,生成bit流文件,在彈出的對話框中選擇Yes: 如果在生成bit流文件過程中

2023-02-13 20:21:27

1、Zynq MPSoC支持的DDR介紹自己做自己的嵌入式產品一般要選擇合適的DDR,而這里開發板給的是4GB的UIMM的DDR4,也就是電腦上用的,所以用不了,只能自己掛載Component,這里

2022-04-19 17:56:03

初學 Zynq 的時候,都是按照慣例打開 Vivado 軟件,然后實現 Zynq 可編程邏輯硬件部分PL的設置后,把硬件部署導出,再打開 SDK 進行 ARM 核的軟件部分 PS 編程設計,最后

2021-01-08 16:33:01

嗨,我必須找出zynq 7020 PS和zynq PL如何通話,特別是我必須找到將在ARM中處理的SDK C代碼。你能用一個明確的C代碼告訴我,它解釋了數據如何從PS轉移到PL,這是ARM用來做這個的基本程序嗎?謝謝

2020-05-08 09:37:11

在SDK中運行程序時,我可以在StandAlone模式下使用多少內存?(在帶有1G DDR的Zynq7030上)運行程序時獨立模式需要多少內存?非常感謝。以上來自于谷歌翻譯以下為原文When

2019-03-29 13:37:45

什么類型的板子完成連接元器件編輯元件Program File這里是選擇你要運行的程序的 HEX 文件。在 KEIL中選擇創建HEX文件Crystal Frequency這里很重要,很多人運行不成功都是因為沒有在這里設定晶振頻率。必須要設定!!!配置供電網要想仿真使用

2021-08-04 08:23:39

HII,我在zynq板上工作。在vivdao工具中,當我嘗試將硬件導出到SDK時,顯示錯誤“文件夾c:\ documents \ .metadata”是只讀的..所以我不能因為這個而使用SDK ..任何人都可以提出更好的方法嗎???謝謝,阿比拉什B.

2020-05-27 09:18:27

的FLASH外設,但是我不知道這個寄存器是在哪里被設置的,有沒有大佬告訴我,在軟件SDK中選擇不同的下載模式時,是哪個部件更改了QSPI0中寄存器的值?是系統總線上的Jtag嗎?還是CPU直接對外設總線上的QSPI0進行寫操作?

2024-01-10 08:10:03

AD18的交叉選擇模式問題: 比如我要在原理圖中選擇一部分,然后在PCB中layout,但移動選擇的這部分時,上面的所有網絡都會被移動,包括電源和地網絡,

2018-12-28 14:52:50

創建新的Module。方法2:在菜單欄選擇File > New > Module,開始創建新的Module。在New Project Module界面中,選擇Module對應的設備類型和模板。點擊Next

2020-09-18 15:30:58

Finish all 似乎不錯,但是當我選擇 ConfigTools Pins 時,我得到錯誤 MCU is not selected 即使我在設備包下的向導中選擇了我需要的特定的。這是我第一次嘗試使用 NXP 處理器,所以希望我遺漏了一些明顯的東西。

2023-03-21 07:37:54

PADS如何實現在原理圖中選擇元件時也同時選擇PCB呢?

2023-04-28 16:25:56

Processor 和各Components 配 置,操作步驟介紹如下: i 在 IDE 界面內,在標題項中選擇File,并在彈出的選項列中選中Export,即會彈出 Export 向導窗口,在向導窗口中展開

2014-12-30 15:38:18

。在主菜單“工程(Project)”中點擊“模板管理(Template Management)”,隨后出現窗體,在窗體中圖形化顯示內置的模板集合。點擊“導入(Import)”,在系統瀏覽器中選擇模板包

2021-10-12 15:15:21

今天在神舟STM32F107V1.0的開發板上移植了RT Thread,網絡部分已經通了,而且個人覺得RTT小組把LWIP優化的非常的好,簡單易用,但是還是存在了寫不足。可不可以把TCP鏈接

2022-04-20 11:41:19

請問在Xilinx Vivado之中,沒有PL的工程,能否直接開啟SDK程序,并固化程序到ZYNQ的芯片之上

2021-03-29 17:22:00

CPUCPU為Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平臺升級能力強,以下為Xilinx Zynq-7000特性參數:電源接口和開關采用12V3A

2021-12-30 07:55:37

本帖最后由 Joevin 于 2015-8-1 16:49 編輯

工具: EDK(ISE 14.7) + SDK1. Zynq配置中使能Enet0,配置如下:2. SDK中創建lwIP

2015-08-01 16:16:05

因為最近要用到zynq芯片,我希望能在zynq芯片上使用freeRTOS,但是弄不明白怎么移植進去。一般xillinx sdk在工程里面添加操作系統的方法是,在repository里先安裝相應的庫

2020-06-11 04:35:29

請教一下各位哥老倌,SDK中,JTAG啟動模式下,zynq的arm boot不起來,程序debug不能運行的問題。準確說是memery test可以運行,arm正常工作,換hello world例程

2016-12-20 12:38:45

使用的是18.1版本的VIVADO。 這次的練習選擇的是ZYNQ的芯片,原本工程是工作在100MHz的時鐘,但是作為練習,我們可以把時鐘調到一個極限的程度來進行優化。 首先,打開一個工程,更改一下時鐘頻率,使得工程

2018-08-22 11:45:54

SDK軟件部分,點擊FileàLaunchSDK 在SDK環境下,新建應用程序工程 在模板中選擇lwIP Ethernet Apps(raw API),即可自動加載lwIP協議棧了 編譯工程 下載

2016-12-14 15:56:23

。4-2 硬件導出完成后,在菜單欄中選擇File > Launch SDK,啟動SDK開發環境。如下圖所示:圖 1.3.34 啟動SDK開發環境在彈出對話框中,直接點擊“OK”,如下圖所示:圖

2020-08-26 17:14:43

綴名.hdf的含義為“Hardware Definition File”,即硬件定義文件。4-2 硬件導出完成后,在菜單欄中選擇File > Launch SDK,啟動SDK開發環境

2020-08-29 16:14:56

hello_world工程,在彈出的菜單欄中選擇Run as > 1 Launch on Hardware (sysntem Debugger),如下圖所示:圖 18.2.4 運行在Console終端可以看到

2020-09-10 17:49:45

Bitstream文件,只需導出到SDK即可。如果使用到PL,則需要添加引腳約束以及對該系統進行綜合、實現并生成Bitstream文件。4-1 導出硬件。在菜單欄中選擇 File > Export

2020-09-08 11:02:37

程,保留bsp工程。下面我們開始第五步——創建應用工程。下面我們開始第五步——創建應用工程step5:在SDK中創建應用工程5-1在菜單欄中選擇“File->New->Application

2020-09-08 11:06:18

描述TIDA-00390 設計是一種經過優化的電源解決方案,適用于 Xilinx? Zynq? 7020 FPGA/SoC(屬于 Zynq? 7000 產品系列)。它面向客戶選擇使用 FPGA 代替

2018-08-09 07:58:16

報錯 lwip-1.4.1 版本選擇函數后引發的使用版本。內部:sock != NULL at line 1296 in src/api/sockets.c在多線程同時使用 lwip-1.4.1版本

2021-12-29 06:56:56

事件結構中選擇雙擊文件列表,系統會自動選擇雙擊的那項,然后進行索引選擇那個文件是嗎?嘗試了一下是這樣但不知道原理,有沒有人能解釋一下,謝謝!

2015-04-20 16:00:39

,在 Vitis 調式設置中選擇不下載 FPGA 。如果是用慣了SDK開發,Vitis 第一次用還是有點不太習慣的,多用幾次就好了。另外,之前在公眾號的另一篇文章中,有 40 位左右網友留言需要

2020-03-06 22:59:12

手把手教你創建 LWIP 模板例程第1步:打開Cube MX軟件第2步:新建工程第3步:選擇自己使用的芯片并開始工程配置第4步:開啟仿真接口第5步:選擇外部高速時鐘HSE第6步:配置USART串行

2022-01-19 07:18:17

一、創建GUIDE文件在命令行空間輸入:guide,進入GUIDE快速入門界面,在【新建GUI】中選擇模板,四類模板分別為:Blank GUI(空白模板)、GUI with Uicontrols

2021-08-17 09:31:58

一篇《基于HDevelop地形狀匹配算法參數地優化研究》文章,總結了在形狀匹配過程中哪些參數影響到模板地搜索和匹配,又如何來協調這些參數來加快匹配過程,提高匹配地精度,這篇paper放到了中國論文在線

2023-09-19 06:13:48

【第10講 新建工程模板-基于固件庫】201703151,MDK中源文件顯示為亂碼,解決方法如下:1)點擊菜單欄Edit按鈕,在其下拉選項中選擇點擊Configuration2)在默認彈出

2021-08-20 06:52:29

各位高手,我用767做tcp server端,接收PC機發過來的數據。目前測試大約可以達到1MB/s,我看網上有人說可以達到4MB/s。有人測試過嗎?可以在哪里優化提高lwip的tcp接收性能?

2019-09-03 23:05:28

嗨,大家好,我是新手SDK用戶。我使用vivado hls來合成一個簡單的圖像處理算法,并構建了我現在使用sdk的硬件平臺,我想使用sdk在獨立模式下使用opencv應用程序在zynq fpga上

2020-05-04 17:09:19

。之所以系統會自動選擇 bootloader 是因為我們在新建 zynq_f***l 工程的時候在 Templates 向導中選擇"Zynq FSBL"后,生成

2018-06-08 10:13:57

需要ESP32做AP,可以連接6個sta, 同時在AP測建立tcp server,要求可以連接6個client。目前發現ESP32的SDK默認只能連接4個sta, tcp server只能連接2個client。怎要修改SDK的參數才能滿足項目需求?

2023-03-09 08:03:39

請問如何在貼片工作中選擇錫膏?

2021-04-23 06:15:18

嗨,大家好,我試圖建立一個內存測試項目。我正在使用的FPGA是Artix-7 XC7A15T,我的目的是在IPI中創建一個帶有微型激光器的設計,作為MIG塊的主控,以便導出到SDK并運行Xilinx

2020-08-04 10:04:05

,自然而然隨之而來就會有這樣幾個問題——這些工程是如何內置在MRS中的呢?我們又如何將已有的工程,保存為自己的模板、供其他用戶使用呢?本文我們就來一一介紹。【工程保存為模板】編寫工程后,在工程瀏覽器

2022-02-11 06:06:53

目前關于微波天線優化的研究成果雖然很多,但多數均是從單一因素進行考慮,優化效果并不是非常理想,本文通過綜合考慮多種因素并優化微波天線選擇參數來尋找更合理的選擇方法。

2021-05-26 06:04:03

電磁波等能量。微波天線是微波通信系統收發設備的“出入口”,天線性能直接影響整個系統的運行。目前關于微波天線優化的研究成果雖然很多,但多數均是從單一因素進行考慮,優化效果并不是非常理想,本文通過綜合考慮多種因素并優化微波天線選擇參數來尋找更合理的選擇方法。

2019-06-11 07:25:18

你好,我是Vivado程序的新手,我在Vivado創建新項目時應該選擇哪個板塊。在創建新項目時,我可以選擇xc7z020clg484-1或xc7z045ffg900-2,但在Digilent網站

2019-03-28 06:27:19

你好我目前正在開發Zynq系統。我想在開發SDK或Plan Ahead時測量硬件使用(CPU)。任何回復將不勝感激謝謝。以上來自于谷歌翻譯以下為原文Hi, thereI am currently

2019-03-18 14:08:04

報表一選擇模板就彈出這個錯誤,請教下。

2016-07-30 00:01:48

在Zynq教程書中,它提到system.mss可以在vivado SDK中打開,以獲取更多信息設備驅動程序。但我無法在SDK中找到它。我使用的是2015.1版。另外,有沒有文件可以在SDK中教新手c / c ++編程? xilinx網站上的文檔不是很有幫助。謝謝,赫茲

2020-03-31 09:42:25

是否有人將 freertos sdk 與 lwip raw 一起使用?

我使用的 SDK 是 11 月 2 日(最新)的 1.3.0。

當我使用這種組合時,我遇到了 lwip

2023-06-12 08:54:36

這幾天在弄LWIP,照原子的視頻移植好了,但是感覺原子的demo不太好,改了太多,就想自己寫,調用API報錯,說沒定義,我頭文件是包含了的,路徑添加也跟原子視頻里的一樣。。但就是不行,,嗚嗚。。搞得

2019-07-25 02:23:32

一、功能簡介在window系統中將rtthread移植到zynq在sdk中實現無bsp的zynq工程調試在zynq中演示rtthread的shell功能二、配置需求三、移植步驟下載RT-Thread

2022-07-01 10:48:51

(BoardSupport Package),然后SDK上可以新建軟件工程,編寫應用程序,實現Zynq上Cortex A9的開發。本節以zstar_ex50工程為例,演示如何將PL工程的PS硬件配置導出、在SDK新建一個

2019-09-25 09:43:18

Zynq,而是如何新建Zynq系統模塊、配置PS的參數、導出硬件、新建軟件工程并且在線板級運行起來。流程很重要,大家在開始的時候總要先走一遍流程了解開發的全貌,然后再細細把玩,逐個精通。 2 新建

2019-09-30 12:57:32

Platform)選擇zstar_zynq_ps_wrapper_platform_0,點擊Next。Templates頁面中,選擇Hello World工程模板。點擊Finish完成工程創建。新建

2019-09-30 14:11:59

和新建SDK工程.pdf》。其中新建SDK工程名稱為GPIO_MIO_project。工程模板(AvailableTemplates)選擇空白應用(Empty Application)即可。 3

2019-10-10 11:21:06

.pdf》。SDK中,新建Empty的模板工程,名稱為GPIO_EMIO_project。 5 EMIO控制編程展開新建的工程GPIO_EMIO_project,選中文件夾src,單擊右鍵,彈出菜單中選擇

2019-10-12 17:35:16

/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c 1SDK在線運行裸跑程序以zstar_ex50為例,演示如何將裸跑程序在Zstar板上在線運行起來。點擊SDK的菜單Run -->Run

2019-10-25 14:58:09

的USB端口和Zstar板的JTAG插座)。使用5V電源給板子供電。參考文檔《玩轉Zynq-工具篇:SDK在線運行裸跑程序.pdf》將當前工程產生的.bit文件和.elf文件在Zstar板上運行起來。打開

2019-11-12 10:23:42

寫使能開關以及對應通道的帶寬。5嵌入式軟件工程創建參考文檔《玩轉Zynq-工具篇:導出PS硬件配置和新建SDK工程.pdf》導出PS硬件工程,并打開EDK新建一個HelloWorld的模板工程。本實例

2019-11-28 10:11:38

/fmcomms2/zed/fmcomms2_zed.sdk/system_top_hw_platform_0:對于定義的數據類型,值太大cc1:錯誤:../../ zynq_f***l_bsp

2018-12-27 10:58:11

描述TIDA-00389 設計是一種經過優化的電源解決方案,適用于 Xilinx? Zynq? 7010 FPGA/SoC(屬于 Zynq? 7000 產品系列)。它面向 ADAS 應用,在這

2018-11-19 15:00:01

針對蟻群算法運行參數選取問題,提出一種利用粒子群優化算法對蟻群算法的運行參數進行優化選擇的方法。將蟻群算法的運行參數作為粒子群的位置信息,在算法迭代過程中使用

2009-04-22 08:42:34 28

28 LwIP無操作系統下的實驗

本文詳細講述了LwIP在無操作系統支持環境下的API函數介紹及編程應用。首先,介紹了RAW API的特點及優缺點,然后逐個介紹了LwIP提供的

2010-04-07 16:39:41 109

109 LWIP是TCP/IP協議棧的一種實現。LWIP的主要目的是減少存儲器利用量和代碼尺寸,使LWIP適合應用于小的、資源有限的處理器如嵌入式系統。為了減少處理器和存儲器要求,lwIP可以通過不需

2011-09-16 15:18:36 33

33 LWIP是TCP/IP協議棧的一種實現。LWIP的主要目的是減少存儲器利用量和代碼尺寸,使LWIP適合應用于小的、資源有限的處理器如嵌入式系統。為了減少處理器和存儲器要求,lwIP可以通過不需

2012-02-03 16:47:58 0

0 文章結合數字示波器的幾個主要性能指標,對其實現信號完整性的能力進行了分析,并提出了在測試過程中選擇適合數字示波器的參考依據。

2012-12-21 11:38:17 1430

1430 LwIP編程指南,LwIP是Light Weight (輕型)IP協議,有無操作系統的支持都可以運行。LwIP實現的重點是在保持TCP協議主要功能的基礎上減少對RAM 的占用,它只需十幾KB的RAM和40K左右的ROM就可以運行,這使LwIP協議棧適合在低端的嵌入式系統中使用。

2015-11-09 18:28:03 45

45 LwIP協議詳解,LwIP是Light Weight (輕型)IP協議,有無操作系統的支持都可以運行。LwIP實現的重點是在保持TCP協議主要功能的基礎上減少對RAM 的占用,它只需十幾KB的RAM和40K左右的ROM就可以運行,這使LwIP協議棧適合在低端的嵌入式系統中使用。

2015-11-09 18:25:20 48

48 TCPIP協議棧的實現lwip方便初學者剛開始接觸lwip,有個大概的了解與認識。

2016-03-14 15:40:04 13

13 STM32F4_LWIP開發手冊_ALIENTEK探索者LWIP開發教程,感興趣的小伙伴們可以看看。

2016-07-26 10:43:06 240

240 Zynq平臺運行SDK程序錯誤的解決辦法,具體的跟隨小編一起來了解一下。

2018-07-14 06:05:00 7592

7592 在Vivado下完之前,先把Zynq的軟件編譯環境安裝好,可以用來重新編譯基于Zynq的Linux系統,同時能寫基于Zynq的C程序(其實Vivado中的SDK也能實現)。

2017-02-10 15:54:12 4487

4487

本文介紹zynq中使用FreeRTOS的空閑鉤子函數時在SDK中的設置和一些說明

2017-03-09 14:33:06 2372

2372

模板計算是一類重要的計算核心,廣泛存在于圖像和視頻處理以及大規模科學和工程計算領域。但是,針對ARM64高性能處理器的模板計算性能的優化研究還很少。為了實現典型模板計算核心在ARM64架構多核

2017-11-21 14:50:59 1

1 lwip是一套用于嵌入式系統的開放源代碼TCP/IP協議棧。Lwip既可以移植到操作系統上,又可以在無操作系統的情況下獨立運行。下面我們來看看lwip移植說明及心得。

2017-12-11 16:06:32 19514

19514

電源設計小貼士 37:折中選擇輸入電容紋波電流的線壓范圍

2018-08-08 02:03:00 5547

5547 Zynq-7000 AP SoC硬件和軟件開發流程中,用于嵌入式軟件開發的工具就是Xilinx SDK。Xilinx SDK是一個基于Eclipse的IDE,內含Xilinx提供的豐富的工具和軟件包

2020-05-31 08:40:00 2082

2082 在本視頻中,我們將學習如何使用Xilinx SDK啟動電路板,利用每個驅動程序提供的應用示例并測試各種外設。

我們將詳細介紹Zynq DRAM測試,并了解如何利用它進行測試。

2018-11-29 06:50:00 4666

4666 了解如何在Zynq處理器上使用輕量級IP堆棧(lwIP)來實現網絡功能。

本次會議既包括獨立用例,也包括與流行的輕量級FreeRTOS操作系統的集成。

2018-11-27 06:17:00 5007

5007 了解如何使用Xilinx SDK創建Zynq引導映像。

我們將在通過Xilinx SDK創建Zynq引導映像時查看可以選擇/添加的引導參數和分區。

2018-11-23 06:24:00 3601

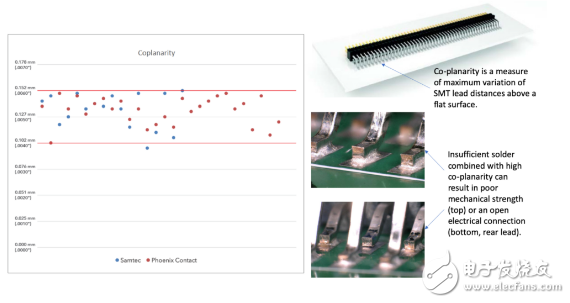

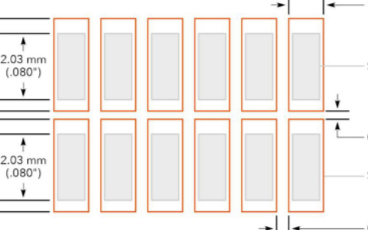

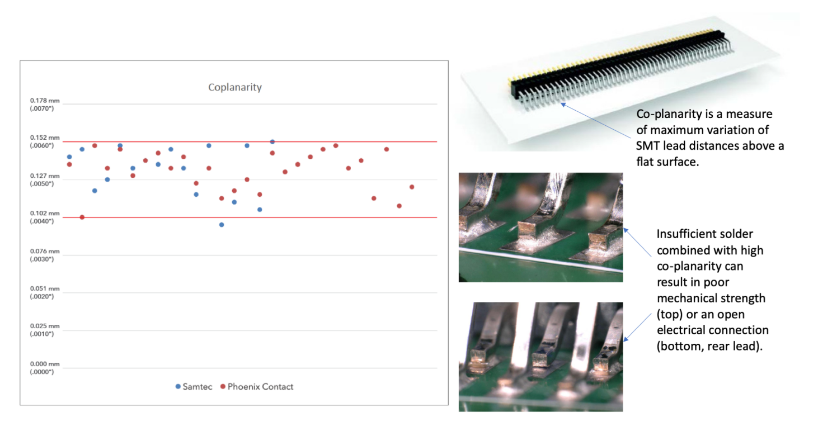

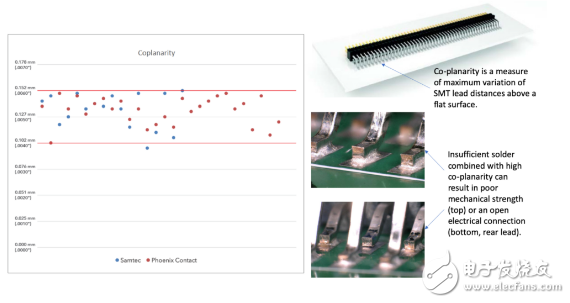

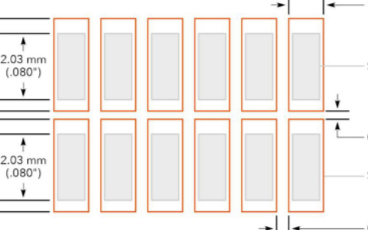

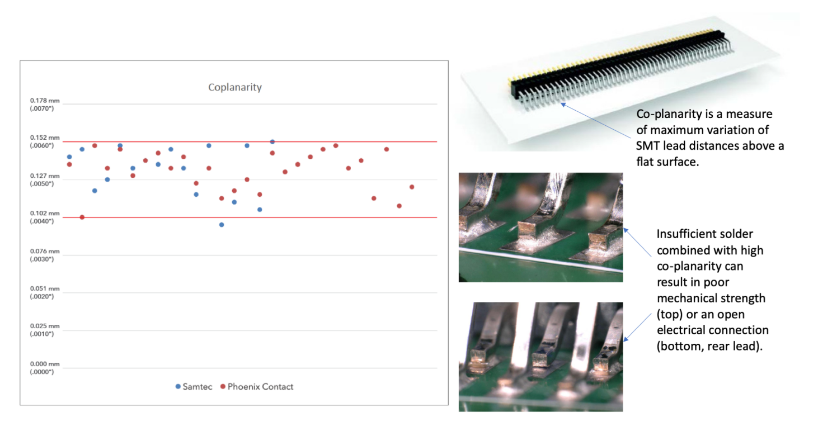

3601 隨著電子系統中元器件密度的提高,設計師通常為了和印制電路板(PCB)上厚度為0.10 mm的焊膏模板配套,而選擇共面度不超過0.10 mm的、同等精密的連接器。然而,市場上有很多共面度值為0.15

2019-11-18 17:38:49 555

555

本文將討論焊膏模板與連接器共面度之間的關系,以及設計師面臨的取舍和制約因素等話題。然后本文將介紹此項研究的情況和相應的結果,以及這些結果在優化設計的時候對成本、空間、性能和可靠性產生的影響。

2019-12-04 15:34:37 698

698

隨著電子系統中元器件密度的提高,設計師通常為了和印制電路板(PCB)上厚度為0.10 mm的焊膏模板配套,而選擇共面度不超過0.10 mm的、同等精密的連接器。

2020-05-04 09:35:00 486

486

本文檔的主要內容詳細介紹的是XILINX中的zynq ultrascale plus產品選擇指南。

2020-12-31 17:30:53 5

5 Processor is ready. Configure programable logic.在新專欄 Rapid TCP/IP on Zynq 中,將圍繞 Xilinx Zynq 系列芯片,從 SDK 驅動,PS-...

2022-02-07 10:59:19 0

0 然而,Samtec Inc.和Phoenix Contact的一項研究表明,通過優化焊膏模板的開孔形狀,設計師就可以選擇已廣泛提供的、價格更低的、共面度為0.15 mm的連接器來與更精細的0.10

2024-01-02 15:33:25 89

89

電子發燒友App

電子發燒友App

評論