0 引 言

由于數(shù)字邏輯系統(tǒng)功能復(fù)雜化的需求,單片系統(tǒng)的芯片正朝著超大規(guī)模、高密度的方向發(fā)展。對于一個大規(guī)模的數(shù)字系統(tǒng)而言,系統(tǒng)規(guī)模是基于各種邏輯功能模塊的組合。但是,無論是時序邏輯系統(tǒng),還是組合邏輯系統(tǒng),或者組合/時序混合系統(tǒng),從時間軸上來看,系統(tǒng)中的各個功能模塊并不是時刻都在工作,而是根據(jù)系統(tǒng)外部的整體要求,輪流或循環(huán)地被激活或工作。并且,隨著數(shù)字邏輯規(guī)模的擴大,在相同速度條件下,在一定的時間區(qū)間,其功能模塊的平均使用率將下降。因此,系統(tǒng)設(shè)計應(yīng)該從傳統(tǒng)追求大規(guī)模、高密度的方向,轉(zhuǎn)向如何提高資源利用率,用有限的資源實現(xiàn)更大規(guī)模的邏輯設(shè)計上來。可重構(gòu)計算技術(shù)能夠提供硬件的效率和軟件的可編程性,它綜合了微處理器和ASIC的特點,在空間維和時間維上均可變。

1 可重構(gòu)技術(shù)概述

1.1 可重構(gòu)的定義

可重構(gòu)就是在電子系統(tǒng)的工作狀態(tài)下,動態(tài)地改變電路的結(jié)構(gòu)。這主要通過對系統(tǒng)中的可編程邏輯器件進(jìn)行重新配置或者局部重新配置來完成。利用可重構(gòu)技術(shù),能在只增加少量硬件資源的情況下,使系統(tǒng)同時具有軟件實現(xiàn)和硬件實現(xiàn)的優(yōu)點。

1.2 可重構(gòu)方式的分類

按照重構(gòu)的方式,系統(tǒng)重構(gòu)可以分為靜態(tài)系統(tǒng)重構(gòu)(Static Reconfiguration)和動態(tài)系統(tǒng)重構(gòu)(Dynamic Reconfiguration)。

1.2.1 靜態(tài)系統(tǒng)重構(gòu)

靜態(tài)系統(tǒng)重構(gòu)是指目標(biāo)系統(tǒng)的邏輯功能靜態(tài)重載,只能在運行前配置的系統(tǒng),如圖1所示。

FPGA功能在外部邏輯的控制下,通過存儲于存儲器中不同的目標(biāo)系統(tǒng)數(shù)據(jù)重新下載,從而實現(xiàn)芯片邏輯功能的改變。

1.2.2 動態(tài)系統(tǒng)重構(gòu)

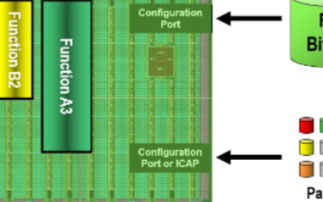

動態(tài)系統(tǒng)重構(gòu)是指能在運行過程中實時配置的可重構(gòu)系統(tǒng),如圖2所示。

對于時序變化的數(shù)字邏輯系統(tǒng),其時序邏輯的發(fā)生不是通過調(diào)用芯片內(nèi)不同區(qū)域、不同邏輯資源組合而成的,而是通過對具有專門緩存邏輯資源的FPGA進(jìn)行局部或全局的芯片邏輯的動態(tài)重構(gòu)而快速實現(xiàn)的。動態(tài)系統(tǒng)結(jié)構(gòu)的FPGA具有緩存邏輯(Cache Logic),在外部邏輯的控制下,通過緩存邏輯對芯片邏輯進(jìn)行全局或局部的快速修改,通過有控制重新布局布線的資源配置來加速實現(xiàn)系統(tǒng)的動態(tài)重構(gòu)。就動態(tài)重構(gòu)實現(xiàn)面積的不同,又可以分為全局重構(gòu)和局部重構(gòu)。

(1)全局重構(gòu)。對FPGA器件或系統(tǒng)能且只能進(jìn)行全部的重新配置。在配置過程中,計算的中間結(jié)果必須取出存放在額外的存儲區(qū),直到新的配置功能全部下載完為止,重構(gòu)前后電路相互獨立,沒有關(guān)聯(lián)。

(2)局部重構(gòu)。對重構(gòu)器件或系統(tǒng)的局部重新配置,與此同時,其余局部的工作狀態(tài)不受影響。局部重構(gòu)對減小重構(gòu)的范圍和單元數(shù)目,大大縮短重構(gòu)時間,占有相當(dāng)?shù)膬?yōu)勢。

2 基于FPGA的局部動態(tài)可重構(gòu)技術(shù)

2.1 具有局部動態(tài)可重構(gòu)功能的FPGA

過去大家普遍進(jìn)行動態(tài)重構(gòu)研究的FPGA主要有Xilinx公司的XC6200系列和Atmel公司的AT6000系列等。它們也是基于SRAM結(jié)構(gòu),但是SRAM的各個單元能夠單獨訪問配置,即局部重構(gòu)。它們的功能互不影響,因而具有局部重構(gòu)的特征。這樣做的優(yōu)點顯著,但也會付出增大硬件電路規(guī)模和功耗的代價。最終要實現(xiàn)電子系統(tǒng)的完全實時重構(gòu),應(yīng)采用結(jié)構(gòu)上具有動態(tài)局部重構(gòu)功能的FPGA器件,如Xilinx公司的Virtex-4系列。

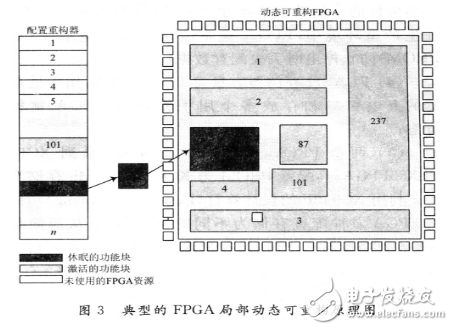

2.2 基于FPGA局部動態(tài)可重構(gòu)技術(shù)主要特征及典型原理

FPGA局部動態(tài)可重構(gòu)技術(shù)的特征就是將整體按功能或按時序分解為不同的組合,并根據(jù)實際需要,分時對芯片進(jìn)行局部動態(tài)重構(gòu),以較少的硬件資源實現(xiàn)較大的時序系統(tǒng)整體功能。圖3給出一種典型的FPGA局部動態(tài)可重構(gòu)。由圖3可以看出,在外部邏輯的控制下,可以實時動態(tài)地對芯片邏輯實現(xiàn)局部重構(gòu)。通過控制布局、布線的資源,實現(xiàn)系統(tǒng)的動態(tài)重構(gòu)。

2.3 FPGA實現(xiàn)局部動態(tài)可重構(gòu)的結(jié)構(gòu)要求

要使FPGA有效地實現(xiàn)實時系統(tǒng)動態(tài)重構(gòu),F(xiàn)PGA在結(jié)構(gòu)上必須滿足以下要求:

(1)不僅具有可重新編程能力,同時可動態(tài)進(jìn)行系統(tǒng)資源地重新配置,而不會破壞器件中全局或局部邏輯操作能力。很多傳統(tǒng)的FPGA把配置數(shù)據(jù)存放在外部的串行EPROM中。這種方式有3個缺點:重構(gòu)之前整個FPGA必須停止工作;只是對整個FPGA進(jìn)行重構(gòu);重構(gòu)時FPGA中以前的內(nèi)部狀態(tài)無法保存。新的能夠?qū)崿F(xiàn)動態(tài)可重構(gòu)的FPGA不需要在重構(gòu)之前觸發(fā)復(fù)位信號,而是將FPGA芯片中的一局部邏輯電路的時鐘關(guān)閉,然后重新配置邏輯電路,最后恢復(fù)時鐘信號。

(2)FPGA內(nèi)部配置信息對稱,記載任何時刻,任何通用的基本邏輯功能可以配置于器件的任何一個位置,運用簡單模型組合去實現(xiàn)設(shè)汁中的復(fù)雜功能。

3 基于FPGA的可重構(gòu)演示系統(tǒng)的設(shè)計與實現(xiàn)

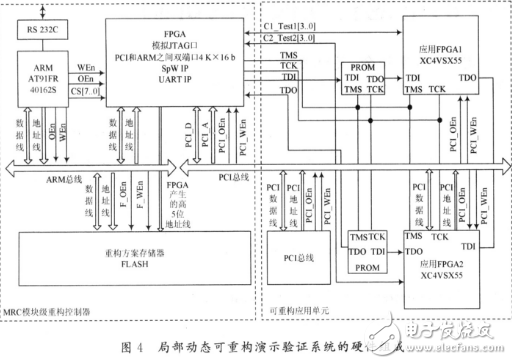

3.1 演示驗證系統(tǒng)的硬件組成及各部分功能

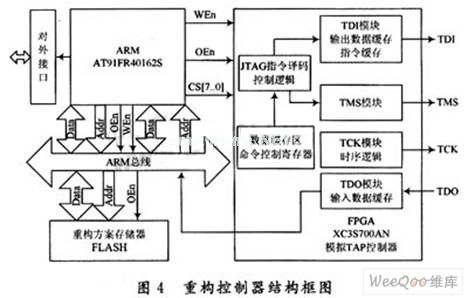

(1)演示驗證系統(tǒng)的硬件組成,如圖4所示。ARM處理器片內(nèi)具有256 KB的片上SRAM存儲器、2 MB容量FLAsH存儲器。主要是對sPARTEN-3AN系列的FPGA進(jìn)行控制,控制其調(diào)取FLASH存儲器中的重構(gòu)方案;FLAsH存儲器的并行數(shù)據(jù)通過ARM轉(zhuǎn)換成串行;ARM中自帶的FLAsH存儲器用來存放程序;

(2)SPARTEN3AN系列的FPGA,是基于非易失性存儲的FPGA,主要作為PCI總線和ARM處理器之間的雙端口;放置Spw IP核、UART IP核、1553 IP核;模擬JTAG口;

(3)兩個XCVSX55的FPGA專用JTAG,進(jìn)行配置文件的下載。Xilinx FPGA基于SRAM技術(shù),因此是易失性的。如果關(guān)掉器件的電源,其配置就會丟失。在生產(chǎn)型環(huán)境中,F(xiàn)PGA通常使用外部存儲器件(如PROM)防止停電時丟失配置數(shù)據(jù);

(4)FLASH存儲器容量為16 M×32 b,用于處理器的上電引導(dǎo)和存放多個用于模塊級FPGA重構(gòu)方案;

(5)兩個PROM-XCF32P。Virtex4系列XC4-VSX55FPGA,其配置PROM為XCF32P,32 Mb存儲容量。利用XCF32P的設(shè)計修訂(Design.Revisiorling)功能將FPGA多種配置存儲為不同的修訂版本,從而簡化FPGA配置更改。上電時,由配置PROM的內(nèi)部邏輯對設(shè)計修訂版本選擇輸入(引腳或控制位)進(jìn)行采樣;

(6)兩組測試線,每組4根,cl_Test[3..O]和C2-Testl[3..O]分別測試兩個XCVSX55系列FPGA的重構(gòu)和反饋重構(gòu)結(jié)果;

(7)兩通道的PROM控制信號線,C1(C2)_PROG,C1(C2)_DIN,C1(C2)_DONE,C1(C2)_INT,C1(C2)_CCLK用于實現(xiàn)兩個XCVSX55系列FPGA的PROM方式的下載。由于JTAG(邊界掃描)鏈在其中一個部件發(fā)生故障時會影響整個JTAG鏈的正常功能,因此多使用:PROM的下載方式備用;

(8)一路RS-232驅(qū)動接收器,實現(xiàn)和外部通信的接口;

(9)PCI總線,通過該總線實現(xiàn)計算機與外界交互的外部接口。

3.2 演示驗證系統(tǒng)的工作原理

3.2.1 上電復(fù)位

在上電復(fù)位時,要確保ARM和FPGA同步復(fù)位。Xilinx公司的FPGA上電時需要200 ms左右的配置時間,在此期間I/O引腳處于三態(tài)狀態(tài),因此對關(guān)鍵的輸入/輸出信號(如IRQx,NWAIT,2.56兆輸出數(shù)據(jù)及輸出時鐘)有必要采取的上下拉,以確保ARM及外圍接口信號處于正常的狀態(tài),避免信號沖突。

3.2.2 初始化

主要的初始化工作有2部分,分別由ARM和FPGA完成。

(1)ARM執(zhí)行的初始化工作。包括監(jiān)控程序自舉→監(jiān)控程序執(zhí)行ARM內(nèi)部寄存器初始化→硬件自檢→加載標(biāo)志檢測→(軟件更新加載)→FPGA參數(shù)設(shè)定→用戶軟件加載及完整性正確性校驗→控制權(quán)叫用戶軟件→用戶軟件初始化→用戶軟件運行。

(2)FPGA執(zhí)行的初始化工作。主要有FPGA內(nèi)部寄存器和邏輯狀態(tài)的初始值、內(nèi)部緩沖區(qū)數(shù)據(jù)清零依靠復(fù)位信號來完成。其中的“FPGA參數(shù)設(shè)定”由監(jiān)控程序負(fù)責(zé)執(zhí)行或由FPGA使用缺省參數(shù)完成。數(shù)據(jù)融合格式、輸入/輸出碼速率等FPGA參數(shù)存儲在ARM的片內(nèi)FLASH中的FPGA參數(shù)區(qū)中,上電或復(fù)位時有監(jiān)控軟件負(fù)責(zé)加載和初始化。

3.2.3 重構(gòu)過程

可重構(gòu)演示驗證系統(tǒng)的結(jié)構(gòu)如圖4所示,當(dāng)出現(xiàn)錯誤和發(fā)生故障時,由ARM處理器讀取FLASH存儲器中的重構(gòu)方案。但是,F(xiàn)LASH存儲器取舍眾多重構(gòu)方案卻是受外部1553B,Spw,UART的控制。由ARM處理器更新FLASH存儲器或給完成并/串轉(zhuǎn)換的FPGA發(fā)出控制命令來對可重構(gòu)應(yīng)用單元進(jìn)行操作。模擬JTAG口的FPGA與兩個應(yīng)用FPGA的JTAG口邊界掃描鏈(Boundary-Scan Chain),在ARM處理器的控制下,對被重構(gòu)的FPGA進(jìn)行重構(gòu)。FPGA的主要任務(wù)是通過ARM控制器將事先存入FLASH中邏輯系統(tǒng)的不同功能配置信息,按用戶的系統(tǒng)時序要求和外部控制,逐一下載到SRAM編程的FPGA之中,以實現(xiàn)系統(tǒng)功能的動態(tài)局部重構(gòu)。在系統(tǒng)工作過程中,F(xiàn)PGA將根據(jù)不同的要求,在處理器的控制下,不斷重構(gòu)其邏輯功能,通過模板級重構(gòu),滿足不同數(shù)字圖像處理和其他邏輯運算的要求。

3.3 實現(xiàn)局部動態(tài)可重構(gòu)的FPGA的選型和配置模式

3.3.1 Xilinx公司的Virtex-4系列FPGA

在選擇器件時,必須保證器件資源留有一定余量,這樣不僅可以避免布線擁擠,也便于測試修改和功能擴展。根據(jù)系統(tǒng)的需求和擴展性,選擇Virtex-4系列FPGA。它是Xilinx公司推出的一系列實現(xiàn)動態(tài)局部重構(gòu)的FPGA芯片,也是基于查找表的。Virtex-4系列芯片將高級硅片組合模塊(ASMBL)架構(gòu)與種類繁多的靈活功能相結(jié)合,大大提高了可編程邏輯設(shè)計能力,從而成為替代ASIC技術(shù)的強有力產(chǎn)品。采用Virtex-4選用Xilinx公司的Virtex-4系列產(chǎn)品XC4VSX55。XC4VSX55具有128列×48行陣列,55 296個邏輯單元,24 576個Slice,最大分布式RAM384 KB,512個XtremeDSPSlice),320個18 KB塊RAM,最大塊RAM存儲容量5 760 KB,8個DCM,4個相位匹配時鐘分頻器(PMCD),13個I/O組,最大用戶I/O數(shù)640個。根據(jù)目前已有的算法,其性能和資源可以較好地滿足圖像匹配算法和目標(biāo)識別算法對硬件資源(邏輯門數(shù)、RAM大小、乘法加法器等)的需求。Virtex-4硬IP核塊的龐大陣列包括PowerPC處理器(帶有新型APU接口)、三態(tài)以太網(wǎng)MAC,622 Mb/s到6.5 Gb/s串行收發(fā)器、專用DSP S1ice、高速時鐘管理電路和源同步接口塊。

3.3.2 Virtex-4系列FPGA在該系統(tǒng)中的配置模式

Virtex-4器件的配置方法是用串行從模式、串行主模式、SelectMAP從模式、SelectMAP主模式、邊界掃描模式(JTAG)之一將比特流載入內(nèi)部配置存儲器的:在該系統(tǒng)中采用可重構(gòu)應(yīng)用單元的FPGA配置模式有兩種:

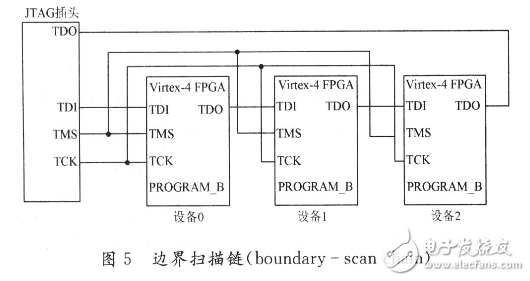

(1)JTAG方式(邊界掃描方式)

通過SPARTEN-3AN系列中FPGA提供的外部邏輯驅(qū)動JTAG專用引腳與同樣4個JTAG引腳的兩個應(yīng)用FPGA及配置它們的PRROM串聯(lián)起來,形成邊界掃描鏈(Boundary-Scan Chain)將配置數(shù)據(jù)下載到FPGA中。在這種模式下,數(shù)據(jù)以每TCK一位的速度加載,如圖5所示。

JTAG或邊界掃描模式是一種行業(yè)標(biāo)準(zhǔn)的(IEEE1149.1或1532)串行編程模式。該模式通過電纜、微處理器或其他器件提供的外部邏輯驅(qū)動JTAG專用引腳TCK和JTAG測試時鐘輸入。當(dāng)TCK保持在零狀態(tài)時,測試邏輯狀態(tài)應(yīng)保持不變;TMS為測試模式選擇,控制JTAG狀態(tài)。出現(xiàn)在TMS的信號在TCK的上升沿由測試邏輯采樣進(jìn)入測試訪問口(Test AccessPort,TAP)控制器;TDI:測試數(shù)據(jù)輸入,測試數(shù)據(jù)在TCK的上升沿采樣進(jìn)入移位寄存器(SR);TD0:測試數(shù)據(jù)輸出,測試結(jié)果在TCK的下降沿從移位寄存器(SR)移出,輸出數(shù)據(jù)與輸入到TDI的數(shù)據(jù)應(yīng)不出現(xiàn)倒置。這種模式因其標(biāo)準(zhǔn)化程度和可通過同樣4個JTAG引腳為FPGA編程的能力而廣泛使用。JTAG方式常用于實現(xiàn)在線編程(In-System Programma-ble,ISP),對FPGA進(jìn)行編程。

JTAG在線編程的特征也改變了傳統(tǒng)生產(chǎn)流程,將以前先對芯片進(jìn)行預(yù)編程再裝到板上的工藝簡化為先固定器件到電路板上,再用JTAG口進(jìn)行編程。Xilinx的Virtex-4系列支持在一個邊界掃描(JTAG)鏈中配置多個FPGA,每次,只配置鏈中的1個FPGA,大大降低了實現(xiàn)難度。

(2)PROM配置模式,是由SPARTEN3AN系列FPGA為每一個Virtex-4系列FPGA配置一組PROM控制線實現(xiàn)FPGA的下載。SPARTEN3AN系列FPGA和可重構(gòu)應(yīng)用單元的每一個virtex-4系列FPGA之間分別有一組PROM的控制線,每組都包括DIN(配置數(shù)據(jù)輸入)、CCLK(配置時鐘)、DONE(FP-GA配置完成)、PROG(觸發(fā)重配置)、INT(配置初始化)5個信號,通過這些信號將配置數(shù)據(jù)下載到Virtex-4系列FPGA中去。兩種方式互補,在邊界掃描鏈發(fā)生斷裂影響到整個鏈的功能時,可以使用PROM模式替補,提高了重構(gòu)過程的可靠性。

4 結(jié) 語

基于SRAM的FPGA的問世標(biāo)志著現(xiàn)代可重構(gòu)技術(shù)的開端,并極大地推動了其發(fā)展。可編程FPGA可以根據(jù)不同算法設(shè)計合理的硬件結(jié)構(gòu),以達(dá)到提高執(zhí)行效率的目的。動態(tài)可重構(gòu)FPGA可以在程序運行中動態(tài)完成FPGA的不同配置電路功能,在不同時段執(zhí)行不同的算法,實現(xiàn)了虛擬硬件可重構(gòu)計算技術(shù)。這里提出的通過微處理器加FPGA結(jié)合串行菊花鏈實現(xiàn)可重構(gòu)的方式,實現(xiàn)了動態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計的一種應(yīng)用。另外,該驗證演示了系統(tǒng)中可重構(gòu)控制器還可以結(jié)構(gòu)模塊化,能夠工程化應(yīng)用于其他設(shè)計中,具有靈活及可移植性強的優(yōu)點。

電子發(fā)燒友App

電子發(fā)燒友App

評論