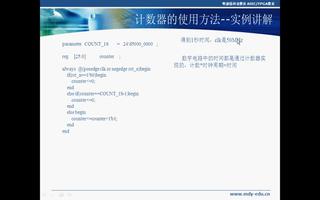

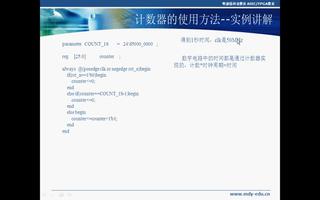

計數器應用實例

除了計數功能外,計數器產品還有一些附加功能,如異步復位、預置數(注意,有同步預置數和異步預置數兩種。前者受時鐘脈沖控制,后者不受時鐘

2010-05-27 09:37:55 5544

5544

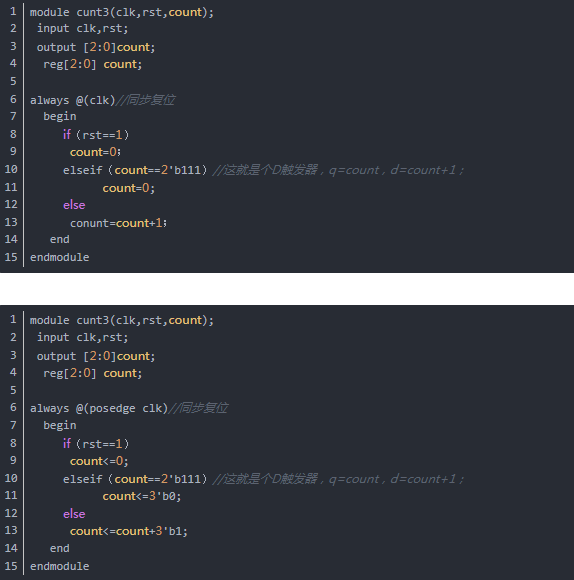

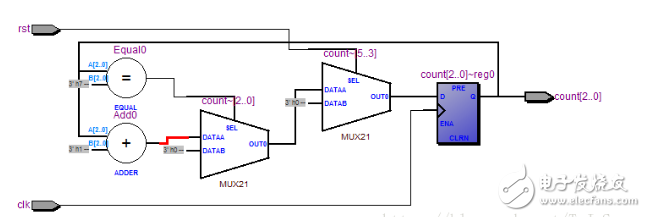

構建一個4位二進制計數器,計數范圍從0到15(包括0和15),計數周期為16。同步復位輸入時,將計數器重置為0。

2022-12-02 09:20:28 3111

3111 可預置同步4位二進制計數器;同步復位

2023-03-28 14:31:12

可預置同步4位二進制計數器;同步復位

2023-03-28 15:04:29

可預置同步4位二進制計數器;同步復位

2023-03-28 15:04:28

可預置同步4位二進制計數器;同步復位

2023-03-28 15:04:29

可預置同步4位二進制計數器;同步復位

2023-03-28 15:04:28

可預置同步4位二進制計數器;同步復位

2023-03-28 15:04:28

計數,模塊B需要1000的循環計數,那么我們就可以設計一個全局計數器,計數器位數為10,前八位供模塊A使用,整個計數器供B使用。合理的利用pll進行分頻,可以實現更靈活的全局計數器設計。4.對于FPGA

2014-12-04 13:52:40

Altera EPM7128SLC84-15,時鐘,四位八段數碼管。三、實驗內容1、用D觸發器設計異步四位二進制加法計數器。2、用JK觸發器設計異步十進制減法計數器。3、用74161兩個宏連接成八位二進制同步

2009-10-10 11:47:02

本人在用PWM信號控制電機時,計數器時基是0.5212*e-6s,計數器是16位的。能處理的最小信號頻率是29.2Hz,現在我用范圍10-29.2Hz的信號去控制,計數器計數出現溢出,請問哪位能幫我怎么去處理。謝謝。

2012-10-22 16:43:39

計數器是什么?如何使用計數器?計數器有哪些應用呢?

2022-02-28 11:08:08

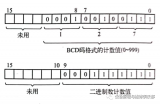

表示0~9十個數,為了擴大計數器范圍,常用多個十進制計數器級聯使用。同步計數器往往設有進位(或借為)輸出端,故可選用其進位(或借位)輸出信號驅動下一級計數器。圖9-3是由CC40192利用進位輸出 控制

2009-10-11 10:00:11

功能中,對我們組成任意進制計數器最有用的功能有復位功能、置位功能、預置數功能。復位功能:是在復位端有效時,將本計數器復位,使其狀態為“0”,即輸出端完全置“0”。但復位功能有同步復位和異步復位之別

2008-07-05 13:41:26

定時器與外部觸發的同步1.復位模式:計數器使用內部時鐘計數,然后正常運轉,直到出現TI1上升沿,當TI1出現上升沿時,計數器清零然后重新從零開始計數。TI1上升沿與實際計數器復位之間的延遲是由于

2021-08-18 06:59:12

STM8觸發同步計數器允許四種觸發輸入ETRTI1TI2來自TIM5/TIM6的TRGOTIM1的計數器使用三種模式與外部的觸發信號同步:標準觸發模式,復位觸發模式和門控觸發模式。

2020-11-09 07:06:59

移位寄存器是工作在波特率時鐘下的,所以計數器模塊的時鐘就是和波特率時鐘同步的波特率發生器提示信號 indicator,這樣每輸出一個完整的波特率時鐘周期計數器就能增加一。計數器計數的上閾是在實體聲明中定義

2018-10-23 10:02:16

一個計數器寫入,一個計數器讀取,這怎么同步

2014-11-19 21:27:52

最近在看《現代操作系統》,他提到了時鐘維持實際時間,在每個時鐘滴答將計數器加1即可實現。但要注意位溢出(32位計數器),可以通過以下方法解決:使用64位計數器:缺點是這種方法使得計數器加一操作的代價很高,1s內維護很多次計數器。我不太懂紅色字體的意思

2018-05-04 11:36:41

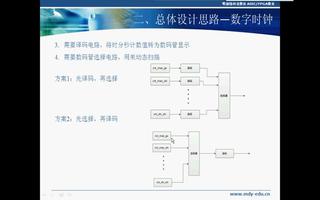

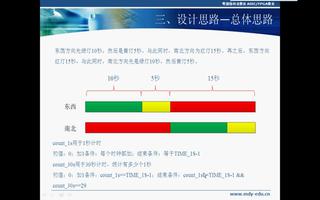

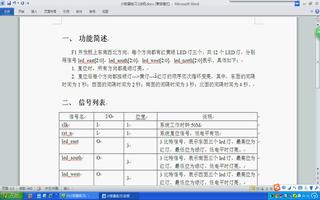

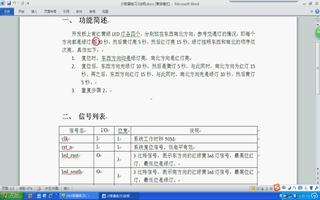

的十位,Result[3:0]代表個位,RSTn為復位輸入信號。將計數器的結果Result輸出給數碼管顯示。功能模塊圖與輸入輸出引腳說明該工程包含頂層模塊counter24與底層模塊

2022-07-05 15:14:27

1、設計一個電子秒表的計數器模塊在上一例中,使用了FPGA開發板上的撥碼開關控制四位數碼管進行動態顯示,在本例中,我們將數碼管作為一個整體IP,然后用一個計數器驅動它實現一個電子秒表的功能。根據這一

2022-07-29 14:57:01

如何使用FRESOC制作8個8位計數器?我有FeleSOC開發板。我想做一個8×8位計數器與8個輸入時鐘。計數器相互獨立。每個計數器都應該能夠在計數器值溢出時產生中斷,即當計數器從255溢出到0時。我的最大頻率是每頻道370赫茲。

2019-09-18 14:50:03

如何使用FRESOC制作8個8位計數器?我有FeleSOC開發板。我想8輸入時鐘進行8*8位計數器。計數器相互獨立。每一個能夠產生中斷時,計數器的值溢出,當計數器溢出from255 0。我的最大頻率是每頻道370赫茲。

2019-09-18 13:48:42

的計數器,從而確保所有 8 個 PWM 計數器之間的同步。 我的問題正是因為需要引入這第九個渠道而產生的。 現在我想問的是,這第九個通道由不同的 TGC 控制是否有問題(例如 TGC0 控制產生 PWM

2024-03-04 08:19:48

我一直在試驗如何在Vivado中“解釋”簡單計數器上的異步與同步復位。這是我的(10位)計數器模板:圖書館IEEE;使用IEEE.STD_LOGIC_1164.ALL

2019-04-25 07:57:01

如何構建一個具有同步復位端的CMOS四進制計數器?輸入端 復位控制信號RESET 時鐘信號clk輸出端 Q3 Q2 Q1 Q0 carry

2016-12-10 17:56:10

獲取,并通過TD700N22KOF_TIM信號到達 TOM,但同時,如果外部復位信號未到來,定時器計數器必須能夠自行復位,保證PWM周期。

參考上圖,由于 EXT_TRIG 和 RST_CCU0

2024-03-06 08:09:01

8253微機接口芯片作為定時器和計數器時實質相同嗎?定時器/計數器8253內部有多少個16位的計數器?

2021-10-20 06:16:30

、T1的啟動和停止計數,同時包含了T0、T1的狀態。單片機復位時,兩個寄存器的所有位都被清0。4種工作方式(方式0-方式3):M1 M0 工 作 方 式0 0 方式0,13位定時器/計數器。0 1 方式1,16位定時器/計數器。1 0 方式2,8位常數自動.

2022-02-28 10:42:12

兩個32位計數器,但我希望這些計數器的計數速率高達3GHz。看起來低端FPGA(即Spartan 6)的最大頻率為200-300 MHz。因此,我計劃使用離散ECL邏輯在片外實現4個LSB,并在FPGA

2019-04-19 13:34:34

怎么實現基于單片機和FPGA的多功能計數器的設計?

2021-05-14 06:57:15

則整個系統開始工作,其上升沿易同步于clk(3)statr是啟動信號,一個clk時鐘周期的正脈沖,同步于clk。alarm[7:0]是配置信息,單位為秒,同步于clk(4)工作模式:收到start后,秒計數器sec_cnt從零開始以秒為單位來計數,計數到alarm[7:0]指定的數值時,產生一個

2021-07-22 07:05:11

16位定時/計數器是什么?怎樣通過TMOD寄存器設置16位定時/計數器的工作模式?怎樣通過TCON寄存器的TF0/TF1位判斷16位定時/計數器是否溢出?

2021-07-16 09:12:26

大家好,感謝您在任何的幫助,我是一個學生,需要使用一個32位的計數器quaddec大小,所以我創建了一個長整型變量來存儲它的價值,因為我需要把它通過UART接口作為字符串來捕捉正交的信息,這里的事情

2019-09-03 12:13:16

使用計數器生成內部復位的推薦寫法?

2023-08-11 06:10:24

求高手幫忙,整一個FPGA 8位 計數器 十進制 的怎么搞!

2012-11-02 00:18:20

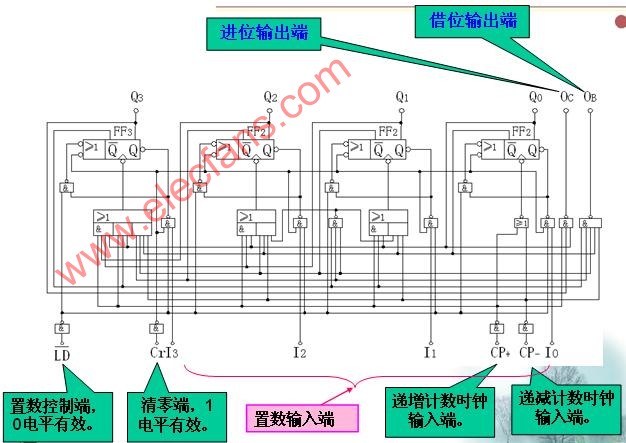

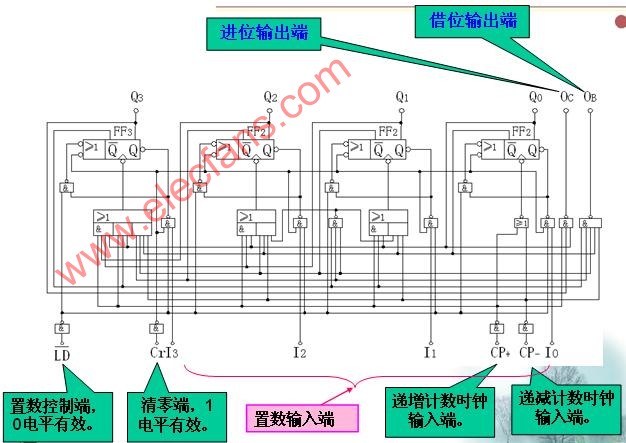

TTL 二進制同步可逆計數器

2009-08-03 09:05:53 26

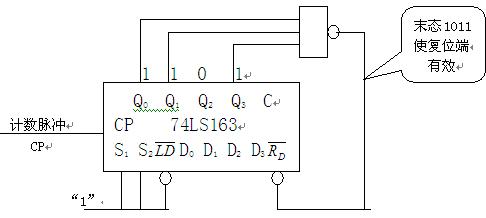

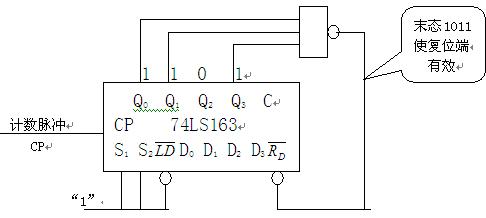

26 在具有同步復位功能的集成計數器中使用復位法(同步復位法),和在具有異步復位功能的集成計數器中使用復位法(異步復位法)是有區別的。這是由同步復位功能與異步

2008-07-05 14:13:15 10647

10647

我們可以采用具有保持功能的同步集成計數器(如74LS160)組成同步計數器,電路如圖3-4所示。在160計數器中當S1=S2

2008-07-05 14:17:49 4408

4408

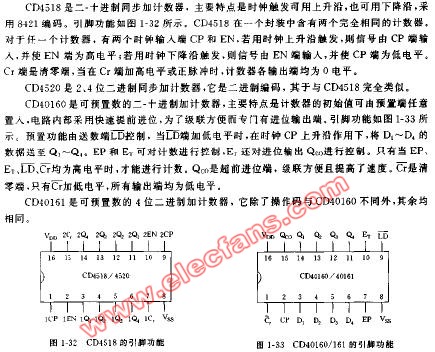

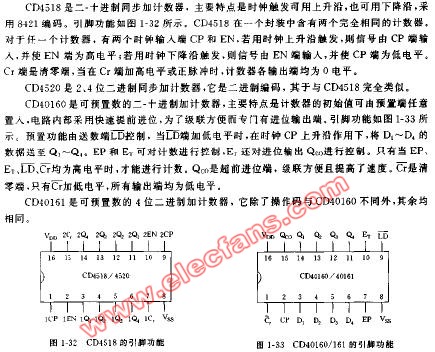

同步計數器的應用:詳細介紹CD40161芯片.

2008-12-17 14:33:18 972

972

第二十五講 同步計數器

7.3.2 同步計數器一、同步二進制計數器1.同步二進制加法計數器JK觸發器組成的4位同步二進制加法

2009-03-30 16:28:45 8597

8597

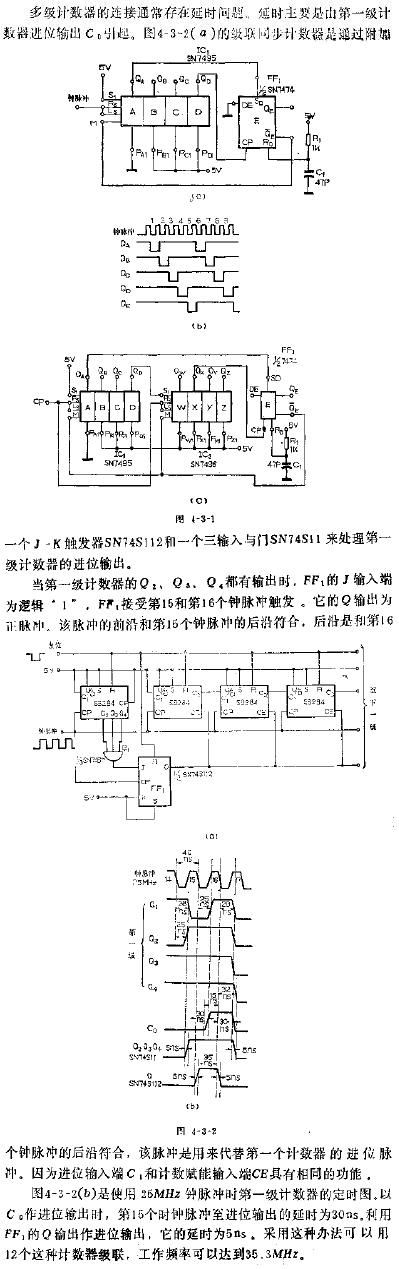

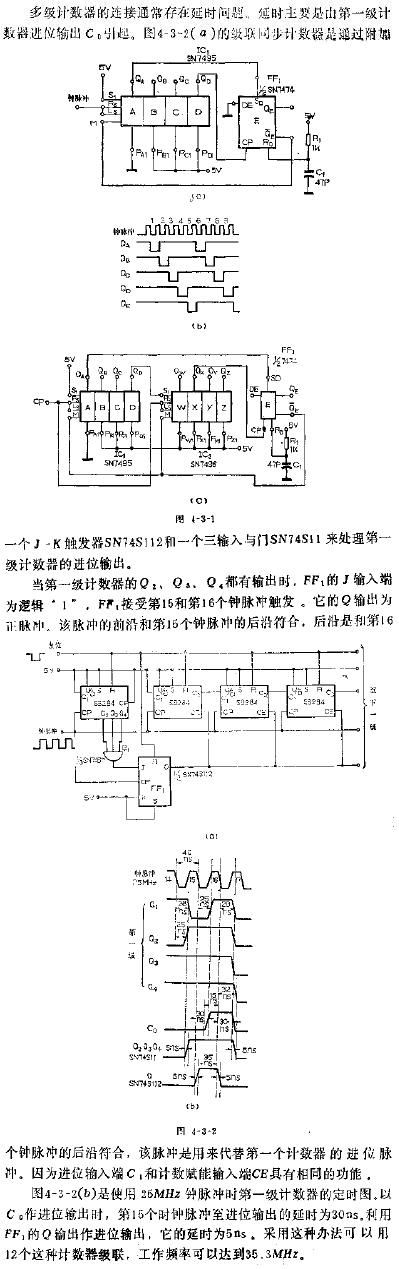

寬頻帶級聯同步計數器

2009-04-10 10:24:56 687

687

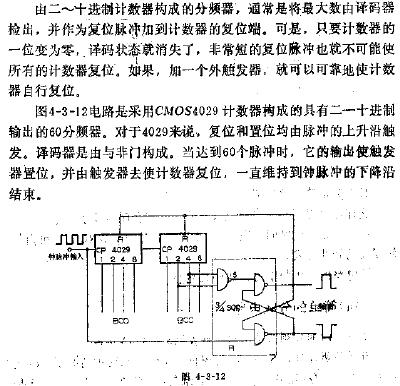

用一個外加觸發器使計數器可靠的自行復位

2009-04-10 10:27:12 393

393

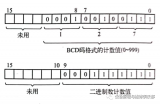

8421碼同步十進制遞增計數器

2009-09-24 11:09:34 6125

6125

T1192型同步十進制可逆計數器

2009-09-24 11:10:59 1352

1352

同步二進制計數器

1. 同步與異步二進制加法計數器比較態序表和工作波形一樣電路結構不同: 異步二進制加法

2009-09-30 18:37:29 11186

11186

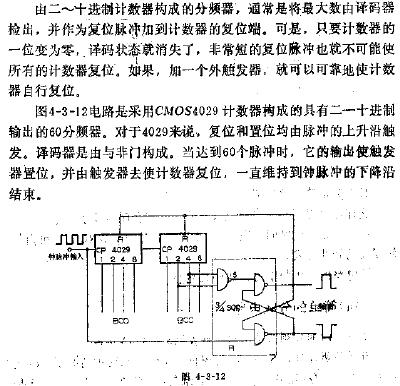

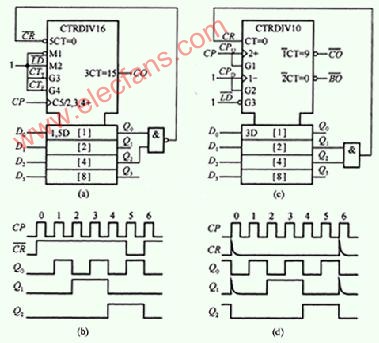

利用復位端構成的模6計數器電路

利用集成計數器的預置端和復位端可以構成任意模計數器。下圖所示依次是利用74163和74192構成的

2010-01-12 13:54:31 4688

4688

計數器的同步擴展

2010-01-12 13:57:16 996

996

環形計數器和扭環形計數器

移位寄存器也可以構成計數器,稱為移位型計數器。它有兩種結構:環形計數器和扭環形計數器。

2010-01-12 14:07:46 9173

9173 簡單改變FPGA計數器規格使作為DAC功能PWM計數器的紋波降低。

2012-04-06 11:11:57 1856

1856

介紹計數器的基本原理(如異步,同步二進制計數器,以及對誤差,性能的分析)

2015-12-17 14:52:39 3

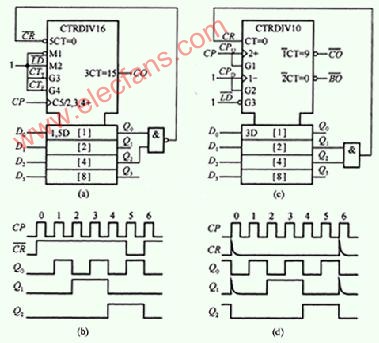

3 數字電子技術--中規模集成計數器及其應用--同步、異步二五十進制計數器-PPT

2016-03-22 14:33:06 0

0 1、了解時序電路的經典設計方法(D觸發器、JK觸發器和一般邏輯門組成的時序邏輯電路)。

2、了解同步計數器,異步計數器的使用方法。

3、了解同步計數器通過清零阻塞法和預顯數法得到循環任意進制

2022-07-10 14:37:37 15

15 本文主要介紹了74LS161集成計數器電路(2、3、4、6、8、10、60進制計數器)。74LS161是4位二進制同步計數器,該計數器能同步并行預置數據,具有清零置數,計數和保持功能,具有進位輸出

2018-01-18 10:56:39 353115

353115

異步復位同步釋放 首先要說一下同步復位與異步復位的區別。 同步復位是指復位信號在時鐘的上升沿或者下降沿才能起作用,而異步復位則是即時生效,與時鐘無關。異步復位的好處是速度快。 再來談一下為什么FPGA設計中要用異步復位同步釋放。

2018-06-07 02:46:00 1989

1989 對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 計數器

2019-09-03 06:15:00 1482

1482

計數器

2019-09-03 06:14:00 1422

1422

計數器

2019-09-03 06:10:00 2856

2856

計數器

2019-09-03 06:09:00 2484

2484

計數器

2019-09-03 06:08:00 1809

1809

計數器

2019-09-03 06:06:00 2556

2556

計數器

2019-09-03 06:04:00 5364

5364

計數器

2019-09-03 06:02:00 1921

1921

計數器

2019-09-03 06:01:00 2800

2800

同步計數器之所以被稱為是因為計數器內所有單個觸發器的時鐘輸入都由同一時鐘信號同時同時計時。

2019-06-23 10:16:39 24564

24564

采用同步清零或置數方式完成的計數器,一般不會出現競爭冒險現象,而采用異步清零或置數方式完成的計數器往往會出現競爭冒險現象。以 74LS160 同步計數器( 異步復位、同步置數) 組成的 7 進制

2019-08-28 08:00:00 7

7 本文檔的主要內容詳細介紹的是同步7進制計數器的設計資料免費下載。

2020-05-20 08:00:00 11

11 計數器清零就是將計數值清零,那么計數器同步清零和異步清零之間有什么區別呢?

2022-01-29 16:45:00 28895

28895 電子發燒友網站提供《FPGA上的十六進制計數器.zip》資料免費下載

2022-11-23 10:47:06 7

7 電子發燒友網站提供《Xilinx Spartan 6 FPGA上的0到999計數器.zip》資料免費下載

2022-11-23 10:27:06 2

2 本方案是一個基于 FPGA ?的十進制計數器。共陽極 7 段顯示器上的 0 到 9 十進制計數器,硬件在 Xilinx Spartan 6 FPGA 板上實現。

2022-12-20 14:52:25 2

2 可預置同步4位二進制計數器;異步復位-74LVC161

2023-02-15 19:23:09 0

0 可預置同步4位二進制計數器;同步復位-74LVC163

2023-02-16 20:48:19 0

0 可預置同步4位二進制計數器;異步復位-74HC161_Q100

2023-02-16 21:10:00 1

1 可預置同步4位二進制計數器;異步復位-74HC161

2023-02-16 21:10:17 2

2 可預置同步BCD十進制計數器;異步復位-74HC160

2023-02-20 20:05:50 10

10 可預置同步4位二進制計數器;同步復位-74HC_HCT163_Q100

2023-02-21 18:35:38 0

0 可預置同步4位二進制計數器;同步復位-74HC_HCT163

2023-02-21 18:35:57 0

0 在數字電子產品中,計數器是由一系列觸發器組成的時序邏輯電路。顧名思義,計數器用于計算輸入在負或正邊沿轉換中出現的次數。根據觸發觸發器的方式,計數器可以分為兩類:同步計數器和異步計數器。了解這兩種計數器的工作原理以及它們之間的區別。

2023-03-25 17:31:07 18649

18649

加計數器(S_CU)在計數初始值預置輸入端S上有上升沿時,PV裝入預置值,輸入端CU每檢測到一次上升沿,當前計數值CV加1(前提是CV 小于999);當前計數值大于0時,Q輸出為高電平“1”;當R端子的狀態為“1”時,計數器復位,當前計數值CV為“0”,輸出也為“0”。加計數器指令和參數見圖2

2023-04-27 15:38:22 1437

1437

同步計數器和異步計數器的區別詳解 同步計數器和異步計數器是數字電路中兩種常見的計數器類型,它們在實現方式和功能上存在明顯的區別。本文將詳細介紹同步計數器和異步計數器的區別,包括其工作原理、特點

2023-12-13 14:54:24 1724

1724 同步計數器和異步計數器是兩種常見的數據結構,它們都用于控制對共享資源的訪問。它們的主要作用是實現多個線程之間的同步和并發控制。盡管它們都被用于同步的目的,但它們有很多不同的特點和用例。 同步計數器

2023-12-15 10:49:43 514

514 計數器是一種被廣泛應用于各個領域的實用工具,在我們的日常生活中隨處可見。無論是進行時間統計,協助工作任務的完成,還是用于科學研究和編程技術,在各個領域都起到了重要的作用。本文將詳細介紹計數器

2024-02-03 10:04:14 589

589 計數器是計算機領域中常用的一種數據結構,用于記錄和控制程序執行中的指令或事件發生的次數。計數器可以根據同步機制或異步機制進行操作。本文將詳細討論計數器的同步性和異步性,深入探討兩者的區別及其在實際

2024-02-22 15:14:02 243

243

電子發燒友App

電子發燒友App

評論