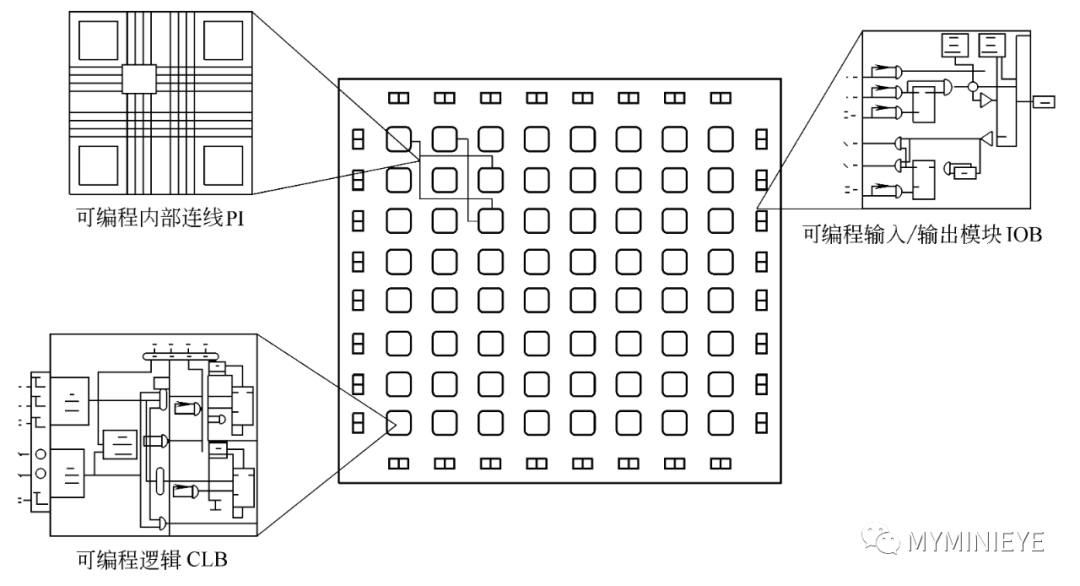

一、XADC簡介

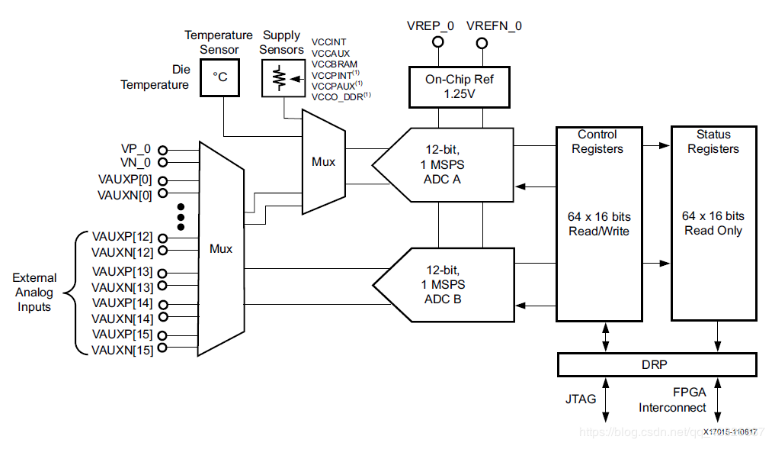

XADC模擬輸入包括專用模擬輸入VP/VN和16組復用模擬信號輸入VAUX(15:0);XADC轉換結果可以通過動態重配接口(DRP)或者JTAG接口輸出;告警信號可通過ALM(7:0)輸出,并有專用的溫度告警信號OT。

XADC還包括幾個支持測量芯片上電源電壓和模具溫度的片上傳感器。ADC轉換數據存儲在稱為狀態寄存器的專用寄存器中。這些寄存器可以通過FPGA互連訪問,使用一個16位同步讀寫端口,稱為動態重新配置端口(DRP)。ADC轉換數據也可以通過JTAG TAP訪問,可以在配置之前(預配置),也可以在配置之后訪問。對于JTAG TAP,用戶不需要實例化XADC,因為它是一個專用接口,使用現有的FPGA JTAG基礎結構。正如后面所討論的,如果XADC沒有在設計中實例化,則設備以預定義的模式(稱為默認模式)運行,該模式監視芯片上的溫度和電源電壓。

?

?

具體的參考手冊如下:

?

ug480:7Series_XADC.pdf

xapp795:driving-xadc.pdf

xapp554:xadc-layout-guidelines.pdf

xapp1203:post-proc-ip-zynq-xadc.pdf

xapp1183:zynq-xadc-axi.pdf

xapp1182:zynq_axi_xadc_mon.pdf

xapp1172:zynq_ps_xadc.pdf

pg019:axi_xadc.pdf

pg091:xadc-wiz.pdf

ug953:vivado-7series-libraries.pdf

ug585:Zynq-7000-TRM.pdf

?

二、XADC的配置方法

本文采用vivado編譯環境對XADC進行配置。

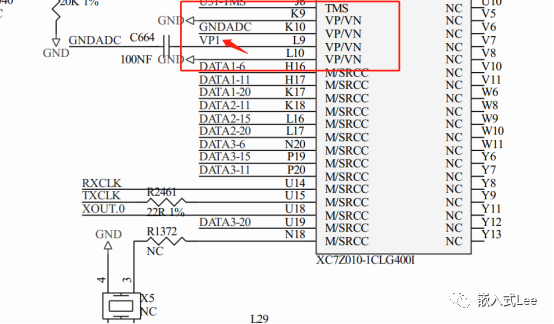

在對XADC進行寄存器配置之前,首先要在vivado中進行硬件電路的搭建,這部分內容可以通過建立block塊完成,具體配置方法請參考https://blog.csdn.net/taowei1314520/article/details/83656386。本文借助外部VPVN測量端口,通過搭建惠斯頓電橋進行溫度的測量(具體方法后面會詳細介紹到),所以需要在搭建硬件電路時引出VPVN和配置XDC管腳約束。

?

2.1 配置寄存器

在配置寄存器之前,首先要對兩種寄存器進行解釋說明。

控制寄存器:用于控制和確定處理器的操作模式以及當前執行任務的特性。

狀態寄存器:用來存放兩類信息,一類是體現當前指令執行結果的各種狀態信息,另一類是存放控制信息。

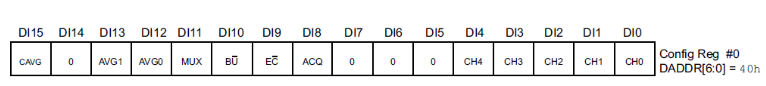

1.配置控制寄存器Configuration register 0

通過寫入C_BASEADDR + 0x300(基地址+偏移量)來定位到該寄存器的位置,下圖為該寄存器的bit位對照圖。

?

?

CAVG:這個比特位用于禁用計算校驗系數的平均,使能為0,使能為1(平均固定在16個樣本)。

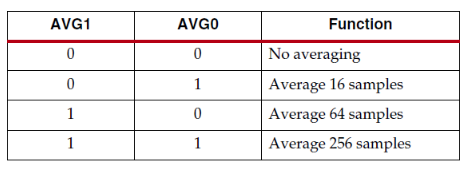

AVG1、AVG0:這些位用于在單通道和序列模式下設置所選通道上的樣本平均量。

?

?

MUX:這個比特位為外部多路復用,設置1即啟動外部多路復用功能。(本文所采用的的VP/VN位專用PL端引腳,所以這里不進行多路復用)。

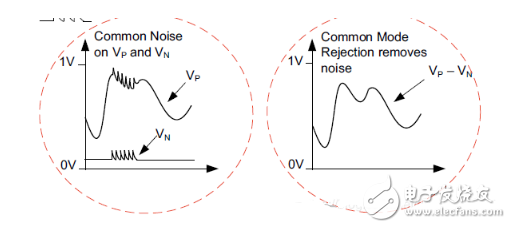

BU:這個比特位是進行單雙極性的選擇,雙極性為1,單極性為0。本文采用的是模擬差分的輸入方式,因為差分輸入能夠有效地降低干擾,實現數據更加穩定地傳輸。

?

?

EC:這個比特位用于為XADC采樣模式,1為event-driven sampling mode,0為continuous sampling mode。

event-driven sampling mode:該工作模式下,采樣瞬間和隨后的轉換過程由一個稱謂轉換開關的觸發信號啟動,當需要對采樣的時刻進行精確控制時,采用該模式。在該模式下,DCLK必須始終存在。

continuous sampling mode:該工作模式下,ADC在當前轉換周期結束時自動啟動新的轉換,adc持續對選定的模擬輸入進行轉換,模數轉換過程由采集階段和轉換階段兩部分組成。

ACQ:在使用單通道模式時,該位用于將連續采樣模式下的外部模擬輸入的可用時間增加6次ADCCLK周期,如果沒有設置ACQ位,則在收購的最后階段允許使用4個ADCCLKs或150個ns。通過將此位設置為邏輯1,可以增加獲取時間。

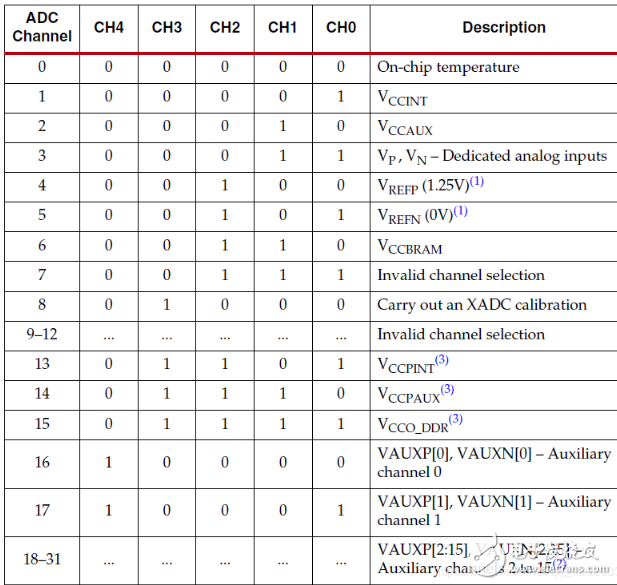

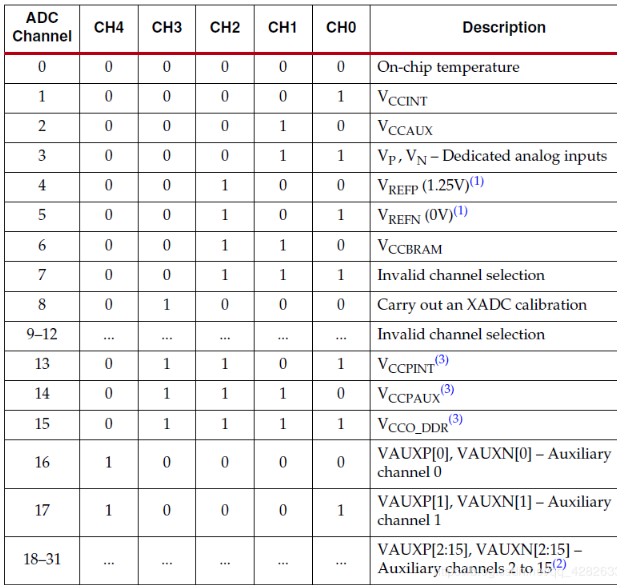

CH4~CH0:在單通道模式或外部多路復用模式下工作時,這些位用于選擇ADC輸入通道。

?

?

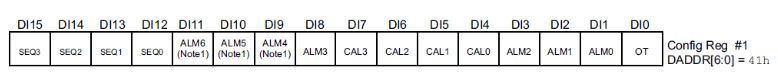

2. 配置控制寄存器Configuration register 1

通過寫入C_BASEADDR + 0x304(基地址+偏移量)來定位到該寄存器的位置,下圖為該寄存器的bit位對照圖。

?

?

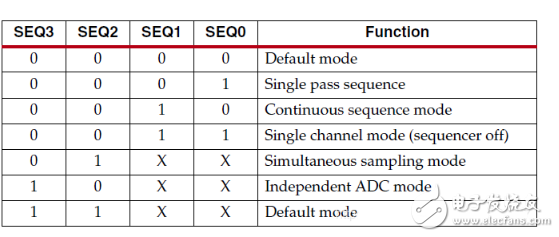

SEQ3~SEQ0:這些比特位用來使能通道序列。

?

Default mode:在這種操作模式下,XADC自動監控芯片上的傳感器,并將結果存儲在狀態寄存器中。這兩種adc都是在這種模式下校準的,所有傳感器都使用平均16個樣本。XADC在此模式下獨立于任何其他控制寄存器設置操作。

Single Pass Mode:在這種操作模式下,序列操作一次通過序列通道寄存器,然后停止。

Continuous sequence mode:該模式相當于single pass mode的自動版,在一次操作結束后又會自動重新開始。

Simultaneous Sampling Mode:在該模式下,測序器通過8對輔助模擬輸入通道自動進行同步采樣和轉換,這在需要保留兩個信號之間的相位關系的應用程序中非常有用,大部分用于多路復用情況下。

Auxiliary analog channels 8 to 15 are assigned to ADC B and are nominated as B channels

Independent ADC Mode:通常用于報警模式和監測模式,在這種模式下,警報輸出使能,并且使用者必須正確地配置報警閾值。與默認的測序模式一樣,平均值固定在16個采樣點。

ALM6~ALM0:這些位用于禁用溫度的單個警報輸出,1為禁用報警輸出。

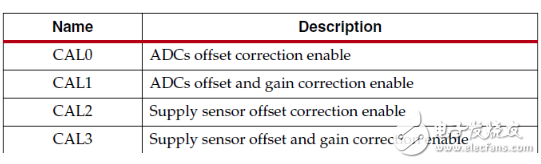

CAL3~CAL0:這些位使校準系數應用于ADC和片上供應傳感器測量,1為使能校準,0位不使能。

?

?

OT:這個位用于禁用溫度過高信號。通過將此位設置為邏輯1來禁用警報。

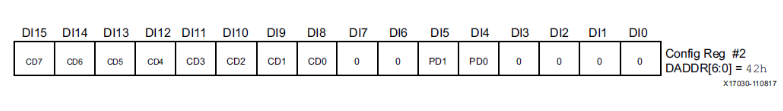

3. 配置控制寄存器Configuration register 2

通過寫入C_BASEADDR + 0x308(基地址+偏移量)來定位到該寄存器的位置,下圖為該寄存器的bit位對照圖。

?

?

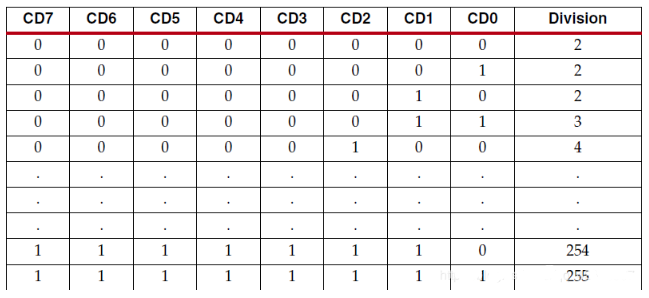

CD7~CD0:這些位用于選擇ADC的DRP時鐘(DCLK)和低頻率ADC時鐘(ADCCLK)之間的分頻比。

DRP:動態配置端口,可直接通過PL部分訪問,也可以通過高級接口單元。

所有XADC計時同步到DRP時鐘(DCLK)。ADCCLK是通過將DCLK在配置寄存器2中分頻得到的。

?

?

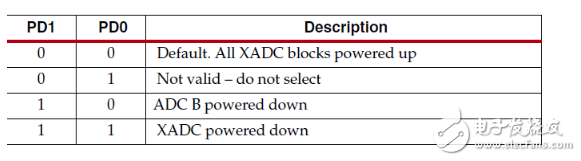

PD1、PD0:XADC的中斷位。通過設置PD1 = PD0 = 1,可以永久關閉整個XADC塊。

?

?

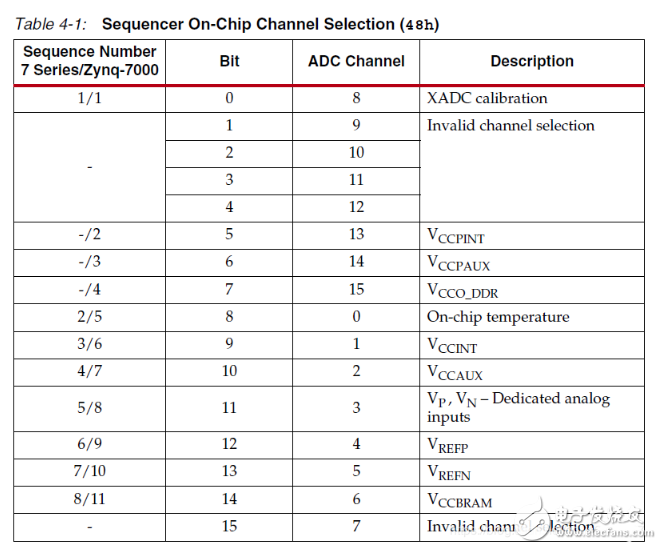

4. 配置序列寄存器Sequence Register 0:首先寫入C_BASEADDR + 0x320(基地址+偏移量)來定位到該寄存器的位置,再通過寫bit位來選擇序列通道,本文采用VPVN序列通道,所以給第12位置1(0000_1000_0000_0000),具體對應表如下。

?

?

5. 配置輸出寄存器:通過寫入C_BASEADDR + 0x20C(基地址+偏移量)來定位到該寄存器的位置,在專用模擬輸入通道(Vp/Vn)上A/D轉換的12位MSB驗證結果存儲在此寄存器中。

?

?

2.2 結果換算

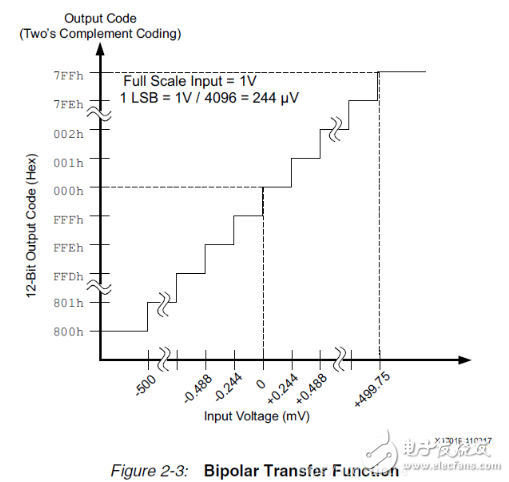

定義和一些計算所應用到的數據位數為16位(unsigned short),而我們所用到的只有12位,所以需要將數據進行右移4位來保證12位MSB驗證結果能夠完整的存儲到寄存器中。

將ADC的外部模擬輸入通道配置為雙極時,它們可以容納真正的差分和雙極模擬信號類型。雙極模式下ADC的輸出編碼是雙極模式下的補碼,用來表示VP上輸入信號相對于VN的符號。設計代碼轉換發生在連續整數LSB值,也就是說,一個LSB、兩個LSB、三個LSB等。伏特的LSB大小即1個數據位等于244uV。

?

?

?

2.3 溫度采集

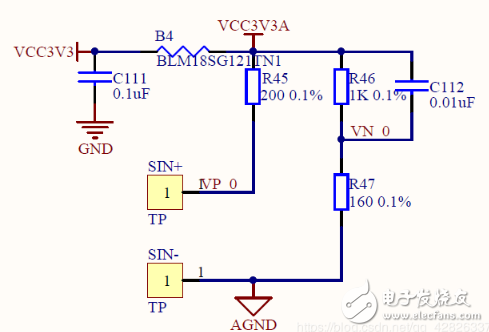

本文采用PT100熱電阻作為外部溫度測量器件,通過搭建惠斯頓電橋,實現溫度的采集。

1、將XADC在PL端的VPVN引腳直接接在電橋上,利用Pt100在不同溫度下電阻值發生變化的原理,實現VP/VN電壓差的改變,根據公式計算得出溫度值,下圖為惠斯頓電橋。

?

?

計算公式:

V=VP0?VN0 V = VP0 - VN0V=VP0?VN0

Rpt=(13200+29000V)/(412.5?145V) Rpt = (13200 + 29000V)/(412.5 - 145V)Rpt=(13200+29000V)/(412.5?145V)

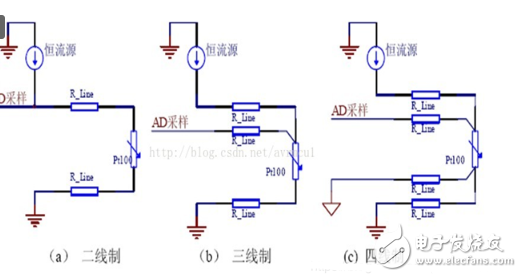

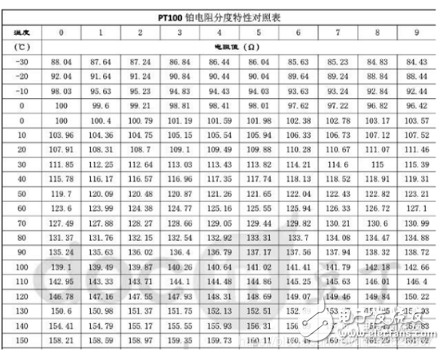

通過查找表或公式計算的方法,將電阻值轉換為對應的溫度值,以下給出“PT100溫度-電壓”對照表和各種類型的接線法。

?

?

a.二線制接法:如圖4(a)所示,這種接法不考慮Pt100 電纜的導線電阻,將A/D 采樣端與電流源的正極輸出端接在一起,這種接法由于沒有考慮測溫電纜的電阻,因此只能適用于測溫距離較近的場合。

b.三線制接法:如圖4(b)所示,這種接法增加了用于A/D 采樣的補償線,三線制接法消除了連接導線電阻引起的測量誤差,這種接法適用于中等測溫距離的場合。

c.四線制接法:如圖4?所示,這種接法不僅增加了A/D 采樣補償線,還加了一條A/D對地的補償線,這樣可以近一步的減小測量誤差,可以用于測溫距離較遠的場合。如果只從精度上考慮,采用四線制接法效果最好。

?

?

?

三、下載與調試

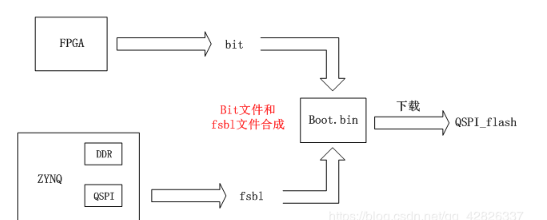

調試完成后,接下來就是將程序固化到板子中,我大致介紹一下程序固化方法和啟動流程。

?

3.1 程序的固化方法

一般在調試程序的過程中FPGA用的是JTAG模式,不需要片外配置芯片,是直接將我們編寫的程序下載到FPGA的片內RAM中,掉電不保留數據。而固化的目的是使板卡掉電不丟失程序,通常在調試階段需要多次啟動,每次上電都重新下載程序是一件很麻煩的事情,所以將程序固化進去會方便很多,下面是固化程序的參考流程。

?

https://blog.csdn.net/wmyan/article/details/79292778

?

如果大家覺得步驟很復雜的話,我用框圖的形式總結了一下,可能會清楚點。

?

?

?

3.2 程序的啟動流程

ZYNQ7000 SOC芯片可以從FLASH啟動,也可以從SD卡里啟動。ZYNQ7000 SOC芯片上電后,先運行的是ARM系統(PS端)。然后通過ARM系統軟件部分加載FPGA的比特流文件.bit至FPGA(PL端),啟動FPGA邏輯功能。

BOOT ROM:開發板上電,Z7000會先執行片內BOOT ROM 代碼,BOOT ROM代碼讀取BOOT mode寄存器決定哪一種啟動方式(SD card/QSPI flash/JTAG)。

確定好啟動方式后,BOOT ROM從相應的啟動設備中(SD card/QSPI flash)加載到First Stage Bootloader (FSBL)到On Chip Memory(OCM)RAM,并將執行權交給FSBL。

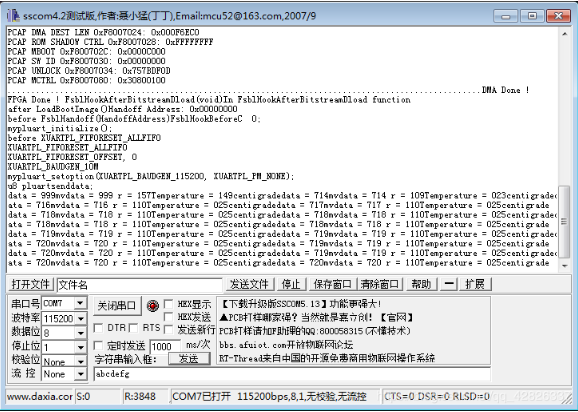

3.3 程序的測試

通過UART串口輸出,借助串口調試助手可以看到實時的溫度數值,完成測試。

?

?

?

四、總結

大致歸納一下XADC用到的基本知識(僅針對個人的學習筆記總結)。

?

1、輪詢模式:CPU重復檢查設備的狀態寄存器,直到寄存器的值表明I/O操作已經完成。

2、多路復用器mux:能夠接收多個信號,按每個信號可恢復方式合成單個輸出信號。

3、XADC也需要參考電壓,參考電壓由芯片內部或外部決定。

4、VP/VN在多路復用通道外(XADC有17個通道),即PL引腳復用。

5、XADC模塊的引腳封裝均在BANK0中。

6、用VP/VN能夠有效減小干擾,噪聲相減則抵消。

7、VP-VN的電壓輸出范圍是-0.5V ~ +0.5V,VP與VN相對于GNDADC電壓必須大于0。

8、模擬信號通道在管腳配置時不需要加電壓,數字信號通道在管腳配置時需要加電壓,電壓相當于一個標準(FPGA有1.8V 2.5V 3.3V),例如3.3V控制時,達到3.3V就相當于邏輯1,0V就相當于邏輯0。

9、掩碼:是一串二進制代碼對目標字段進行位與運算,屏蔽當前的輸入位。

10、狀態寄存器只能查看工作狀態(read only),控制寄存器可以配置(read and write)。

11、沒有JTAG一般用Anolog-Input Mode(4Ch and 4Dh)配置。

?

通過實現利用XADC對溫度的采集,我學習到了如何配置寄存器(直接用地址寫寄存器的方式),學習到了什么是固化程序以及如何將程序固化到FPGA板卡中,這同時用到了vivado和sdk編譯環境,理解了溫度傳感器的工作原理,最重要的是能夠系統地對一項工程進行梳理,這對于學習FPGA有很大的幫助,希望以后能夠通過學習和寫博客的這種方式慢慢進步。

?

電子發燒友App

電子發燒友App

評論