關鍵詞: FPGA , 國產 , 國產FPGA , 試用

作者:特權同學

2011-5-25 11:44:13 上傳

題記:本以為這個國產FPGA的就此夭折,沒想到權衡之后,在性能打些折扣的情況下還是重新撿起來了。從剛接觸這個器件的時候特權同學就很關心它的硬核可擴展性,Avalone接口用上手了,當然很希望這個51硬核也能夠提供類似的強大擴展接口。不過話說回來,畢竟是個8位的核,再強大也不到哪去,但在花了點心思琢磨了這個小玩意的擴展方式后,多少覺得還是有點花頭的。

SFR,即特殊功能寄存器。SFR是8051單片機內部用于訪問控制各種片上集成外設的主要寄存器,如常見的IO口(P0/P1/P2/P3)讀寫、IO 中斷配置、定時器配置、串口外設等。因此,對一般用戶而言,玩轉8051就是玩轉SFR的過程。一般的單芯片8051單片機的SFR接口不對外開放,除了部分寄存器內部使用外,余下地址空間保留。而Astro器件的這顆8051硬核將空置的SFR地址空間開放給用戶,提供了專門的對外接口時序。

特權同學將關于Astro器件SFR相關的特性整理如下:

● 可尋址空間0x80~0xff。

● 部分地址空間已被8051內部使用。

● 16個地址空間(能被8整除的地址如0x80、0x88、0x90、…0xf8等)可位尋址。

● 最多支持49個8051核外可用SFRs,除核內已占用的地址,余下地址空間均為用戶可用的核外SFRs。

● 外部SFR接口含有等待狀態寄存器(主要由sfack信號控制實現),允許8051內核與較慢的外設連接。

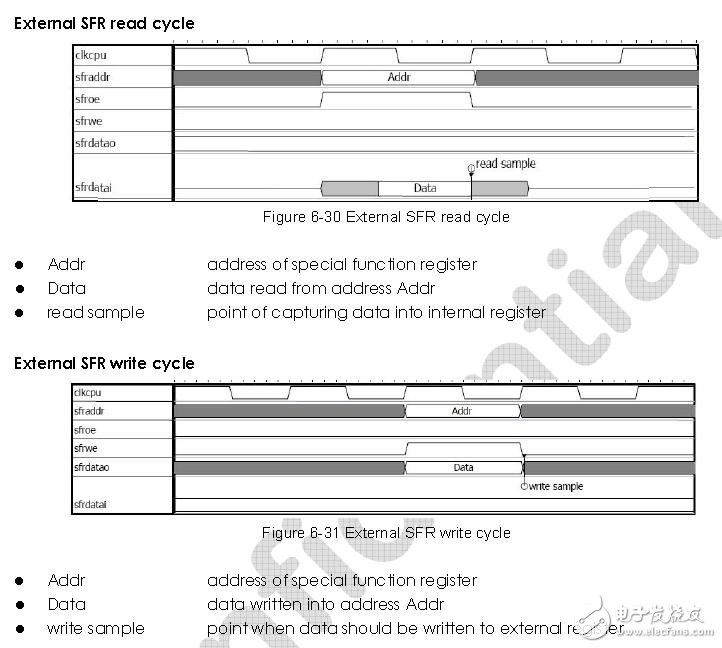

● 外部SFR讀寫時序如圖1所示。

圖1

為了簡單的評估8051硬核的SFR擴展功能的性能,特權同學做了一些測試。

測試1:SFR可用性測試

簡單的用邏輯模擬一個SFR可訪問的外部寄存器,該寄存器只使用低四位,對應控制4個外部LED的亮暗。以此驗證核外SFR的可用性。

對于8051硬核而言,如果開啟核外SFR功能,提供了如下接口(與前面給出的波形圖對應):

// External Special Function Registers interface

output[7:0] sfrdatao; //8051寫數據

output [6:0] sfraddr; //8051訪問地址

input [7:0] sfrdatai; //8051讀數據

output sfrwe; //8051寫SFR使能信號,高電平有效

output sfroe; //8051讀SFR使能信號,高電平有效

SFR從機的邏輯接口代碼如下:

reg[3:0] ledr; //LED指示燈對應的SFR

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) ledr <= 4'h0;

else if(sfrwe && (sfraddr == 7'h78)) ledr <= sfrdatao[3:0];

//8051往地址為0xf8的SFR寫數據,將數據鎖存到ledr寄存器中

end

assign {led3,led2,led1,led0} = ledr;

軟件編程時,需要在工程中做一個新的sfr定義:

//自定義SFR

sfr LED = 0xf8; //低4bit控制LED亮暗

編寫函數實現SFR控制的流水燈:

void main(void)

{

while(1)

{

LED = 0x1;

delay(500);

LED = 0x2;

delay(500);

LED = 0x4;

delay(500);

LED = 0x8;

delay(500);

}

}

實驗結果證明功能可行,達到預期。這個SFR功能的使用還是蠻簡單的。

為了驗證寫功能,基本思路是想針對板載4個按鍵做一個SFR寄存器,專供8051內核讀取當前按鍵值,然后把該值分別賦給4個LED(在前面測試的基礎上執行)。添加的邏輯代碼:

reg[3:0] keyr;

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyr <= 4'hz;

else if(sfroe && (sfraddr == 7'h79)) keyr <= {key4,key3,key2,key1}; //8051從地址為0xf9的SFR讀出數據

else keyr <= 4'hz;

end

assign sfrdatai = keyr;

讀時序這個時鐘clkcpu應該是8051工作的指令時鐘,即8051外部輸入時鐘的12分頻。這個時序圖好像不太準確,實際讀或寫選通高脈沖不會保持一整個指令周期。特權同學測試下來發現用50MHz時鐘做從接口,早一個時鐘或是晚一個時鐘周期送數據都無法使8051讀走數據,只有上面給出的代碼下時鐘送數據才能正常保證8051鎖存數據。也就是說,數據必須在讀選通期間都保持穩定,早一個時鐘周期撤銷或是晚一個時鐘周期撤銷都不行。因此,為了延長數據有效長度,改進如下:

reg[3:0] keyr;

reg keyrden;

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyrden <= 1'b0;

else if(sfroe && (sfraddr == 7'h79)) keyrden <= 1'b1;

else keyrden <= 1'b0;

end

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) keyr <= 4'hz;

else if(keyrden || (sfroe && (sfraddr == 7'h79))) keyr <= {key4,key3,key2,key1}; //8051從地址為0xf9的SFR讀出數據

else keyr <= 4'hz;

end

assign sfrdatai = keyr;

軟件編程也很簡單:

//自定義SFR

sfr LED = 0xf8; //低4bit控制LED亮暗

sfr KEY = 0xf9; //低4bit對應當前按鍵值

void main(void)

{

while(1)

{

LED = KEY;

}

}

測試2:SFR性能測試

與《國產FPGA試用手記二(51硬核性能測試)》做了類似的測試,驗證LED寄存器拉高拉低的速度,和之前的結果一樣。也就是說,核外的SFR在不使用等待功能的情況下與核內SFR的操作速度是一樣的。

測試3:SFR等待功能驗證

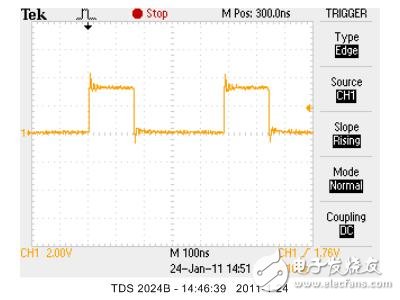

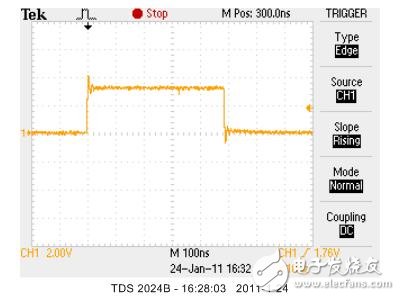

在50MHz的clkcpu下,沒有等待時(即assign sfrack = 1'b1;),不斷的對核外SFR寫使能情況可以得到如圖2所示的使能信號波形。兩次上升沿之間240ns即一個指令周期(12個50MHz時鐘周期),而讀使能信號有效高脈沖為160ns,即8個時鐘周期。

2011-5-25 11:44:13 上傳

下載附件 (16.42 KB)圖2

Datasheet中標明的sfrack信號其實無法直接從例化的51硬核中找到接口,于是特權同學干脆直接生成的IP核例化文件中把它手動引出來了,在自定義邏輯中對這個信號做了一些測試,也發現了該信號的使用方法。

代碼如下:

reg[7:0] sfcnt; //延時等待計數器,以50MHz為時鐘單位計數

wire sfrack; //SFR 讀寫等待信號

always @(posedge clk_50m or negedge rst_n) begin

if(!rst_n) sfcnt <= 8'd0;

else if(sfrwe) sfcnt <= sfcnt+1'b1;

else sfcnt <= 8'd0;

end

assign sfrack = (sfcnt == 0) | (sfcnt > 8'd23);

//等待n個指令周期,則sftcnt要大于(n*12-1)

該代碼實現在sfrwe即SFR寄存器寫選通信號到來后,用計數器sfcnt進行計數,然后相應的對需要延時等待的8051指令周期數通過控制sfrack為低電平實現。

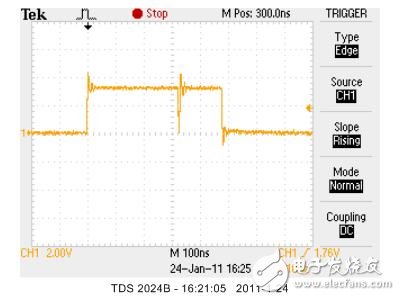

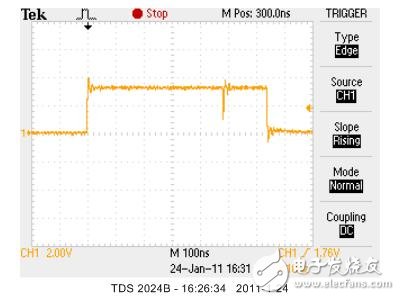

分別設置了sfcnt>8’d16、sfcnt>8’d24、sfcnt>8’d23得到sfrwe的波形如圖3、圖4、圖5所示。

2011-5-25 11:44:14 上傳

下載附件 (16.41 KB)圖3

2011-5-25 11:44:15 上傳

下載附件 (16.47 KB)圖4

2011-5-25 11:46:24 上傳

下載附件 (16.28 KB)圖5

由此可見,這里延時等待的時間必須剛好是指令周期。即系統指令周期為20ns*12=240ns,那么我們外部計數周期也是20ns的情況下,一般取等待時鐘數為12的倍數即可。否則就會出現圖3和圖4的“毛刺”,其中原因特權同學不好妄下定論,恐怕和器件本身的內部處理機制有關。

電子發燒友App

電子發燒友App

評論