在傳統的硬件電路設計中,主要的設計文件是電路原理圖,而采用HDL設計系統硬件電路時主要使用HDL編寫源程序。

VHDL的主要優點有:

(1)VHDL支持自頂至下的和基于庫的設計方法,而且支持同步電路、異步電路、現場可編程門陣列器件FPGA(field programmable gate array)以及其他隨機電路的設計。

(2)VHDL語句的行為描述能力和程序結構決定了它具有支持大規模設計的分解和已有設計再利用的功能,它支持系統的數學模型直到門級電路的描述,并且高層次的行為描述與低層次的門級電路描述、結構描述可以混合使用。(3)VHDL的硬件描述與具體的工藝技術和硬件結構無關,當門級或門級以上的描述通過仿真檢驗后,再利用相應的工具將設計映射成不同的工藝,因此電路的設計與工藝的改變是相互獨立的。彼此的改變不會產生不良影響,并且VHDL硬件描述語言的實現目標器件的選擇范圍廣泛,可使用各系列的CPLD、FPGA及各種門陣列器件。

(4)VHDL具有類屬描述語句和子程序調用等功能,對于己完成的設計源程序,可以通過修改類屬參數表和函數的辦法來改變設計的規模和結構。VHDL具有豐富的仿真語句和庫函數,使得門電路級的功能仿真、檢查成為可能,使設計者對整個工程設計的結構和功能的可行性做出決策。

(5)VHDL作為一種IEEE的工業標準,使VHDL的設計成果便于重復利用和交流。這就更進一步推動了VHDL語言的推廣及完善。另外,由于其語法嚴格,給閱讀和使用帶來極大的便利。

硬件設計

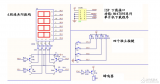

軟件設計

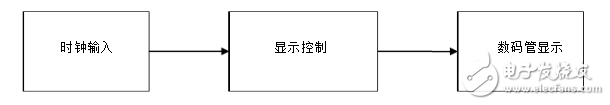

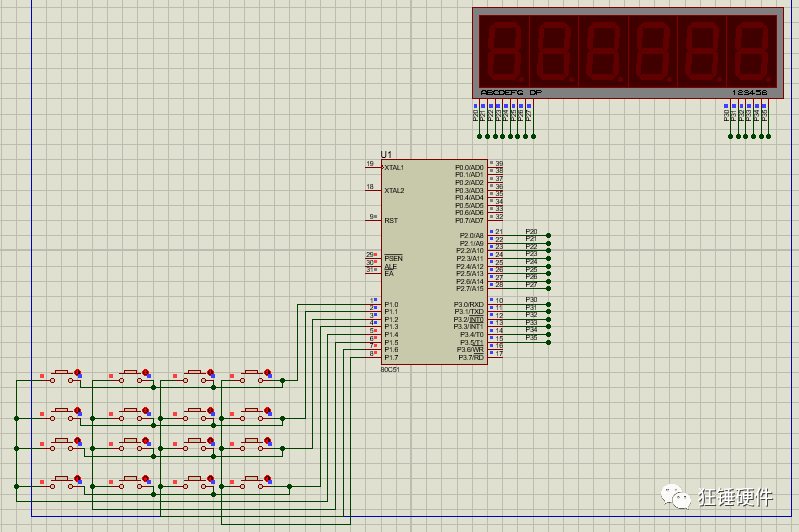

本設計的VHDL程序主要有共有3個部分:分頻、數碼管掃描進程、顯示控制進程。方案原理圖如下。

完整程序:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY key IS

PORT(clk : IN STD_LOGIC;

key : in std_logic_vector(7 downto 0);

l : out STD_LOGIC_VECTOR(2 downto 0);

data_o : out STD_LOGIC_VECTOR(7 downto 0);

bell : out STD_LOGIC:=‘0’

);

END key;

ARCHITECTURE an OF key IS

signal clk_1k : std_logic;

signal p : integer range 0 to 7;

begin

process(clk)

variable cnt1 : integer range 0 to 200;

variable cnt2 : integer range 0 to 125;

begin

if clk‘event and clk=’1‘ then

if cnt1=200 then

cnt1:=0;

if cnt2=125 then

cnt2:=0;

clk_1k《=not clk_1k;

else

cnt2:=cnt2+1;

end if;

else

cnt1:=cnt1+1;

end if;

end if;

end process;

process(p,clk_1k)

begin

if clk_1k=’1‘ and clk_1k’event then

if p=7 then

p《=0;

else

p《=p+1;

end if;

end if;

case p is

when 0 =》 l《=“000”;

when 1 =》 l《=“001”;

when 2 =》 l《=“010”;

when 3 =》 l《=“011”;

when 4 =》 l《=“100”;

when 5 =》 l《=“101”;

when 6 =》 l《=“110”;

when 7 =》 l《=“111”;

when others=》

end case;

end process;

process(clk_1k)

FUNCTION b_to_s7(bcd8421:INTEGER RANGE 0 TO 9) RETURN STD_LOGIC_VECTOR IS

VARIABLE smg7: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

CASE bcd8421 IS

WHEN 0 =》 smg7:=“11111100”;

WHEN 1 =》 smg7:=“01100000”;

WHEN 2 =》 smg7:=“11011010”;

WHEN 3 =》 smg7:=“11110010”;

WHEN 4 =》 smg7:=“01100110”;

WHEN 5 =》 smg7:=“10110110”;

WHEN 6 =》 smg7:=“10111110”;

WHEN 7 =》 smg7:=“11100000”;

WHEN 8 =》 smg7:=“11111110”;

WHEN 9 =》 smg7:=“11110110”;

END CASE;

RETURN smg7;

END b_to_s7;

begin

if clk_1k=‘1’ then

case key is

when “11111111”=》bell《=‘0’;

when “11111110”=》 data_o《=b_to_s7(1);bell《=‘1’;

when “11111101”=》data_o《=b_to_s7(2);bell《=‘1’;

when “11111011”=》data_o《=b_to_s7(3);bell《=‘1’;

when “11110111”=》data_o《=b_to_s7(4);bell《=‘1’;

when “11101111”=》data_o《=b_to_s7(5);bell《=‘1’;

when “11011111”=》data_o《=b_to_s7(6);bell《=‘1’;

when “10111111”=》data_o《=b_to_s7(7);bell《=‘1’;

when “01111111”=》data_o《=b_to_s7(8);bell《=‘1’;

when others=》data_o《=“10001111”;bell《=‘1’;

end case;

end if;

end process;

end an;

所編寫程序經過下載到電路板后,當分別撥動開關sw0—sw7時,在LED數碼管上分別顯示數字1—8,并且蜂鳴器發出聲響,有關部分運行結果的如下圖所示。

電子發燒友App

電子發燒友App

評論