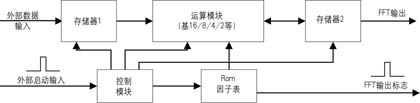

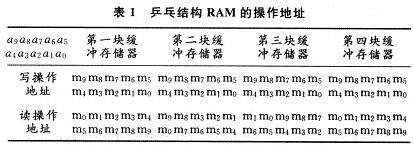

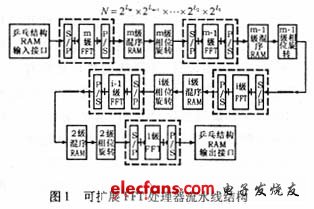

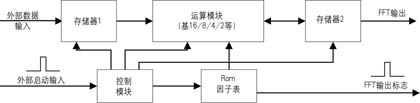

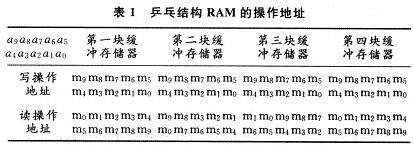

FPGA實現(xiàn)的 FFT 處理器的硬件結構。接收單元采用乒乓RAM 結構, 擴大了數(shù)據(jù)吞吐量。中間數(shù)據(jù)緩存單元采用雙口RAM , 減少了訪問RAM 的時鐘消耗。計算單元采用基 2 算法, 流水線結構, 可在

2017-11-21 15:55:13

在信號處理中,FFT占有很重要的位置,其運算時間影響整個系統(tǒng)的性能。傳統(tǒng)的實現(xiàn)方法速度很慢,難以滿足信號處理的實時性要求。針對這個問題,本文研究了基于FPGA芯片的FFT算法,把FFT算法對實時性

2010-05-28 13:38:38

FPGA實現(xiàn)高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

設計RISC微處理器需要遵循哪些原則?基于FPGA技術用VHDL語言實現(xiàn)的8位RISC微處理器

2021-04-13 06:11:51

本帖最后由 mr.pengyongche 于 2013-4-30 03:00 編輯

我想知道fft在dsp處理器上的實現(xiàn),,,他的表現(xiàn)是什么,,程序如何,,,波形是怎樣的,求這一題目的論文,,,感謝各位大神

2013-01-16 01:35:52

高速專用GFP處理器的FPGA實現(xiàn)采用 實現(xiàn)了非標準用戶數(shù)據(jù)接入 網絡時,進行數(shù)據(jù) 封裝和解封裝的處理器電路在處理器電路中引入了緩沖區(qū)管理器,使得電路能夠有效處理突發(fā)到達 瞬時速率較高的客戶

2012-08-11 11:51:11

減輕計算密集型 2D FFT 運算負載的 FFTC 硬件加速器,可實現(xiàn)低延遲和高精度附加了 JESD 的寬帶采樣信號處理解決方案,包含數(shù)字信號處理器 (DSP)、ADC 和 DAC 板、演示軟件、配置

2018-09-20 09:07:06

1.處理器上有64個可復用的IO口,我們需要64個IO口,因為是復用的,我么也會用到部分復用功能,所以IO口不夠用,有人提出用CPLD或FPGA擴展,這樣擴展的IO的速度與處理器的IO有區(qū)別嗎?

2023-04-23 14:10:40

)作為一種特殊的嵌入式微處理器系統(tǒng),已逐漸成為一個新興的技術方向。SOPC融合了SoC和FPGA各自的優(yōu)點,并具備軟硬件在系統(tǒng)可編程、可裁減、可擴充、可升級的功能。其核心是在FPGA上實現(xiàn)的嵌入式微處理器

2020-03-16 06:37:20

另一組FTFO的寫時序,實現(xiàn)了信號不間斷的采樣和存儲。FPGA將一組數(shù)據(jù)處理完畢后,以中斷的方式通知SEP3203,處理器以DMA方式將運算后的結果存儲到片外的SDRAM中。由于數(shù)據(jù)寫滿FIFO的時間大于

2019-04-26 07:00:06

PowerPC)。大量的邏輯單元使你可以實現(xiàn)數(shù)據(jù)處理單元,這些單元與處理器系統(tǒng)一起工作,由處理器對其進行控制或監(jiān)控。FPGA作為一種可重復編程的單元,允許你在設計過程中進行編程并對其進行測試。如果你發(fā)現(xiàn)了

2015-02-02 14:18:19

一種高速并行FFT處理器的VLSI結構設計摘要:在OFDM系統(tǒng)的實現(xiàn)中,高速FFT處理器是關鍵。在分析了基4按時域抽取快速傅立葉變換(FFT)算法特別的基礎上,研究了一種高性能的FFT處理器的硬件

2008-10-15 22:41:48

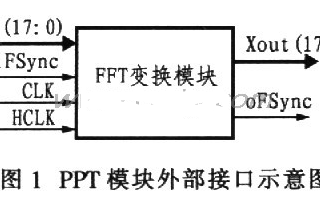

中,數(shù)字信號處理系統(tǒng)經常要進行高速、高精度的FFF運算。現(xiàn)場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數(shù)字信號處理算法的物理結構。用FPGA實現(xiàn)FFT處理器具有硬件系統(tǒng)簡單、功耗低的優(yōu)點

2019-07-03 07:56:53

代碼加速和代碼轉換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實現(xiàn)算法加速?

2021-04-13 06:39:25

的可擴展處理平臺(Extensible Processing Platform)架構,該平臺將完整的ARM Cortex-A9 MPCore處理器片上系統(tǒng)(SoC)與集成了28nm低功耗和高性能的可編程

2019-10-15 06:30:53

我目前使用的是32位FFT LIB函數(shù),它在DSP庫(XC32和C32)中可用。這個庫還會與PIC32 MZ處理器一起工作嗎?據(jù)我所知,MZ系列包含一個加速fft轉換的指令,但是當我查看

2019-08-08 10:49:05

``基于FPGA的圖像FFT濾波處理 AT7_Xilinx開發(fā)板(USB3.0+LVDS)資料共享 騰訊鏈接:https://share.weiyun.com/5GQyKKc 百度網盤鏈接

2019-08-08 11:33:01

基于FPGA的移位寄存器流水線結構FFT處理器

2012-08-18 00:04:21

基于FPGA的超高速FFT硬件實現(xiàn)介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數(shù)超高速FFT硬件系統(tǒng)設計與實現(xiàn)方法,當多組大點數(shù)進行FFT運算時,利用FPGA

2009-06-14 00:19:55

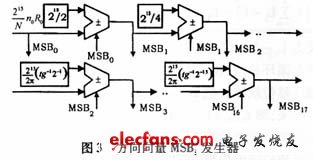

FFT算法在數(shù)字信號處理中占有重要的地位,所以本文提出了用FPGA實現(xiàn)FFT的一種設計思想,給出了總體實現(xiàn)框圖:重點設計實現(xiàn)了FFT算法中的蝶形處理單元,采用了一種高效乘法器算法設計實現(xiàn)了蝶形處理單元中的旋轉因子乘法器,從而提高了蝶形處理器的運算速度,降低了運算復雜度。

2017-11-28 11:32:15

在現(xiàn)代電子系統(tǒng)設計中,微處理器是不可缺少的一個部件。然而,隨著系統(tǒng)變得越來越復雜,擁有更廣泛的功能和用戶接口時,使用中檔微處理器的系統(tǒng)架構在連接一個或多個微處理器時面臨著三個關鍵的挑戰(zhàn)

2019-09-26 08:08:42

傅里葉變換、脈沖壓縮、線性預測編碼語音處理、高速定點矩陣乘法等,有較好的應用前景和發(fā)展空間。那有誰知道該如何利用FPGA實現(xiàn)級聯(lián)信號處理器嗎?

2019-07-30 07:22:48

FFT算法的實現(xiàn)為了提高FFT工作頻率和節(jié)省FPGA資源,采用3級流水線結構實現(xiàn)64點的FFT運算。流水線處理器的結構如圖2所示。每級均由延時單元、轉接器(SW)、蝶形運算和旋轉因子乘法4個模塊組成

2019-06-17 09:01:35

請問一下如何用FPGA實現(xiàn)FFT算法?

2021-04-08 06:06:26

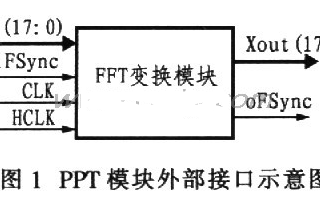

本文設計的FFT處理器,基于FPGA技術,由于采用移位寄存器流水線結構,實現(xiàn)了兩路數(shù)據(jù)的同時輸入,相比傳統(tǒng)的級聯(lián)結構,提高了蝶形運算單元的運算效率,減小了輸出延時,降低了芯片資源的使用。

2021-04-28 06:32:30

ARM通過增加硬件協(xié)處理器來支持對其指令集的通用擴展,通過未定義指令陷阱支持這些協(xié)處理器的軟件仿真。簡單的ARM核提供板級協(xié)處理器接口,因此協(xié)處理器可作為一個獨立的元件接入。高速時鐘使得板級接口非常

2022-04-24 09:36:47

本文提出的通過微處理器加FPGA結合串行菊花鏈實現(xiàn)可重構的方式,實現(xiàn)了動態(tài)可重構FPGA結構設計的一種應用。

2021-05-10 06:22:19

怎么利用FPGA和嵌入式處理器實現(xiàn)低成本智能顯示模塊?

2021-04-28 07:10:33

求大佬分享一下怎么用FPGA嵌入式處理器實現(xiàn)構想?

2021-04-13 06:31:14

快速傅里葉變換(FFT)在雷達、通信和電子對抗等領域有廣泛應用。近年來現(xiàn)場可編程門陣列(FPGA)的飛速發(fā)展,與DSP技術相比,由于其并行信號處理結構,使得FPGA能夠很好地適用于高速信號處理

2019-08-28 06:10:15

一個以上的嵌入式處理器IP(Intellectual Property,知識產權)核,具有小容量片內高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA

2020-03-13 07:03:54

討論了一種基于FPGA的64點FFT處理器的設計方案,輸入數(shù)據(jù)的實部和虛部均以16位二進制數(shù)表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發(fā)平臺對處理器各個的模塊進行設計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結果正確。

2021-04-29 06:25:54

求大神分享一種基于FPGA的級聯(lián)結構FFT處理器的優(yōu)化設計

2021-05-06 07:34:53

的 FPU 框,即可實現(xiàn)APU-FPU 連接(見圖 3 頂部)。該向導可實現(xiàn)一個經過優(yōu)化能以處理器時鐘三分之一速率運行的雙精度 FPU。您也可定制更高時鐘速率的 FPU 和單精度 FPU。如果不想

2018-08-03 11:15:23

徽標。支持低功耗應用SiFive的處理器核心設計可擴展方法使萊迪思能夠創(chuàng)建針對IP的核心應用程序,該應用程序著重于性能和功能工作負載要求。兩家公司已同意合作開發(fā)新的,優(yōu)化的處理器內核,這些內核在開放

2020-07-27 17:57:36

處理器擴展性有什么重要之處?

2021-06-17 09:51:26

FFT算法原理是什么?怎樣去實現(xiàn)64點高速FFT算法?

2021-04-29 07:03:28

怎樣去設計可擴展FFT處理器?可擴展FFT處理器的結構是如何構成的?

2021-05-06 07:52:19

賽靈思Zynq-7000可擴展處理平臺(EPP)將雙ARM Cortex-A9 MPCore處理器系統(tǒng)與可編程邏輯和硬IP外設緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

處理器。這些可配置協(xié)處理器可幫助設計人員解決傳統(tǒng)ASIC仿真中存在的許多問題,并更省力、更快捷地實現(xiàn)更精確的設計。

2019-07-23 06:24:16

,最高可提供256 GMAC的DSP性能。將需要高速并行處理的工作卸載給FPGA,而將需要高速串行處理的工作留給處理器,這樣即可在降低系統(tǒng)要求的同時優(yōu)化整體系統(tǒng)的性價比。

2019-07-15 06:18:56

包含一個以上的嵌入式處理器IP(Intellectual Property,知識產權)核,具有小容量片內高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA編程接口共用或并存,可能包含部分可編程模擬電路,單芯片、低功耗[1]。

2019-08-23 08:18:51

介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數(shù)超高速FFT硬件系統(tǒng)設計與實現(xiàn)方法,當多組大點數(shù)進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

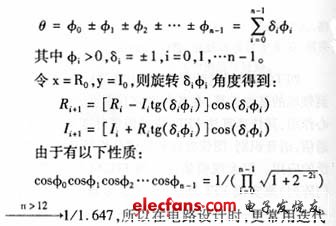

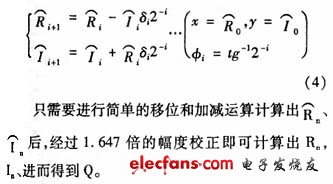

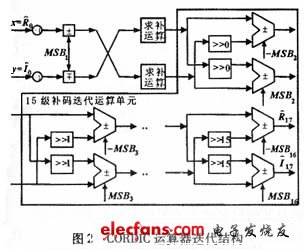

26 針對在工業(yè)中越來越多的使用到的FFT,本文設計出了一種利用CORDIC 算法在FPGA 上實現(xiàn)快速FFT 的方法。CORDIC 實現(xiàn)復數(shù)乘法比普通的計算器有結構上的優(yōu)勢,并且采用了循環(huán)結構

2009-08-24 09:31:10 9

9 本文討論了一種可在FPGA 上實現(xiàn)的FFT 結構。該結構采用基于流水線結構和快速并行乘法器的蝶形處理器。乘法器采用改進的Booth 算法,簡化了部分積符號擴展,使用Wallace 樹結構和4-2

2009-09-11 15:46:40 16

16 主要介紹基于現(xiàn)場可編程門陣列(FPGA)的微波接力通信中FFT 模塊的設計與實現(xiàn)方案。提出一種全并行流水結構,采用新一代大容量的高速Stratix 系列FPGA 可以在N 個系統(tǒng)時鐘之內

2009-11-24 12:13:19 19

19 本文主要研究基于FPGA 的數(shù)據(jù)處理系統(tǒng),內部包含一個1024 點的FFT 處理單元。FFT 部分采用基四算法,五級級聯(lián)處理,并通過CORDIC 流水線結構使硬件實現(xiàn)較慢的復乘運算轉化為移位

2009-12-19 16:18:35 59

59 本文利用頻域抽取基四算法,運用靈活的硬件描述語言-Verilog HDL 作為設計主體,設計并實現(xiàn)一套集成于FPGA 內部的FFT 處理器。FFT 處理器的硬件試驗結果表明該處理器的運算結

2010-01-20 14:33:54 40

40 在OFDM系統(tǒng)的實現(xiàn)中,高速FFT處理器是關鍵。在分析了基4按時域抽取快速傅立葉變換(FFT)算法特點的基礎上,研究了一種高性能FFT處理器的硬件結構。此結構能同時從四個并行存

2010-07-02 16:51:15 11

11 針對在工業(yè)中越來越多的使用到的FFT,本文設計出了一種利用CORDIC算法在FPGA上實現(xiàn)快速FFT的方法。CORDIC實現(xiàn)復數(shù)乘法比普通的計算器有結構上的優(yōu)勢,并且采用了循環(huán)結構的CORDIC算

2010-08-09 15:39:20 55

55 Intel Xeon?可擴展處理器(第三代)Intel?Xeon?可擴展處理器(第三代)針對云、企業(yè)、HPC、網絡、安全和IoT工作負載進行了優(yōu)化,具有8到40個強大的內核和頻率范圍、功能和功率級別

2024-02-27 11:58:54

Intel 第四代Xeon?可擴展處理器Intel第4代Xeon? 可擴展處理器設計旨在加速以下增長最快工作負載領域的性能:人工智能 (AI)、數(shù)據(jù)分析、網絡、存儲器和高性能計算 (HPC) 。這些

2024-02-27 12:19:48

用FPGA實現(xiàn)FFT算法

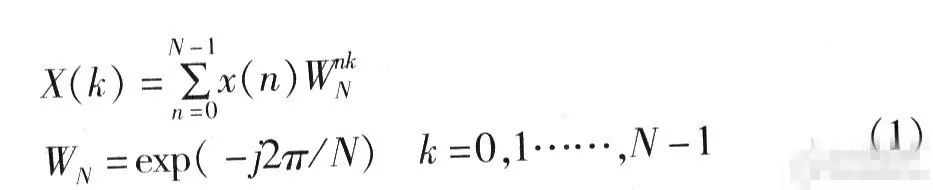

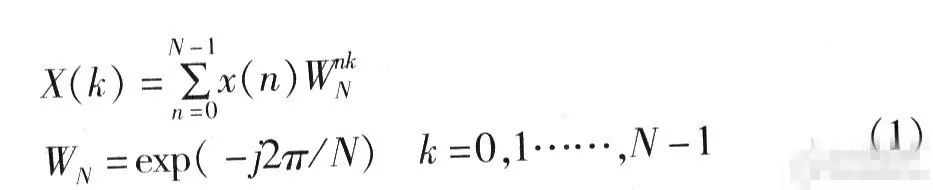

引言 DFT(Discrete Fourier Transformation)是數(shù)字信號分析與處理如圖形、語音及圖像等領域的重

2008-10-30 13:39:20 1426

1426

基于FPGA的級聯(lián)結構FFT處理器的優(yōu)化設計

0 引 言

數(shù)字信號處理主要研究采用數(shù)字序列或符號序列表示信號,并用數(shù)字計算方法對這些序列進行處理,以便

2009-12-28 11:07:33 1865

1865

基于FPGA的高速定點FFT算法的設計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學科領域(如信號處理、圖像處理、生物信息學、計算物理

2010-02-09 10:47:50 992

992

提出了一種高速定點FFT 處理器的設計方法此方法在CORDIC 算法的基礎上通過優(yōu)化操作數(shù)地址映射方法和旋轉因子生成方法每周期完成一個基4 蝶形運算具有最大的并行性同時按照本文提出

2011-06-28 18:08:12 28

28 作者提出了一種實時可重配置的FFT處理器.該處理器采用小點數(shù)內部流水和大點數(shù)二維化處理結構,通過控制各處理模塊實現(xiàn)4,16,64,256和1 024點復數(shù)FFT運算,并給出了該結構與Hasan結構的

2011-08-23 11:35:20 2370

2370 在現(xiàn)代邏輯設計中,FPGA占有重要的地位,不僅因為具有強大的邏輯功能和高速的處理速度,同時因為其內部嵌有大量的可配置的塊RAM,使其得到了廣泛地應用,例如FFT算法的實現(xiàn)等。

2011-09-27 17:07:12 54

54 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實時性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運算速度快的特點以及FFT算法的分級特性,實現(xiàn)了高速、高階FFT的流水線工作方式設計。通

2011-10-01 01:52:51 55

55 為了提高快速傅里葉變換( FFT)處理數(shù)據(jù)的實時性,本文利用現(xiàn)場可編程陣列( FPGA)邏輯資源豐富、運算速度快的特點以及FFT算法的分級特性,實現(xiàn)了高速、高階FFT的流水線工作方式設計。通

2011-10-28 17:11:26 32

32 提出了Radix-4 FFT的優(yōu)化算法,采用該優(yōu)化算法設計了64 點流水線IFFT/FFT 處理器,該處理器可以在64 個時鐘周期內僅采用3 個復數(shù)乘法器獲得64 點處理結果,提高了運算速度,節(jié)約了硬件資

2011-12-14 16:03:35 47

47 首先,針對圖像聲納實時性的要求和FPGA片內資源的限制,設計了級聯(lián)和并行遞歸兩種結構的FFT處理器。文中詳細討論了利用流水線技術和并行處理技術提高FFT處理器運算速度的方法,并

2011-12-27 13:51:14 51

51 本書比較全面地闡述了fpga在數(shù)字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現(xiàn)數(shù)字信號處理的數(shù)據(jù)規(guī)劃、多種

2015-12-23 11:07:46 44

44 本文主要研究如何利用FPGA實現(xiàn)FFl’算法,研制具有自主知識產權的FFT

信號處理器

2016-03-21 16:22:52 40

40 高速專用GFP處理器的FPGA實現(xiàn),下來看看

2016-05-10 11:24:33 15

15 利用FPGA的IP核設計和實現(xiàn)FFT算法

2016-05-24 14:14:47 36

36 基于802_11ac的FFT_IFFT處理器設計_施隆照

2017-01-03 17:41:32 0

0 基于FPGA的1024點高性能FFT處理器的設計_鐘冠文

2017-03-19 11:36:55 10

10 算法及其實現(xiàn)方法的研究具有很強的理論和現(xiàn)實意義。 1 FFT 算法及其實現(xiàn)方法 現(xiàn)場可編程門陣列 FPGA 是一種可編程使用的信號處理器件,其運算速度高,內置高速乘法器可實現(xiàn)復雜累加乘法運算;同時其存儲量大,無需外接存儲器就可實現(xiàn)大量數(shù)

2017-10-15 10:54:31 20

20 有兩種:軟件(軟件編程)和硬件(專用ASIC芯片)。DSP軟件編程實現(xiàn)速度較慢,不能滿足FFT算法高速、實時的場合;專用芯片在速度上能滿足要求,但外圍電路復雜,可擴展性差,FPGA在當今數(shù)字信號處理領域被廣泛采用,其兼有軟件編程的靈活性和專用芯

2017-11-09 10:58:14 11

11 運算所需的巨量存儲器,需外置特定的接口、控制芯片和RAM.限制了運算速度。采用專用的FFT處理芯片,雖然速度能達到要求,但其外圍電路復雜、可擴展性差,并且價格昂貴。FPGA具有可配置性強、速度快、密度高、功耗低的特點,而且目前的FPGA內部集成有

2018-04-03 16:48:12 2

2 、遙感遙測、地質勘探、航空航天、生物醫(yī)學等眾多領域都獲得極其廣泛的應用。隨著FPGA技術的高速發(fā)展以及EDA技術的成熟,采用FPGA芯片實現(xiàn)FFT已經顯示出巨大的潛力。

2019-01-15 10:20:00 2757

2757

本文提出了一種實現(xiàn)信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統(tǒng)的系統(tǒng)設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯(lián)設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現(xiàn)了信號的采集與存儲。

2018-11-02 15:46:01 10

10 對實現(xiàn)FFT的工程,目前通用的方法是采用DSP、FFT處理電路及FPGA。用DSP實現(xiàn)FFT的處理速度較慢,不能滿足某些高速信號實時處理的要求;專用的FFT處理器件雖然速度較快,但是價格相對昂貴

2020-07-27 17:52:01 1191

1191

針對高速實時信號處理的要求,介紹了用現(xiàn)場可編程邏輯陣列(FPGA)實現(xiàn)的一種流水線結構的FFT處理器方案。該FFT處理器能夠對信號進行實時頻譜分析,最高工作頻率達到75 MHz。通過對采樣數(shù)據(jù)進行

2021-01-25 14:51:00 12

12 采用FPGA實現(xiàn)了非標準用戶數(shù)據(jù)接入sDH網絡時,進行數(shù)據(jù)GFP封裝和解封裝的處理器電路。在處理器電路中引入了緩沖區(qū)管理器,使得電路能夠有效處理突發(fā)到達、瞬時速率較高的客戶數(shù)據(jù);采用了并行cRc算法

2021-01-27 16:38:03 7

7 采用FPGA實現(xiàn)了非標準用戶數(shù)據(jù)接入sDH網絡時,進行數(shù)據(jù)GFP封裝和解封裝的處理器電路。在處理器電路中引入了緩沖區(qū)管理器,使得電路能夠有效處理突發(fā)到達、瞬時速率較高的客戶數(shù)據(jù);采用了并行cRc算法

2021-01-28 17:22:52 7

7 的數(shù)字信號處理系統(tǒng)具有更高的實時性和可嵌入性,能夠方便地實現(xiàn)系統(tǒng)的集成與功能擴展。FFT的硬件結構主要包括蝶形處理器、存儲單元、地址生成單元與控制單元。

2021-02-01 10:33:06 19

19 目的針對高速數(shù)字信號處理的要求,給出了用現(xiàn)場可編程門陣列(FPGA)實現(xiàn)的快速傅里葉變換(FFT)方案。方法 算法為按時間抽取的基4算法,采用遞歸結構的塊浮點運算方案,蝶算過程只擴展兩個符號位以適應

2021-02-02 17:13:02 13

13 及布局布線,并用ModelSim和Matlab對設計作了聯(lián)合仿真。結果表明,通過利用FPGA器件中大量的乘法器、邏輯單元及存儲器等硬件資源,采用全并行加流水結構,可在一個時鐘節(jié)拍內完成32點FFT運算的功能,設計最高運算速度可達11 ns,可實現(xiàn)對高速A/D采樣數(shù)據(jù)的實時處理.

2021-03-31 15:22:00 11

11 該文在闡述了灰度圖像順序形態(tài)變換的基礎上,介紹了順序形態(tài)變換硬件實現(xiàn)的圖像處理系統(tǒng).該系統(tǒng)采用DSP+FPGA的框架結構,利用FPGA的可重構特性將其中一片FPGA作為協(xié)處理器可以實現(xiàn)不同的圖像處理

2021-04-01 11:21:46 8

8 EE-263:在TigerSHARC?處理器上并行實現(xiàn)定點FFT

2021-05-16 08:53:56 2

2 基于新型FPGA的FFT設計與實現(xiàn)設計方法。

2021-06-17 17:07:03 42

42 基于FPGA+STM32雙處理器的高速數(shù)據(jù)采集系統(tǒng)

2021-06-25 10:38:04 64

64 摘要:在對FFT(快速傅立葉變換)算法進行研究的基礎上,描述了用FPGA實現(xiàn)FFT的方法,并對其中的整體結構、蝶形單元及性能等進行了分析。

2022-04-12 19:28:25 4515

4515 摘要: 現(xiàn)代 信號 處理系統(tǒng)通常需要在不同處理器之間實現(xiàn)高速數(shù)據(jù) 通信 ,SRIO協(xié)議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現(xiàn)SRIO協(xié)議的方法

2023-03-20 15:00:01 1324

1324 目前,硬件實現(xiàn)FFT算法的方案主要有:通用數(shù)字信號處理器(DSP)、FFT專用器件和現(xiàn)場可編程門陣列(FPGA)。DSP具有純軟件實現(xiàn)的靈活性,適用于流程復雜的算法,如通信系統(tǒng)中信道的編譯

2023-05-11 15:31:41 1649

1649

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評論