作者:Tom Myers 高級(jí)硬件工程師,Anritsu 公司 tom.myers@anritsu.com

低功耗的賽靈思 FPGA 系列使總線供電的 USB 器件設(shè)計(jì)垂手可得

憑借在市場中數(shù)十億的端口數(shù)量,通用串行總線 (USB) 成為實(shí)現(xiàn)主機(jī)與外設(shè)之間千兆位以下連接的首選接口。不過,由于 USB 規(guī)范有著嚴(yán)格的浪涌電流和穩(wěn)態(tài)工作電流限值要求,因此由總線供電的器件應(yīng)用經(jīng)常忽視FPGA,而是更愿意采用性能和靈活性都不及 FPGA 的微控制器解決方案。

隨著賽靈思低功耗系列器件中最新成員Artix-7 的問世,這種情況將不復(fù)存在。通過嚴(yán)加注意系統(tǒng)級(jí)功率轉(zhuǎn)換效率和排序,并使用 VivadoDesign Suite 中的功耗估算和優(yōu)化工具,設(shè)計(jì)人員能夠克服這些挑戰(zhàn)性限制,從而實(shí)現(xiàn)高性能、緊密集成的并由總線供電的定制器件。

讓我們來看一下如何以 Artix-7 MicroBlaze平臺(tái)為基礎(chǔ)構(gòu)建由總線供電的 USB 2.0 高速器件。在 Anritsu 公司,我們成功利用該方案開發(fā)出一款最新的微波功率測量產(chǎn)品。該新產(chǎn)品設(shè)計(jì)采用USB 2.0 高速接口,相比前一代采用 USB 全速微控制器解決方案的產(chǎn)品而言,顯著提高了測量吞吐量。更高的測量吞吐量可縮短制造生產(chǎn)測試應(yīng)用的測試時(shí)間。最終可幫助客戶節(jié)約成本

系統(tǒng)設(shè)計(jì)

Anritsu項(xiàng)目中,我們必須要克服的主要障礙是 500 毫安(額定 5V)的穩(wěn)態(tài)電流消耗限值。因此,我們的系統(tǒng)設(shè)計(jì)方案以功耗預(yù)算為中心。我們將數(shù)據(jù)手冊(cè)上電流消耗的典型值和最大值制成功率預(yù)算電子數(shù)據(jù)表。

功率預(yù)算中的大部分是針對(duì)200MB 的最小片外存儲(chǔ)器需求。最適合此需求的是標(biāo)準(zhǔn) 4Gb LPDDR2 器件。我們利用廠商應(yīng)用指南提供的詳細(xì)方法生成該器件的電流消耗估算,并應(yīng)用估算的數(shù)據(jù)流配置文件。我們還利用Xilinx Power Estimator (XPE) 等工具,通過假設(shè)功能、時(shí)鐘速率和觸發(fā)率,對(duì)各種可編程器件及其它解決方案進(jìn)行了評(píng)估。

我們確定了幾款備選器件,并且利用MicroBlaze、存儲(chǔ)器控制器(使用存儲(chǔ)器接口生成器 (MIG))構(gòu)建出完整系統(tǒng)的子系統(tǒng),再使用 Vivado 的 IP Integrator 工具添加各種外設(shè)的接口模塊,以精確功耗、尺寸和I/O 估算值。我們快速獲得可綜合目標(biāo),并利用 Vivado 功耗報(bào)告精算功耗大小。

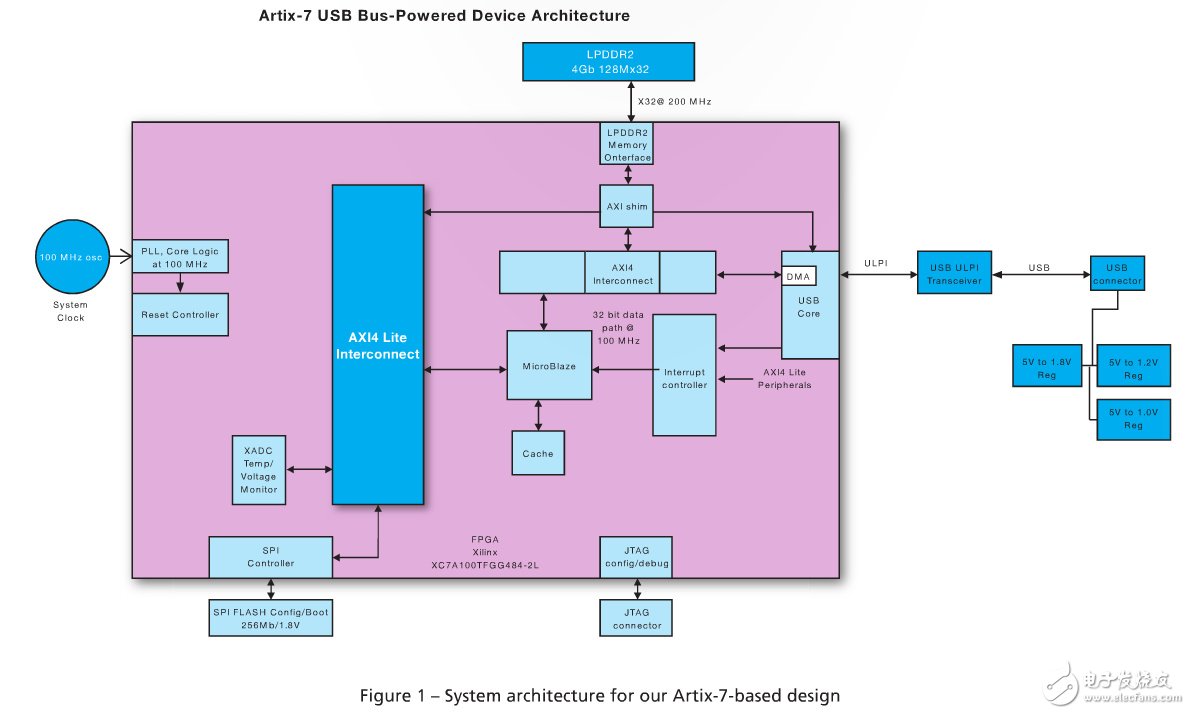

由于MIG 本身不提供到LPDDR2 器件的 AXI 本地連接,因此我們過后自己開發(fā)該鏈路。在我們的AXI層(shim) 做好之前,我們使用 MIG 生成的 LPDDR2 實(shí)例設(shè)計(jì)進(jìn)行初步的功耗估算和尺寸調(diào)整。圖1 給出了得到的系統(tǒng)架構(gòu)。

降低器件的晶片溫度能減少漏電流功耗。

策略包括盡可能減小器件晶片尺寸并選擇盡可能大的封裝

正如“Vivado DesignSuite 用戶指南:賽靈思功耗分析與優(yōu)化”(UG907) 中介紹的那樣,降低器件的晶片溫度能夠減少漏電流功耗。我們使用的策略包括根據(jù)應(yīng)用嚴(yán)格的板級(jí)空間約束,盡可能縮小器件晶片尺寸并選擇盡可能大的器件封裝。

我們通過減少電源數(shù)量來最大程度降低轉(zhuǎn)換損耗和穩(wěn)壓器電路成本。在確定器件功耗要求后,我們?cè)O(shè)計(jì)了電壓轉(zhuǎn)換電路,用以將額定的USB 5V 總線電壓降至電軌電壓。目前為止,我們一直在關(guān)注穩(wěn)態(tài)電流消耗。不過,還必須考慮到浪涌電流消耗。最小化浪涌電流的方法之一是選擇具有軟啟動(dòng)功能的穩(wěn)壓器控制上電排序。您必須將FPGA 的上電順序和斜坡時(shí)間要求與 USB 要求進(jìn)行權(quán)衡。

從容應(yīng)對(duì)意料之外的情況

盡管提供各種機(jī)制用以正確地關(guān)閉和移除USB 設(shè)備,但現(xiàn)實(shí)中很多用戶會(huì)不顧警告魯莽地拔下設(shè)備。如果固件更新過程不夠穩(wěn)健可靠,就會(huì)出現(xiàn)問題,導(dǎo)致無響應(yīng)的“磚頭”設(shè)備,客戶不悅,以及成本不菲的設(shè)備返廠以進(jìn)行固件恢復(fù)。Anritsu憑借大批量制造測試的可靠性和速度,在競爭中脫穎而出。因此,我們的主要要求包括快速啟動(dòng)時(shí)間和快速固件升級(jí)時(shí)間。

我們通過實(shí)現(xiàn)賽靈思應(yīng)用指南 XAPP1081介紹的和圖 2 中總結(jié)的 QuickBoot 黃金鏡像固件升級(jí)架構(gòu)與流程,解決了這個(gè)問題。傳統(tǒng)7 系列回讀多重啟動(dòng)解決方案采用的啟動(dòng)過程可保持已知正確的“黃金”鏡像,在配置閃存存儲(chǔ)器中包含比特流。在更新過程中,更新的“工作”鏡像在“黃金”鏡像之后載入存儲(chǔ)器。如果更新過程失敗或者“工作”鏡像損壞,F(xiàn)PGA會(huì)自動(dòng)檢測錯(cuò)誤并回讀至“黃金”鏡像。XAPP1081 Quick-Boot 方法進(jìn)一步擴(kuò)展該過程,使其具備更完善的配置時(shí)間和“黃金”鏡像更新特性。

在該項(xiàng)目成功的基礎(chǔ)之上,我們進(jìn)一步展望下一代賽靈思器件將如何為Anritsu 產(chǎn)品實(shí)現(xiàn)更多功能。例如,大量的功耗預(yù)算被片外 SDRAM 互聯(lián)占用。我們期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 來減少或消除該負(fù)載,或許可以在應(yīng)用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 產(chǎn)品線。

如需了解更多信息,敬請(qǐng)聯(lián)系:更新過程中,更新的“工作”鏡像在“黃金”鏡像之后載入存儲(chǔ)器。如果更新過程失敗或者“工作”鏡像損壞,F(xiàn)PGA會(huì)自動(dòng)檢測錯(cuò)誤并回讀至“黃金”鏡像。XAPP1081 Quick-Boot 方法進(jìn)一步擴(kuò)展該過程,使其具備更完善的配置時(shí)間和“黃金”鏡像更新特性。

在該項(xiàng)目成功的基礎(chǔ)之上,我們進(jìn)一步展望下一代賽靈思器件將如何為Anritsu 產(chǎn)品實(shí)現(xiàn)更多功能。例如,大量的功耗預(yù)算被片外 SDRAM 互聯(lián)占用。我們期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 來減少或消除該負(fù)載,或許可以在應(yīng)用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 產(chǎn)品線。

如需了解更多信息,敬請(qǐng)聯(lián)系作者:更新過程中,更新的“工作”鏡像在“黃金”鏡像之后載入存儲(chǔ)器。如果更新過程失敗或者“工作”鏡像損壞,F(xiàn)PGA會(huì)自動(dòng)檢測錯(cuò)誤并回讀至“黃金”鏡像。XAPP1081 Quick-Boot 方法進(jìn)一步擴(kuò)展該過程,使其具備更完善的配置時(shí)間和“黃金”鏡像更新特性。

在該項(xiàng)目成功的基礎(chǔ)之上,我們進(jìn)一步展望下一代賽靈思器件將如何為Anritsu 產(chǎn)品實(shí)現(xiàn)更多功能。例如,大量的功耗預(yù)算被片外 SDRAM 互聯(lián)占用。我們期望研究如何利用更新的 16nm UltraScale 系列的UltraRAM 來減少或消除該負(fù)載,或許可以在應(yīng)用中采用支持 ARM7 的 Zynq-7000 AllProgrammable SoC 產(chǎn)品線。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論