ADSP-TS201S - TigerSHARC-R Embedded Processor - Analog Devices

2022-11-04 17:22:44

ADSP-TS201SABP-050 245PCS現(xiàn)貨

2019-01-07 10:27:12

PCS.預(yù)計(jì)春節(jié)后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫(kù)存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS ADSP-TS201SABP-050 245 PCS ADSP-TS201SYBPZ050873 PCS

2018-12-21 19:48:14

端,最大系統(tǒng)時(shí)鐘是核時(shí)鐘的1/4。同時(shí)SCLK也為外部接口總線提供時(shí)鐘。ADSP一TS201內(nèi)部有一個(gè)PLL,通過設(shè)置SCLKRATE2~0引腳將SCLK倍頻到所需的核時(shí)鐘。在設(shè)計(jì)過程中,為了保證時(shí)鐘

2019-04-12 07:00:11

{:12:}{:12:}{:12:}{:12:}{:12:}報(bào)道:ADSP-TS201誰(shuí)用過

2012-09-19 14:14:35

用于多處理TigerSHARC系統(tǒng)的集群總線通信的詳細(xì)信號(hào)完整性和時(shí)序分析。該系統(tǒng)由8個(gè)ADSP-TS101S器件,一個(gè)主處理器和SDRAM組成,其集群總線運(yùn)行頻率為100MHz。包括仿真結(jié)果和物理

2019-08-30 09:24:28

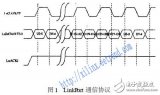

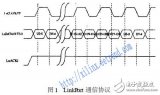

太多。而采用鏈路口通信不但能有效緩解DSP總線上的壓力,而且傳輸速度快,與FPGA之間的連線相對(duì)也少得多,故鏈路口方式更適合于FPGA與DSP之間進(jìn)行實(shí)時(shí)數(shù)據(jù)通信。1 TS101和TS201的鏈路口分析

2019-06-21 05:00:07

在使用StratixII90的FPGA與TS201進(jìn)行數(shù)據(jù)通信時(shí),FPGA向TS201發(fā)送數(shù)據(jù),link時(shí)鐘為384MHz,之前已經(jīng)做了幾十塊板卡,低溫測(cè)試通過,最近做的幾個(gè)板卡,高溫和常溫試驗(yàn)都

2014-11-04 15:18:49

在使用StratixII90的FPGA與TS201進(jìn)行數(shù)據(jù)通信時(shí),FPGA向TS201發(fā)送數(shù)據(jù),link時(shí)鐘為384MHz,之前已經(jīng)做了幾十塊板卡,低溫測(cè)試通過,最近做的幾個(gè)板卡,高溫和常溫試驗(yàn)都

2014-11-04 15:20:49

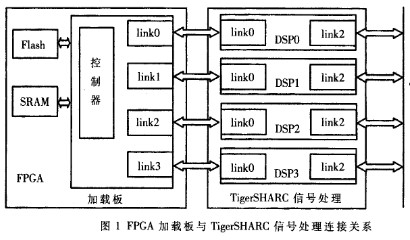

TS201與TS101的性能比較,但沒有針對(duì)兩者的鏈路口進(jìn)行詳細(xì)介紹,本文對(duì)兩者的鏈路口進(jìn)行了細(xì)致的分析和比較。文獻(xiàn)[4]所設(shè)計(jì)的采集系統(tǒng)中,DSP與FGA的通信僅限于FPGA發(fā)、TS101收的單工通信

2018-12-04 10:39:29

TS201與TS101的性能比較,但沒有針對(duì)兩者的鏈路口進(jìn)行詳細(xì)介紹,本文對(duì)兩者的鏈路口進(jìn)行了細(xì)致的分析和比較。文獻(xiàn)[4]所設(shè)計(jì)的采集系統(tǒng)中,DSP與FGA的通信僅限于FPGA發(fā)、TS101收的單工通信

2019-06-19 05:00:08

)來(lái)通知接收準(zhǔn)備好和數(shù)據(jù)塊傳輸結(jié)束。 采用FPGA與DSP通過鏈路口通信的關(guān)鍵是令雙方通信的握手信號(hào)達(dá)成協(xié)議,促使數(shù)據(jù)傳輸?shù)倪M(jìn)行。實(shí)際上,如果考慮TS201的LVDS信號(hào)形式已經(jīng)被轉(zhuǎn)換完畢,則

2019-06-21 05:00:04

TS201 link口傳輸數(shù)據(jù),一個(gè)link口為發(fā)送,一個(gè)link口為接收,link口和相關(guān)DMA配置和初始化完成后,在主函數(shù)當(dāng)中收發(fā)一直運(yùn)行,目前只發(fā)送4個(gè)unsigned int型數(shù)據(jù),link口的傳輸是按照4字傳輸,現(xiàn)在接收不到數(shù)據(jù),用示波器觀察LACKO信號(hào)一直為低電平。

2024-01-11 07:13:23

您好!我按照adi官網(wǎng)的ts201開發(fā)板的電路設(shè)計(jì)復(fù)制相關(guān)電路,選著的EPROM的啟動(dòng)模式。但是程序燒寫進(jìn)去后,斷電重啟一直無(wú)法加載程序。經(jīng)過測(cè)試發(fā)現(xiàn),正常情況下TS201的bms引腳在啟動(dòng)后一段

2024-01-11 07:02:02

TS201的核電壓1。05V,I/O電壓2.5V,DRAM電壓1.5V的上電順序應(yīng)該誰(shuí)先誰(shuí)后啊?如果兩個(gè)電壓間隔幾十ms建立可不可以?

我現(xiàn)在調(diào)整電壓上電順序,會(huì)導(dǎo)致DSP不加載程序。

2024-01-09 08:18:32

如題,我電腦已多次正確安裝并激活visual dsp++5.0程序,但是將ts201仿真器插入u***時(shí),顯示未找到驅(qū)動(dòng)程序,請(qǐng)問怎么辦

2019-01-10 14:45:39

ADI TS201的RS422串口通信 和與SDRAM讀寫的程序交流

2018-10-30 09:18:47

KIT LITE EVAL FOR ADSP-TS201S

2023-03-22 19:55:59

與Flash接口設(shè)計(jì)ADSP-TS201是ADI公司的TigerSHARC系列處理器的一種器件,其內(nèi)核工作頻率可高達(dá)600 MHz,指令周期為1.6 ns,片內(nèi)存儲(chǔ)器

2008-10-07 11:01:37

。 LTC2208IUP#PBF公司備貨2000 PCS.預(yù)計(jì)春節(jié)后3月份到貨。ADSP-TS201SAPBZ-060 在途400只+公司庫(kù)存285只=685PCS ADSP-TS201SAPBZ050 2404 PCS

2019-02-13 10:39:34

交流下ADSP TS201的RS422串口通信,EMIF的SDRAM,沒思路啊

2018-10-30 09:57:11

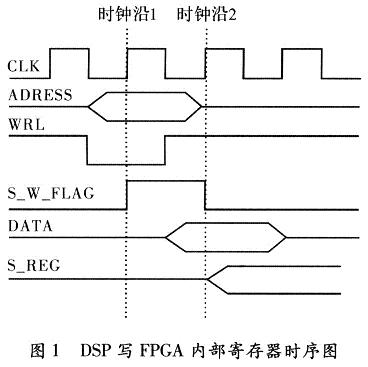

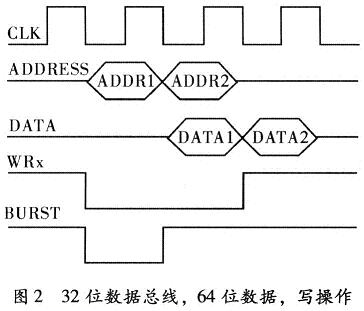

本文主要結(jié)合ADI公司的高性能ADSP-TS201的結(jié)構(gòu)特點(diǎn),討論了在系統(tǒng)設(shè)計(jì)的過程中應(yīng)該重點(diǎn)注意的幾個(gè)問題和ADSP-TS201的外部接口技術(shù),并給出了其與SDRAM,FPGA的連接實(shí)例,對(duì)基于TigerSHARC系列DSP的應(yīng)用設(shè)計(jì)具有實(shí)用的參考價(jià)值。

2021-05-27 06:59:04

總線)。因此,由多ADSP- TS201 S組成的DSP并行處理系統(tǒng)從數(shù)據(jù)傳輸方式來(lái)看,不外乎有以下三種模型:高速鏈路口(LINK)耦合模型;高速外部總線口(簇總線)耦合模型;高速鏈路口 (LINK

2019-05-21 05:00:19

基于FPGA的PCI總線接口設(shè)計(jì)

2020-03-15 11:43:10

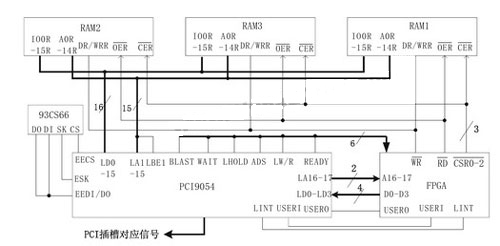

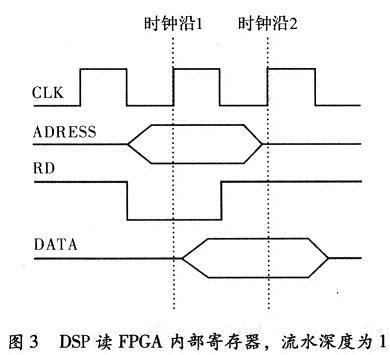

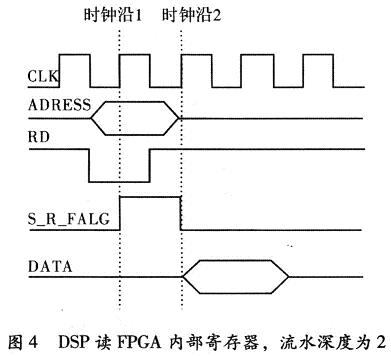

什么是DSP流水線協(xié)議?如何利用FPGA與ADSP TS201去設(shè)計(jì)總線接口?

2021-04-28 06:31:06

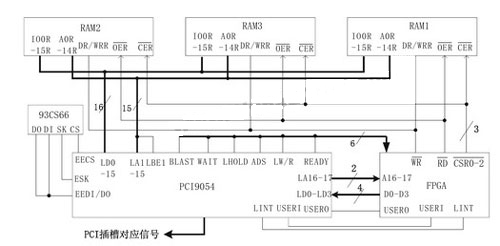

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)的應(yīng)用越來(lái)越廣泛。那么,我們?cè)撛趺蠢?b class="flag-6" style="color: red">FPGA與ADSP TS201設(shè)計(jì)總線接口呢?

2019-08-09 06:56:11

PCI總線是什么?有什么特點(diǎn)?如何利用FPGA去設(shè)計(jì)PCI總線的接口電路?設(shè)計(jì)PCI總線接口時(shí)應(yīng)注意哪些問題?

2021-05-31 06:37:24

什么是PCI總線?它有什么特點(diǎn)?如何利用FPGA設(shè)計(jì)PCI總線的接口電路?設(shè)計(jì)PCI總線接口時(shí)應(yīng)注意哪些問題?

2021-04-29 06:10:31

如題,我電腦已多次正確安裝并激活visual dsp++5.0程序,但是將ts201仿真器插入usb時(shí),顯示未找到驅(qū)動(dòng)程序,請(qǐng)問怎么辦

2024-01-12 06:00:28

您好!我按照adi官網(wǎng)的ts201開發(fā)板的電路設(shè)計(jì)復(fù)制相關(guān)電路,選著的EPROM的啟動(dòng)模式。但是程序燒寫進(jìn)去后,斷電重啟一直無(wú)法加載程序。經(jīng)過測(cè)試發(fā)現(xiàn),正常情況下TS201的bms引腳在啟動(dòng)后一段

2018-08-01 07:58:17

ADSP-TS201的鏈路口程序應(yīng)怎么寫啊,毫無(wú)頭緒啊,寄存器也看不懂,ADI公司沒找到參考的鏈路口程序啊

2018-12-10 09:17:06

你好,我用的是TS201,現(xiàn)在沒有板子,只是在仿真下,建立一個(gè)工程,驗(yàn)證某個(gè)算法。我在程序中定義了一個(gè) 數(shù)組 float zzz[36000],編譯后,它提示下面的錯(cuò)誤out of memory

2018-10-19 09:44:09

TS201的核電壓1。05V,I/O電壓2.5V,DRAM電壓1.5V的上電順序應(yīng)該誰(shuí)先誰(shuí)后啊?如果兩個(gè)電壓間隔幾十ms建立可不可以?我現(xiàn)在調(diào)整電壓上電順序,會(huì)導(dǎo)致DSP不加載程序。

2019-03-08 08:04:56

介紹了一種基于CPCI總線并采用TS201,stratix和GA3816作為系統(tǒng)信號(hào)的高速信號(hào)處理平臺(tái)。同時(shí)簡(jiǎn)單介紹了GA3816芯片的一些特點(diǎn),詳細(xì)說明了該信號(hào)處理系統(tǒng)的結(jié)構(gòu)和功能,給出了系統(tǒng)

2009-03-07 10:01:32 4

4 基于FPGA的PCI總線接口設(shè)計(jì)::PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接

2009-06-25 08:17:18 48

48 在機(jī)載SAR 的實(shí)時(shí)成像處理器中,回波信號(hào)方位向帶寬以及方位向采樣率不能很好的滿足成像處理的要求,本文選擇ADSP-TS201 處理器芯片對(duì)回波信號(hào)在成像之前對(duì)其進(jìn)行方位向預(yù)處

2009-08-05 09:45:52 18

18 ADSP-TS101 是ADI 公司新一代高性能浮點(diǎn)DSP,開始應(yīng)用在高速數(shù)據(jù)采集和處理系統(tǒng)中。TS101 外部總線接口可編程,方便和各種總線外設(shè)接口。本文結(jié)合TS101 與同步FIFO、SDRAM 和FPGA 的接

2009-08-11 09:49:31 28

28 本文采用 altera 公司cyclone 系列芯片ep1c12 實(shí)現(xiàn)了與ts101/ts201 兩種芯片的鏈路口的雙工通信,并給出了具體的設(shè)計(jì)實(shí)現(xiàn)方法。其中ts101 的設(shè)計(jì)已經(jīng)成功應(yīng)用于某信號(hào)處理機(jī)中。

2009-12-03 16:32:07 18

18 為滿足復(fù)雜信號(hào)處理的實(shí)時(shí)性要求,通過對(duì)高速數(shù)字信號(hào)處理器TS201 的系統(tǒng)結(jié)構(gòu)及其軟件開發(fā)過程的研究,在TS201 EZ-KIT 板上實(shí)現(xiàn)了自適應(yīng)旁瓣對(duì)消(ASLC)處理,結(jié)果表明了TS201 數(shù)字

2010-01-07 12:01:33 24

24 本文提出了一種基于TS201的高速數(shù)據(jù)記錄儀,能將雷達(dá)模擬信號(hào)轉(zhuǎn)換成的數(shù)字信號(hào)經(jīng)過處理后實(shí)時(shí)的按FAT32文件系統(tǒng)存儲(chǔ)到固態(tài)盤中去。采用DSP+FPGA的硬件架構(gòu),FPGA作為接口處理單元,DSP

2010-07-15 16:42:10 23

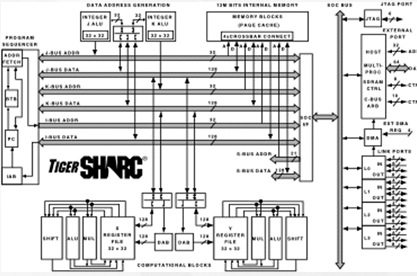

23 描述ADSP-TS201S是TigerSHARC處理器系列中的最新款器件之一。ADI公司的TigerSHARC處理器面向眾多依靠多個(gè)處理器共同工作來(lái)執(zhí)行計(jì)算密集型實(shí)時(shí)功能的信號(hào)處理應(yīng)用,非常適合

2024-01-26 11:33:09

隨著技術(shù)的發(fā)展, 往往需要在不同的系統(tǒng)之間實(shí)現(xiàn)高速通信, 現(xiàn)介紹了一種基于LVDS的高速數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">接口LinkPort , 給出了在Xilinx 的FPGA 中實(shí)現(xiàn)該接口的原理以及關(guān)鍵設(shè)計(jì), 并成功

2010-09-22 08:26:14 98

98 軍事領(lǐng)域常選擇ADI公司的TS201芯片用于信號(hào)處理平臺(tái),但由于其采用基于電路交換的LINK口進(jìn)行連接,難以實(shí)現(xiàn)軍方對(duì)電子系統(tǒng)設(shè)計(jì)提出的可重構(gòu)性的需求。FPGA可以用來(lái)實(shí)現(xiàn)接口轉(zhuǎn)換

2010-10-15 09:31:25 12

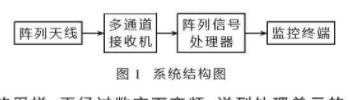

12 介紹了一種基于ADSP-TS201的無(wú)線電測(cè)向系統(tǒng)。給出了系統(tǒng)的總體結(jié)構(gòu)和工作原理,研究了MUSIC測(cè)向算法及基于零點(diǎn)預(yù)處理的波束合成算法,介紹了DSP模塊的設(shè)計(jì)思想和程序流程圖。實(shí)

2010-11-22 14:52:42 39

39 采用ADSP-TS201S芯片的圖像采集處理系統(tǒng)

隨著人們對(duì)實(shí)時(shí)信號(hào)處理要求的不斷提高和大規(guī)模集成電路的迅速發(fā)展,作為數(shù)字信號(hào)處理核心和標(biāo)志的數(shù)字

2009-03-30 12:19:18 1162

1162

摘 要 :PCI是一種高性能的局部總線規(guī)范,可實(shí)現(xiàn)各種功能標(biāo)準(zhǔn)的PCI總線卡。本文簡(jiǎn)要介紹了PCI總線的特點(diǎn)、信號(hào)與命令,提出了一種利用高速FPGA實(shí)現(xiàn)PCI總線接口的

2009-06-20 13:13:28 936

936

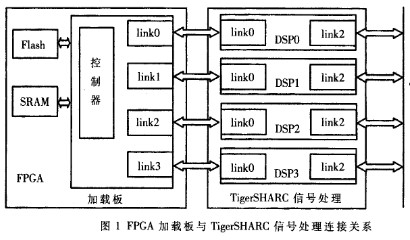

應(yīng)用領(lǐng)域: 6U VME TigerSHARC201FPGA信號(hào)處理機(jī)主要面向雷達(dá)、聲納、通信、圖象處理等高速信號(hào)處理領(lǐng)域。采用專用DSP與FPGA可編程邏輯器組成陣列化并行處理機(jī),已經(jīng)越來(lái)越成為當(dāng)前數(shù)字信號(hào)處理發(fā)展的趨勢(shì)。 雷航科技的6U VME TigerSHARC201FPGA信號(hào)處理機(jī)就

2011-02-28 12:05:32 64

64 為了解決 雷達(dá)信號(hào)處理 中的高速運(yùn)算, 大容量存儲(chǔ)和高速數(shù)據(jù)傳輸?shù)膯栴}, 提出采用 TS201 芯片實(shí)現(xiàn)雷達(dá)信號(hào)處理機(jī)設(shè)計(jì), 利用其超高性能的處理能力和易于構(gòu)造多處理并行系統(tǒng)的特

2011-07-20 17:20:13 65

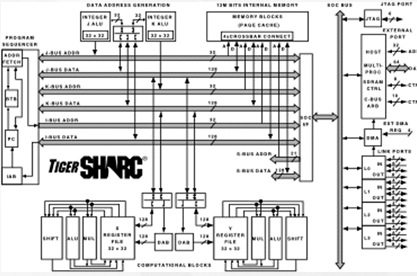

65 數(shù)字信號(hào)處理器DSP是一種具有特殊結(jié)構(gòu)的微處理器,它專門為實(shí)現(xiàn)數(shù)字信號(hào)處理的各種算法而設(shè)計(jì),因而在硬件結(jié)構(gòu)上具有特殊性。TS201是ADI公司TigerSHARC系列中集成了定點(diǎn)和浮點(diǎn)計(jì)算功

2011-09-21 11:59:38 1964

1964 設(shè)計(jì)并實(shí)現(xiàn)了一種基于ADSP TS201的組網(wǎng)雷達(dá)數(shù)據(jù)融合實(shí)時(shí)處理系統(tǒng)。主要闡述了雙ADSP TS201并行處理系統(tǒng)的結(jié)構(gòu)、算法量的估計(jì)與結(jié)果分析。系統(tǒng)可滿足集中式組網(wǎng)融合和分布式組網(wǎng)融合

2011-10-09 10:49:40 30

30 2015-10-16 16:00:35 0

0 基于ADSP_TS201S的多DSP并行系統(tǒng)設(shè)計(jì)

2015-12-29 17:33:04 22

22 TS201的實(shí)時(shí)圖像處理系統(tǒng)鏈路口通信設(shè)計(jì)

2017-08-31 15:10:19 10

10 大規(guī)模集成電路技術(shù)的發(fā)展,作為數(shù)字信號(hào)處理的核心數(shù)字信號(hào)處理器(DSP)得到了快速的發(fā)展和應(yīng)用。ADSP-TS201DSP是美國(guó)模擬器件(ADD公司繼TSl01之后推出的一款高性能處理器。此系列DSP性價(jià)比很高,兼有FPGA和ASIC信號(hào)處理性能和指令集處理器的高

2017-10-20 15:01:32 0

0 共享與鏈路口混合耦合的多DSP并行處理系統(tǒng)方案。在設(shè)計(jì)中,利用FPGA實(shí)現(xiàn)數(shù)據(jù)傳輸和CPCI接口的邏輯控制。經(jīng)驗(yàn)證,該系統(tǒng)具有運(yùn)算能力強(qiáng)、片間通信靈活、并行處理效率高等優(yōu)點(diǎn)。 關(guān)鍵詞:多DSP并行系統(tǒng);ADSP-TS201S;FPGA;CPCI接口 0 引言 在寬帶雷達(dá)信號(hào)處理中,存在諸如回波

2017-10-31 16:41:04 0

0 。LVDS差分信號(hào)技術(shù)降低了對(duì)噪聲的關(guān)注。TS201 使用LinkPort 進(jìn)行高速通信,解決了TS201 之間的通信瓶頸問題,但無(wú)法和需要高速通信的實(shí)時(shí)系統(tǒng)之間實(shí)現(xiàn)連接。FPGA 具有接口靈活,硬件設(shè)計(jì)軟件化的功能

2018-07-18 14:32:00 2537

2537

現(xiàn)代雷達(dá)信號(hào)處理已成為雷達(dá)功能實(shí)現(xiàn)的關(guān)鍵,本文根據(jù)某型雷達(dá)信號(hào)處理機(jī)的系統(tǒng)需要,對(duì)其硬件結(jié)構(gòu)及軟件設(shè)計(jì)做了系統(tǒng)優(yōu)化。設(shè)計(jì)了1套以4片 TS201和1片FPGA為核心信號(hào)處理板,該系統(tǒng)僅用l副板卡

2017-12-11 02:21:07 1881

1881

TigerSHARC系列處理器是ADI公司推出的高性能數(shù)字信號(hào)處理器,包含ADSP TS101、ADSP TS201、ADSP TS202、ADSP TS203。TigerSHARC系列處理器

2019-04-19 08:05:00 1943

1943

TS201是ADI公司繼ADSP-TS101之后又推出的新一代高性能Tiger-SHARC處理器,它集成了更大容量的存儲(chǔ)器,性價(jià)比很高。它兼有ASIC和FPGA的信號(hào)處理性能和指令集處理器的高度可編程性與靈活性,適用于高性能、大存儲(chǔ)量的信號(hào)處理和圖像應(yīng)用。其特點(diǎn)如下:

2020-08-27 09:05:59 2258

2258

模擬器件公司(Analog Devices)推出的下一代TigerSHARC處理器ADSP-TS201,ADSP-TS-202和ADSP-TS203。它的每瓦DSP性能是最高的。

2021-01-11 12:01:00 1803

1803

MT-201:FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口

2021-03-21 09:52:10 7

7 ADSP-TS201S Iba-DataFile BGA包(09/2003)

2021-04-12 16:09:33 10

10 ADSP-TS201S EZ-KIT精簡(jiǎn)版?超級(jí)政府/超級(jí)政府手冊(cè)

2021-04-13 10:25:37 0

0 ADSP-TS201 EZ-KIT Lite電路板設(shè)計(jì)數(shù)據(jù)庫(kù)

2021-04-13 12:13:17 1

1 EE-201:ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-04-13 18:00:50 6

6 EE-198:ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-04-13 18:10:30 8

8 ADSP-TS201S:TigerSHARC嵌入式處理器過時(shí)數(shù)據(jù)表

2021-04-15 18:45:56 6

6 EE-205:將代碼從ADSP-TS101S TigerSHARC?處理器移植到ADSP-TS201S TigerSHARC處理器的注意事項(xiàng)

2021-04-16 13:54:51 9

9 EE-283:采用ADSP-TS20x TigerSHARC?處理器的外部總線仲裁

2021-04-16 15:34:05 10

10 EE-170:評(píng)估ADSP-TS201S TigerSHARC?處理器的功耗

2021-04-21 10:41:30 6

6 EE-182:ADSP-TS201S TigerSHARC?處理器的散熱設(shè)計(jì)

2021-04-22 09:46:01 10

10 ADSP-TS201S EZ-KIT Lite評(píng)估系統(tǒng)手冊(cè)(3.0版,2007年1月)

2021-05-13 08:49:32 0

0 ADSP-TS201S EZ-KIT Lite評(píng)估系統(tǒng)手冊(cè)(2.0版,2005年1月)

2021-05-13 19:09:15 0

0 ADSP-TS201 TigerSHARC處理器編程參考

2021-05-18 09:21:19 1

1 ADSP-TS201 TigerSHARC處理器硬件參考

2021-05-18 15:46:19 1

1 ADSP-TS201S EZ-KIT精簡(jiǎn)版?超級(jí)政府/超級(jí)政府手冊(cè)

2021-05-24 18:47:02 0

0 EE-218:為ADSP-TS201 TigerSHARC?處理器編寫高效浮點(diǎn)FFT

2021-05-26 09:17:20 5

5 ADSP-TS201S EZ-KIT Lite為開發(fā)人員提供一種經(jīng)濟(jì)有效的方法,可以初步評(píng)估ADSP-TS201S TigerSHARC? 處理器和其多處理器能力。 該EZ-KIT Lite包括桌面

2021-06-09 08:59:50 4

4 ADSP-TS201S Iba數(shù)據(jù)文件BGA包(092003)

2021-06-16 12:02:33 2

2 ADSP-TS201S EZ-KIT Lite?手冊(cè)

2021-06-17 09:57:57 2

2 ADSP-TS201 EZ-KIT Lite電路板設(shè)計(jì)數(shù)據(jù)庫(kù)

2021-06-17 16:05:58 0

0 EE-201 ADSP-TS20x TigerSHARC?處理器片上SDRAM控制器

2021-06-18 10:47:01 4

4 EE-198 ADSP-TS201S TigerSHARC?處理器IBIS文件用戶指南

2021-06-18 11:13:33 2

2 電子發(fā)燒友網(wǎng)為你提供ADI(ti)TS201S-EZLITE相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè),更有TS201S-EZLITE的引腳圖、接線圖、封裝手冊(cè)、中文資料、英文資料,TS201S-EZLITE真值表,TS201S-EZLITE管腳等資料,希望可以幫助到廣大的電子工程師們。

2021-09-02 12:00:02

電子發(fā)燒友網(wǎng)站提供《基于ADSP-TS201的著陸雷達(dá)恒虛警電路實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-23 09:59:21 0

0 電子發(fā)燒友網(wǎng)站提供《TigerSHARC? ADSP-TS201S處理器的散熱設(shè)計(jì)要點(diǎn).pdf》資料免費(fèi)下載

2023-11-29 11:12:01 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論