項(xiàng)目概述

1.1項(xiàng)目背景

示波器(Oscilloscope)是一種能夠顯示電壓信號(hào)動(dòng)態(tài)波形的電子測(cè)量?jī)x器。它能夠?qū)r(shí)變的電壓信號(hào)轉(zhuǎn)換為時(shí)域上的曲線,原來(lái)不可見(jiàn)的電氣信號(hào),轉(zhuǎn)換為在二維平面上直觀可見(jiàn)光信號(hào),由此能夠分析電氣信號(hào)的時(shí)域性質(zhì)。

目前,全球主要的示波器生產(chǎn)廠商都集中在美國(guó),而高端示波器更是被美國(guó)Tektronix公司、Agilent公司和LeCory公司所壟斷。如Agilent公司的高性能90000系列Infiniium示波器在4個(gè)通道上均達(dá)到40-GSPS采樣率,并同時(shí)提供超低噪聲的13 GHz全實(shí)時(shí)示波器帶寬,存儲(chǔ)深度也達(dá)到了1Gpts。

而國(guó)內(nèi)方面,由于在高速模數(shù)轉(zhuǎn)換器和專(zhuān)用集成電路方面與發(fā)達(dá)國(guó)家的差距,市場(chǎng)上同類(lèi)示波器的最高采樣率、模擬帶寬和存儲(chǔ)深度等主要指標(biāo)還落后很多。本課題是開(kāi)發(fā)具有自主知識(shí)產(chǎn)權(quán)的數(shù)字熒光示波器的采集與存儲(chǔ)系統(tǒng)。為高性能采集存儲(chǔ)技術(shù)積累開(kāi)發(fā)經(jīng)驗(yàn)。同時(shí)填補(bǔ)我國(guó)數(shù)字熒光示波器的空白以及縮小與國(guó)外同類(lèi)示波器發(fā)展水平的差距。

1.2數(shù)字熒光示波器

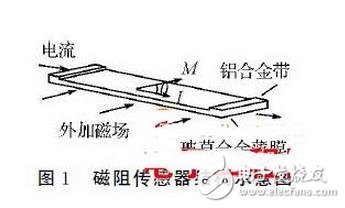

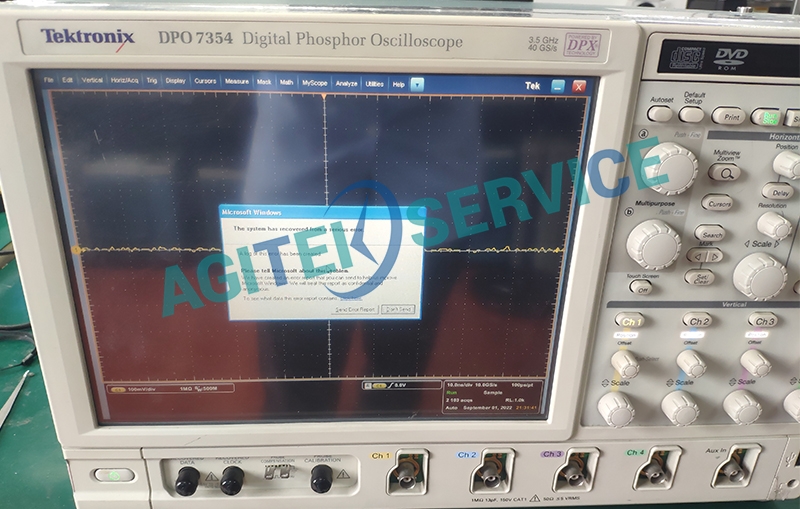

數(shù)字熒光示波器(DPO)是Tektronix公司推出的一種示波器平臺(tái),它具有數(shù)字存儲(chǔ)示波器的各種傳統(tǒng)優(yōu)點(diǎn),如數(shù)據(jù)存儲(chǔ)和先進(jìn)的觸發(fā)功能等。同時(shí),它也具有模擬實(shí)時(shí)示波器的明暗顯示和實(shí)時(shí)特性,能以數(shù)字形式產(chǎn)生顯示效果優(yōu)于模擬示波器的亮度漸次變化的熒光效果。其結(jié)構(gòu)如圖1所示。

數(shù)字存儲(chǔ)示波器因需要微處器理顯示數(shù)據(jù),導(dǎo)致在顯示兩幅波形之間有一定毫秒級(jí)的停滯時(shí)間;模擬示波器在回掃時(shí)間內(nèi)也不能捕捉波形信息。而DPO的數(shù)據(jù)采集和顯示模塊并行運(yùn)行,使得DPO能夠在處理顯示數(shù)據(jù)的同時(shí),繼續(xù)采集信號(hào)數(shù)據(jù)。同時(shí),與DSO不同的是,DPO是在連續(xù)進(jìn)行多次采集與處理后再進(jìn)行一次顯示。由于DPO一般采用專(zhuān)用硬件電路進(jìn)行采集波形的數(shù)字熒光處理,不再受限于微處理器對(duì)數(shù)據(jù)的低速處理,使得波形的更新率有了質(zhì)的提高。所以DPO能夠連續(xù)不斷得捕捉波形的絕大部分細(xì)節(jié),可以完整的反映波形信息,同時(shí)也為后續(xù)的分析處理提供了完整的數(shù)據(jù)。如圖2所示。

數(shù)字熒光顯示技術(shù)的應(yīng)用使DPO能以不同的亮度或色彩顯示信號(hào)在某一特定位置出現(xiàn)的頻率,頻率越高,則亮度越高。數(shù)字熒光處理器一般由專(zhuān)用的硬件電路(高速FPGA或ASIC)構(gòu)成。與DSO一樣,輸入信號(hào)首先經(jīng)放大和A/D變換后得到信號(hào)的采樣值,采樣值經(jīng)過(guò)數(shù)字熒光處理單元的處理后形成一幅包含波形三維信息的完整波形圖,在不中斷采集過(guò)程的情況下,數(shù)字熒光處理單元每秒向波形顯存儲(chǔ)器傳輸約30幅完整的具有熒光顯示效果的波形圖像,在微處理器的控制下,將波形圖像顯示在示波器的熒光屏上,達(dá)到模擬示波器的熒光顯示效果。與此同時(shí),微處理器可以并行方式執(zhí)行自動(dòng)測(cè)量及運(yùn)算等各種功能。

DPO每秒鐘捕獲的波形數(shù)可以高達(dá)到幾十萬(wàn)幀,比一般的DSO高幾千倍甚至上萬(wàn)倍。這種快速波形捕獲速率結(jié)合超強(qiáng)的顯示能力,使DPO具有分析信號(hào)任何細(xì)節(jié)的性能。同時(shí)由于采用了數(shù)字處理,又具備數(shù)字存儲(chǔ)示波器的優(yōu)點(diǎn)。

1.3項(xiàng)目特點(diǎn)

本項(xiàng)目的數(shù)字熒光示波器(DPO,Digital Phosphor Oscilloscope)是最新一代的示波器,它集成了數(shù)字存儲(chǔ)示波器和模擬示波器的優(yōu)點(diǎn),既有數(shù)字存儲(chǔ)示波器的波形存儲(chǔ),瞬態(tài)捕獲,負(fù)延時(shí)觸發(fā)和高級(jí)觸發(fā)等功能,又有模擬示波器的實(shí)時(shí)捕獲,高波形更新率和亮度漸次變化的顯示效果等特性。

利用FPGA豐富的邏輯資源和強(qiáng)大的數(shù)據(jù)處理能力,在FPGA模塊中實(shí)現(xiàn)主要的DPX模塊,即數(shù)字熒光處理模塊,同時(shí),利用USB接口將處理后的數(shù)據(jù)傳到PC機(jī)處理,利用PC機(jī)進(jìn)行進(jìn)一步的分析處理與顯示。由于采用FPGA設(shè)計(jì),系統(tǒng)的復(fù)雜度大為降低,也方便升級(jí)與更新,同時(shí),可通過(guò)USB口對(duì)FPGA模塊進(jìn)行供電,極大的方便了工程師的調(diào)試,使該DPO具有很好的便攜性。

總體方案設(shè)計(jì)與論證

虛擬數(shù)字熒光示波器可以簡(jiǎn)單描述為這樣一個(gè)系統(tǒng):用戶(hù)通過(guò)PC機(jī)菜單設(shè)定采集觸發(fā)參數(shù),示波器根據(jù)用戶(hù)的設(shè)定采集數(shù)據(jù),并將采集到的數(shù)據(jù)做數(shù)字熒光處理,生成波形圖像經(jīng)DPX處理后經(jīng)USB傳送到PC機(jī)最后在液晶屏上顯示出來(lái),同時(shí),采集到的數(shù)據(jù)還可以做進(jìn)一步的分析處理。因此,示波器可以分成兩大部分,一部分負(fù)責(zé)監(jiān)控命令和波形、菜單的顯示;另一部分負(fù)責(zé)高速數(shù)據(jù)采集和數(shù)字熒光成像。

2.1總體框圖

根據(jù)上述分析,制定以下設(shè)計(jì)方案:該示波器采用FPGA架構(gòu),F(xiàn)PGA作為系統(tǒng)控制核心負(fù)責(zé)監(jiān)控PC機(jī)上發(fā)送過(guò)來(lái)的按鍵命令并根據(jù)當(dāng)前的工作狀態(tài)發(fā)送相應(yīng)的采集控制命令給采集模塊,同時(shí)還控制著數(shù)字熒光處理模塊生成的波形圖像和控制菜單,另一方面,由于其高速的特點(diǎn),用于實(shí)現(xiàn)高速數(shù)據(jù)采集系統(tǒng)以及數(shù)字熒光處理器。整體實(shí)現(xiàn)框圖如圖3所示。其中模數(shù)轉(zhuǎn)換器、時(shí)鐘電路和FPGA共同構(gòu)成了示波器的采集系統(tǒng),F(xiàn)PGA內(nèi)部實(shí)現(xiàn)DPX模塊,最后通過(guò)USB上傳到PC機(jī)處理顯示。

2.2信號(hào)調(diào)理電路

信號(hào)調(diào)理電路主要由衰減放大電路、耦合控制電路和直流偏置電路組成,由FPGA控制。

衰減放大電路調(diào)整輸入波形的幅度范圍,把不同幅度的信號(hào)進(jìn)行衰減或放大以適應(yīng)屏幕的顯示范圍,便于觀察和測(cè)量。

耦合控制電路控制輸入信號(hào)的耦合方式,分別為交流耦合和直流耦合,在直流耦合方式時(shí),信號(hào)的所有分量(交流和直流)都被采集顯示出來(lái),而在交流耦合方式時(shí),信號(hào)的直流分量被阻斷,只有交流分量被采集顯示出來(lái)。

直流偏置電路給信號(hào)加入直流分量,可以控制信號(hào)在屏幕中上下移動(dòng)。另外,示波器的輸入阻抗和模擬帶寬也由信號(hào)調(diào)理電路所決定。在本項(xiàng)目中,信號(hào)調(diào)理電路的輸入阻抗為50歐姆和1M歐姆可選。模擬帶寬為500MHz。

2.3數(shù)據(jù)采集系統(tǒng)

數(shù)據(jù)采集系統(tǒng)由到模數(shù)轉(zhuǎn)換器(Analog Digital Convertor, ADC)、時(shí)鐘芯片和FPGA中相關(guān)采集控制模塊組成。

2.3.1模數(shù)轉(zhuǎn)換

本設(shè)計(jì)選用e2v公司的AT84AD001B模數(shù)轉(zhuǎn)換器。其接口如圖4所示。該ADC為并行比較結(jié)構(gòu),速度快,但功耗大。其將兩路ADC集成在一個(gè)芯片中,每路ADC最高采樣率達(dá)1GHz,量化精度八比特,另外該芯片還支持交織采樣的功能,即同一芯片中的兩路ADC同時(shí)采集同一路模擬信號(hào),并且其采樣時(shí)鐘相位相反,將這兩路ADC的抽樣數(shù)據(jù)拼接起來(lái)可獲得2GSPS的最高采樣率。AT84AD001B的主要特性如下:

雙路ADC,每通道采樣率1GSPS,交織采樣模式下可達(dá)2GSPS;

輸出編碼為格雷碼和二進(jìn)制編碼可選,支持1:1和1:2復(fù)用輸出;

支持模擬輸入切換選擇,采樣時(shí)鐘選擇;

支持增益控制和零電平調(diào)節(jié);

采樣率1GSPS時(shí)誤比特率不超過(guò)

串行配置工作模式,源同步時(shí)鐘數(shù)據(jù)輸出;

2.3.2時(shí)鐘電路

在本項(xiàng)目中,采用了National Semiconductor公司的高精度時(shí)鐘管理芯片LMK03033C。其時(shí)鐘抖動(dòng)的均方根值為500飛秒。該芯片內(nèi)置低噪聲鎖相環(huán)并且支持8路時(shí)鐘同步輸出,支持串行配置。每路輸出時(shí)鐘都帶有可編程的分頻比、延遲調(diào)整和輸出選擇模塊,最高輸出時(shí)鐘頻率1GHz,且可在 0 至 2.25ns 的范圍內(nèi)調(diào)節(jié)輸出延時(shí),步進(jìn)為150ps。該芯片為高速ADC采集數(shù)據(jù)提供了精確的采樣時(shí)鐘。接口如圖5所示。

2.3.3采集控制和數(shù)據(jù)緩沖

模數(shù)轉(zhuǎn)換器輸出的高速數(shù)字信號(hào)在采集控制模塊的控制下寫(xiě)入數(shù)據(jù)緩沖區(qū),之后進(jìn)行數(shù)字熒光處理。如圖6所示。對(duì)于高速數(shù)字信號(hào)的控制和緩沖一般采用高速數(shù)字電路實(shí)現(xiàn)。一種方案是采用專(zhuān)用集成電路(ASIC)實(shí)現(xiàn)高速控制和數(shù)據(jù)緩沖。但是,專(zhuān)用集成電路成本極高,而且不能修改,一般用于經(jīng)過(guò)充分驗(yàn)證的,成熟的數(shù)字電路設(shè)計(jì)。另一種方案是采用高速FPGA。

現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array, FPGA)是一種含有可編程元件的設(shè)備,其速度一般比專(zhuān)用集成電路慢,但仍快于通用微處理器,適合做高速數(shù)據(jù)控制器。并且FPGA的可編程特性和低廉的價(jià)格適合項(xiàng)目初期開(kāi)發(fā)階段的原型驗(yàn)證。

示波器的采集控制和數(shù)據(jù)緩沖模塊是在FPGA中完成的,該模塊根據(jù)用戶(hù)設(shè)定的觸發(fā)條件,從無(wú)限長(zhǎng)的波形信號(hào)中截取用戶(hù)感興趣的部分來(lái)顯示。數(shù)據(jù)存儲(chǔ)系統(tǒng)的存取控制模塊也在FPGA中實(shí)現(xiàn)。

2.4數(shù)字熒光處理模塊

數(shù)字熒光處理單元的主要工作有如下幾個(gè)方面:

(1) 進(jìn)行波形的熒光顯示,達(dá)到模擬示波器的熒光顯示效果

數(shù)字熒光示波器將采集到的波形進(jìn)行熒光顯示,通過(guò)波形亮度顯示長(zhǎng)時(shí)間內(nèi)信號(hào)出現(xiàn)的頻度情況,完整地保留了多個(gè)通道波形顯示的亮度層次信息,達(dá)到模擬示波器的熒光顯示效果。在某一點(diǎn)的出現(xiàn)頻度越大,該點(diǎn)在熒光屏上顯示的亮度就越大;在某一點(diǎn)的出現(xiàn)頻度越小,該點(diǎn)在熒光屏上顯示的亮度就越小。

(2) 網(wǎng)格的調(diào)節(jié)控制

當(dāng)利用數(shù)字熒光示波器觀測(cè)信號(hào)時(shí),為了觀測(cè)精確,需要熒光屏在顯示波形信號(hào)的同時(shí)顯示網(wǎng)格。

(3) 波形熒光顯示亮度的調(diào)節(jié)控制

當(dāng)利用數(shù)字熒光示波器觀測(cè)信號(hào)時(shí),顯示的波形亮度會(huì)直接影響到觀測(cè)效果,過(guò)亮或者過(guò)暗的波形,會(huì)使波形的細(xì)節(jié)分辨不清,都不利于用戶(hù)觀測(cè)。因此,需要加入波形熒光顯示亮度的調(diào)節(jié)功能,使用戶(hù)可以調(diào)節(jié)熒光屏上顯示的波形亮度,有利于波形觀測(cè)。

(4) 波形消隱百分比的調(diào)節(jié)控制

當(dāng)利用數(shù)字熒光示波器觀測(cè)信號(hào)時(shí),有時(shí)需要使波形在屏幕上滯留一定的時(shí)間后再消失,或者有時(shí)需要將出現(xiàn)的波形永遠(yuǎn)顯示在熒光屏上,如毛刺等偶發(fā)信號(hào)。因此,需要加入波形消隱百分比的調(diào)節(jié)功能,使用戶(hù)可以調(diào)節(jié)波形在熒光屏上顯示的持續(xù)時(shí)間。

(5) 多通道波形的熒光顯示及通道優(yōu)先級(jí)的控制

當(dāng)示波器同時(shí)觀測(cè)多個(gè)通道時(shí),不同的通道應(yīng)該顯示為不同的顏色以示區(qū)分。同時(shí),多個(gè)通道同時(shí)顯示時(shí),應(yīng)有優(yōu)先級(jí)的區(qū)分,即哪一個(gè)通道應(yīng)該顯示在最上層。用戶(hù)應(yīng)該能夠通過(guò)調(diào)節(jié)控制,將最關(guān)心的通道波形顯示在所有波形的最上層,便于波形觀測(cè)。

(6) 滿(mǎn)足數(shù)字熒光示波器實(shí)時(shí)顯示的要求

示波器是一種實(shí)時(shí)測(cè)量?jī)x器,需要滿(mǎn)足波形實(shí)時(shí)顯示的要求。因此在進(jìn)行波形的熒光顯示時(shí),要盡量提高處理速度,以提高實(shí)時(shí)性。

本章將首先詳細(xì)介紹數(shù)字熒光處理單元的設(shè)計(jì)思想,并在此基礎(chǔ)上,具體介紹數(shù)字熒光處理單元的設(shè)計(jì)及實(shí)現(xiàn)。

由需求分析可知,為了實(shí)現(xiàn)波形的熒光顯示,首先需要定時(shí)一段時(shí)間,將在這段時(shí)間內(nèi)采集到的若干次波形進(jìn)行疊加,并記錄所有波形點(diǎn)出現(xiàn)的頻度。因此數(shù)字熒光處理單元內(nèi)部需要設(shè)計(jì)一個(gè)存儲(chǔ)器,以記錄一段時(shí)間內(nèi)所有波形點(diǎn)出現(xiàn)的頻度,稱(chēng)之為模擬熒光屏存儲(chǔ)器。同時(shí),需要一個(gè)波形疊加處理模塊,完成將 若干次波形進(jìn)行疊加后的頻度存儲(chǔ)到模擬熒光屏存儲(chǔ)器的功能。

然后,當(dāng)定時(shí)時(shí)間到時(shí),將之前疊加儲(chǔ)存在模擬熒光屏存儲(chǔ)器中的所有單元信息讀出,經(jīng)過(guò)顏色轉(zhuǎn)換形成一幀波形圖像送顯示器進(jìn)行顯示;同時(shí)將讀出的模擬熒光屏存儲(chǔ)器中的所有單元信息進(jìn)行消隱處理,再寫(xiě)回模擬熒光屏存儲(chǔ)器。

送到顯示器進(jìn)行顯示的一幀波形圖像是一幅和顯示屏的波形顯示區(qū)具有同樣大小和分辨率的像素圖像。它的原始信息是存儲(chǔ)在模擬熒光屏存儲(chǔ)器中的。模擬熒光屏存儲(chǔ)器實(shí)際上是一個(gè)二維的動(dòng)態(tài)數(shù)據(jù)庫(kù)。數(shù)據(jù)庫(kù)的地址單元是與波形顯示區(qū)的像素點(diǎn)一一對(duì)應(yīng)的。因此數(shù)據(jù)庫(kù)的大小由數(shù)字熒光示波器的熒光屏波形顯示區(qū)的總像素點(diǎn)確定。橫軸對(duì)應(yīng)于時(shí)間軸,縱軸對(duì)應(yīng)幅度軸。規(guī)定顯示區(qū)的左下角對(duì)應(yīng)數(shù)據(jù)庫(kù)的起始單元,其后的數(shù)據(jù)單元按對(duì)應(yīng)屏幕從左到右,從下到上的次序排列。

由上可知,整個(gè)數(shù)字熒光處理單元應(yīng)包括五個(gè)子單元協(xié)同工作:波形數(shù)據(jù)緩沖存儲(chǔ)器、模擬熒光屏存儲(chǔ)器、波形激活處理模塊、波形消隱處理模塊和顏色轉(zhuǎn)換處理模塊等,它們共同完成多路波形的數(shù)字熒光處理,并每隔一定時(shí)間形成一幀波形圖像輸出給顯示器,同時(shí)進(jìn)行一次消隱處理。各個(gè)子單元之間的聯(lián)系如圖8所示。

2.5 PC機(jī)部分

PC機(jī)與FPGA經(jīng)USB進(jìn)行數(shù)據(jù)交互(DPX數(shù)據(jù)與控制信息),PC機(jī)通過(guò)USB給FPGA供電,DPX數(shù)據(jù)經(jīng)USB傳到PC機(jī)后通過(guò)LABwindows處理顯示。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論