FPGA和復位電路相比大家應該都比較熟悉,那么對于FPGA怎么搭復位電路你知道嗎?本文介紹的就是關于FPGA怎么搭復位電路以及fpga復位電路設計方案。

復位電路

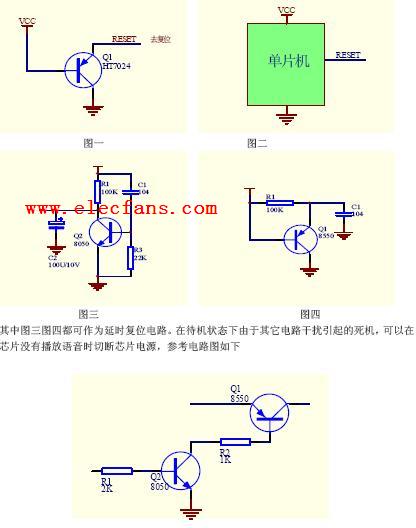

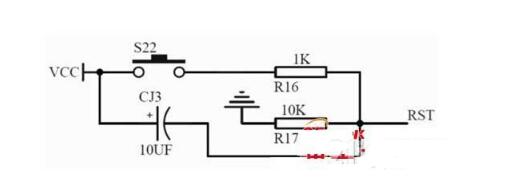

為確保微機系統中電路穩定可靠工作,復位電路是必不可少的一部分,復位電路的第一功能是上電復位。一般微機電路正常工作需要供電電源為5V±5%,即4.75~5.25V。由于微機電路是時序數字電路,它需要穩定的時鐘信號,因此在電源上電時,只有當VCC超過4.75V低于5.25V以及晶體振蕩器穩定工作時,復位信號才會撤除,微機電路開始正常工作。

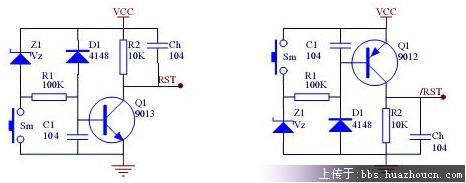

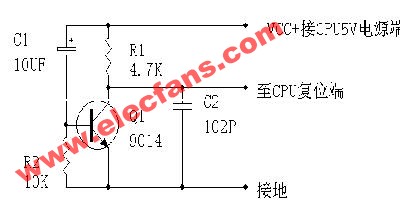

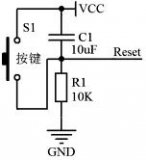

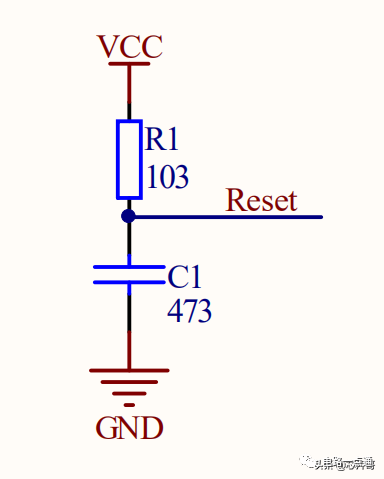

復位電路,就是利用它把電路恢復到起始狀態。就像計算器的清零按鈕的作用一樣,以便回到原始狀態,重新進行計算。和計算器清零按鈕有所不同的是,復位電路啟動的手段有所不同。一是在給電路通電時馬上進行復位操作;二是在必要時可以由手動操作;三是根據程序或者電路運行的需要自動地進行。復位電路都是比較簡單的大都是只有電阻和電容組合就可以辦到了。再復雜點就有三極管等等配合程序來進行了。

FPGA

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

系統設計師可以根據需要通過可編輯的連接把FPGA內部的邏輯塊連接起來,就好像一個電路試驗板被放在了一個芯片里。一個出廠后的成品FPGA的邏輯塊和連接可以按照設計者而改變,所以FPGA可以完成所需要的邏輯功能。

FPGA一般來說比ASIC(專用集成電路)的速度要慢,實現同樣的功能比ASIC電路面積要大。但是他們也有很多的優點比如可以快速成品,可以被修改來改正程序中的錯誤和更便宜的造價。廠商也可能會提供便宜的但是編輯能力差的FPGA。因為這些芯片有比較差的可編輯能力,所以這些設計的開發是在普通的FPGA上完成的,然后將設計轉移到一個類似于ASIC的芯片上。另外一種方法是用CPLD(Complex Programmable Logic Device,復雜可編程邏輯器件)。

FPGA怎么搭復位電路

異步復位:復位信號和系統時鐘信號的觸發可以在任何時刻。二者相互獨立。?

同步復位:在系統時鐘信號的觸發下,復位信號有效。?

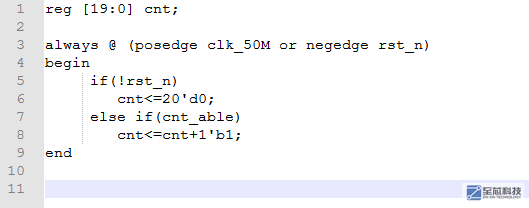

用verilog表示會更明顯:

// 異步復位

reg a;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

a <= 'd0;

else

a <= ~a;

end

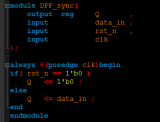

//同步復位

reg b;

always @ (posedge clk)? begin

if(!rst_n)

b <= 'd0;

else? ??

b <= ~b;

end

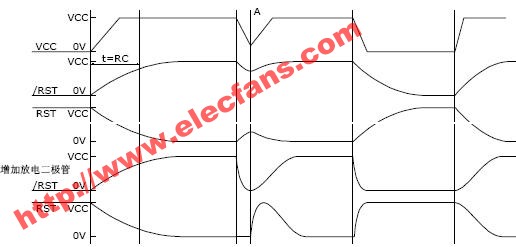

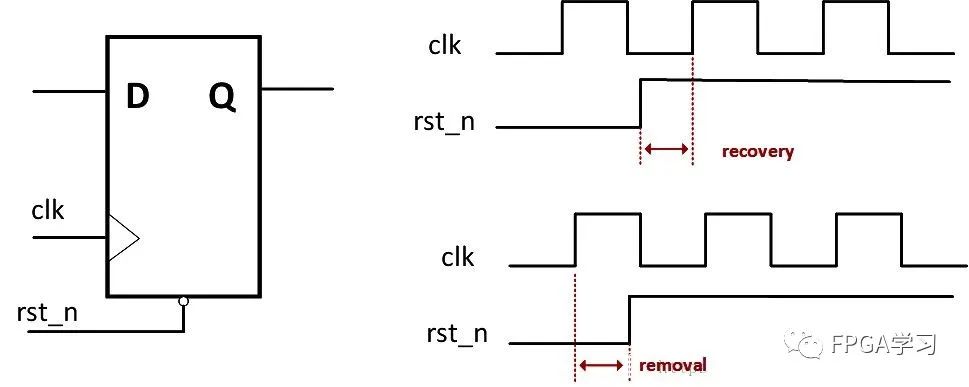

如果復位信號的撤銷發生在系統時鐘的建立和保持時間這段時間內,系統此時檢測到復位信號的狀態就處在一個亞穩態,無法確定是0還是1。就有可能造成系統工作不同步的問題。

異步復位會影響寄存器的recovery時間,引起設計的穩定性問題,尤其對于狀態機的無意識復位,將導致進入不確定的狀態。?

同步復位最主要的問題是對于不帶同步復位專用端口的器件會增加額外的邏輯資源。?

//異步復位、同步釋放

reg rst_nr1;

reg rst_nr2;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

rst_nr1 <= 'd0;

else

rst_nr1 <= 1'b1;

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

rst_nr2 <= 'd0;

else

rst_nr2 <= rst_nr1;

end

簡單分析一下這個電路,當異步復位發生,rst_nr2直接拉低為0,并且由于rst_nr2是在時鐘沿的作用下對rst_nr1進行采樣,所以當rst_nr2的置1是和時鐘沿同步的。也就是異步復位、同步釋放。然后用信號rst_nr2作為系統復位時鐘,就不發生亞穩態現象。

但是在我的理解看來,這兩個觸發器仍然是采用rst_n作為復位信號,所以必然會有亞穩態的現象發生,即rst_nr2還是 有可能在不應該復位的時間點復位,但是由rst_nr2作為系統復位信號的后級電路不會發生系統工作不同步的現象。

fpga復位電路設計方案

對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局異步復位/置位資源和采用內部復位。上述方法可有效提高FPGA復位的可靠性。

?

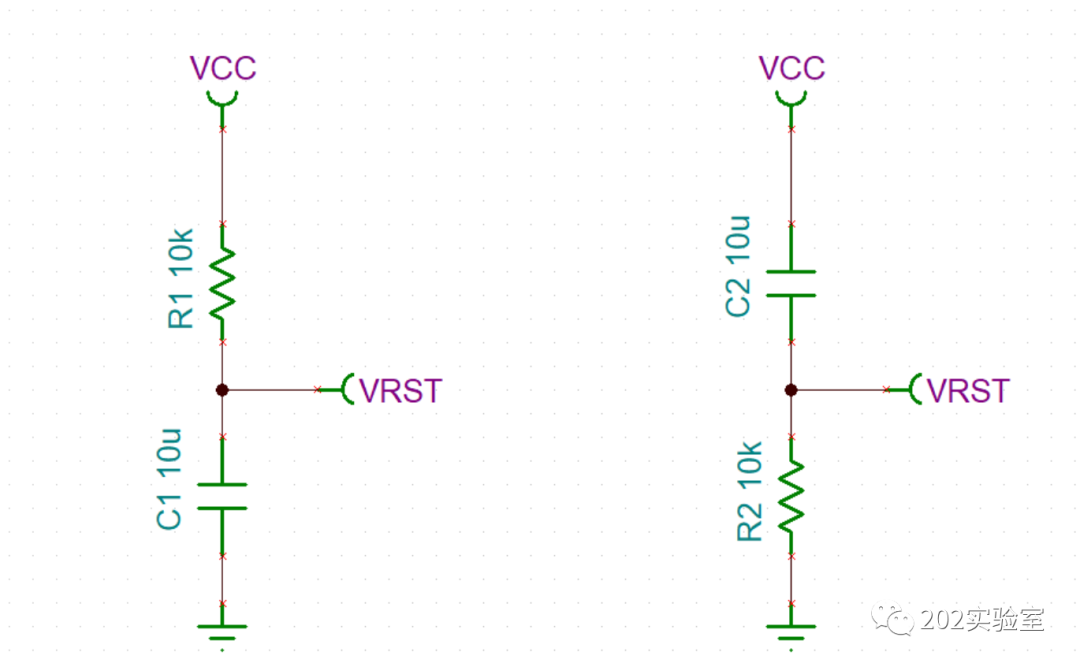

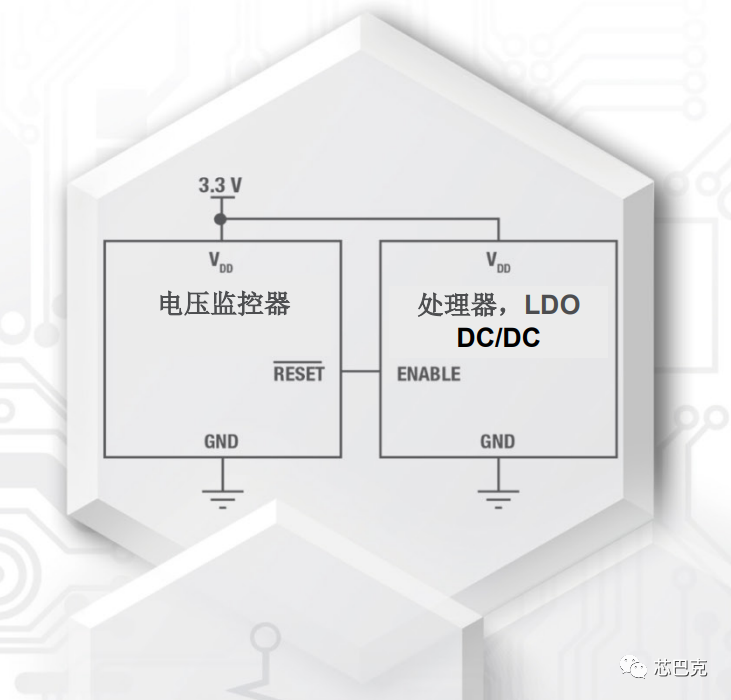

對FPGA芯片而言,在給芯片加電工作前,芯片內部各個節點電位的變化情況均不確定、不可控,而這種不確定且不可控的情況會使芯片在上電后的工作狀態出現錯誤。因此,在FPGA的設計中,為保證系統能可靠進進入工作狀態,以及避免對FPGA輸出關聯的系統產生不良影響,FPGA上電后要進行復位,且為了消除電源開關過程中引起的抖動影響,復位信號需在電源穩定后經過一定的延時才能撤銷,FPGA的復位信號需保證正確、穩定、可靠。

在FPGA的設計中,多數情況下復位電路的功能雖能夠正常完成,但電路并未得到精確合理的設計,仍存在可靠性設計缺陷。為確保系統復位的可靠性,有必要對FPGA復位的可靠性設計方法進行研究。

1 復位設計方法分類

復位的目的是在仿真時將設計強制定位在一個可知狀態,合理選擇復位方式是電路設計的關鍵。根據與系統時鐘域的關系,復位電路可分為同步復位和異步復位。同步復位是指復位信號只在時鐘沿到來時,才有效。否則,無法完成對系統的復位工作。異步復位是指無論時鐘沿是否到來,只要復位信號有效,使對系統進行復位。

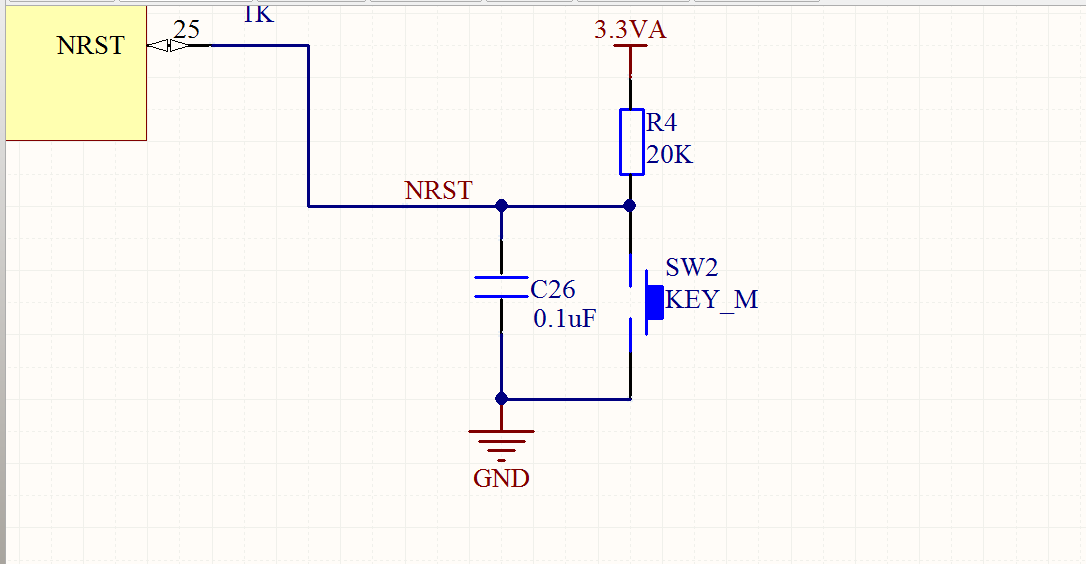

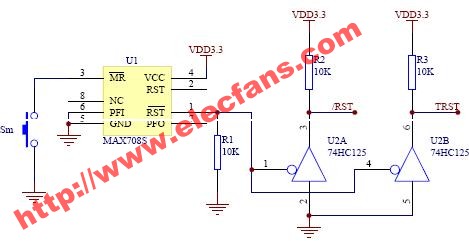

根據是否存在外部復位端口,復位電路又可分為外部復位和內部復位。外部復位是指復位信號主要來自外部引腳的輸入,如復位按鈕、電源模塊輸出等。內部復位信號則是主要由FPGA內部電路產生。

2 復位設計方法的比較

2.1 同步復位與異步復位

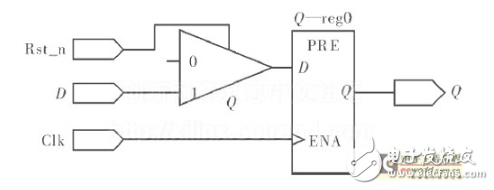

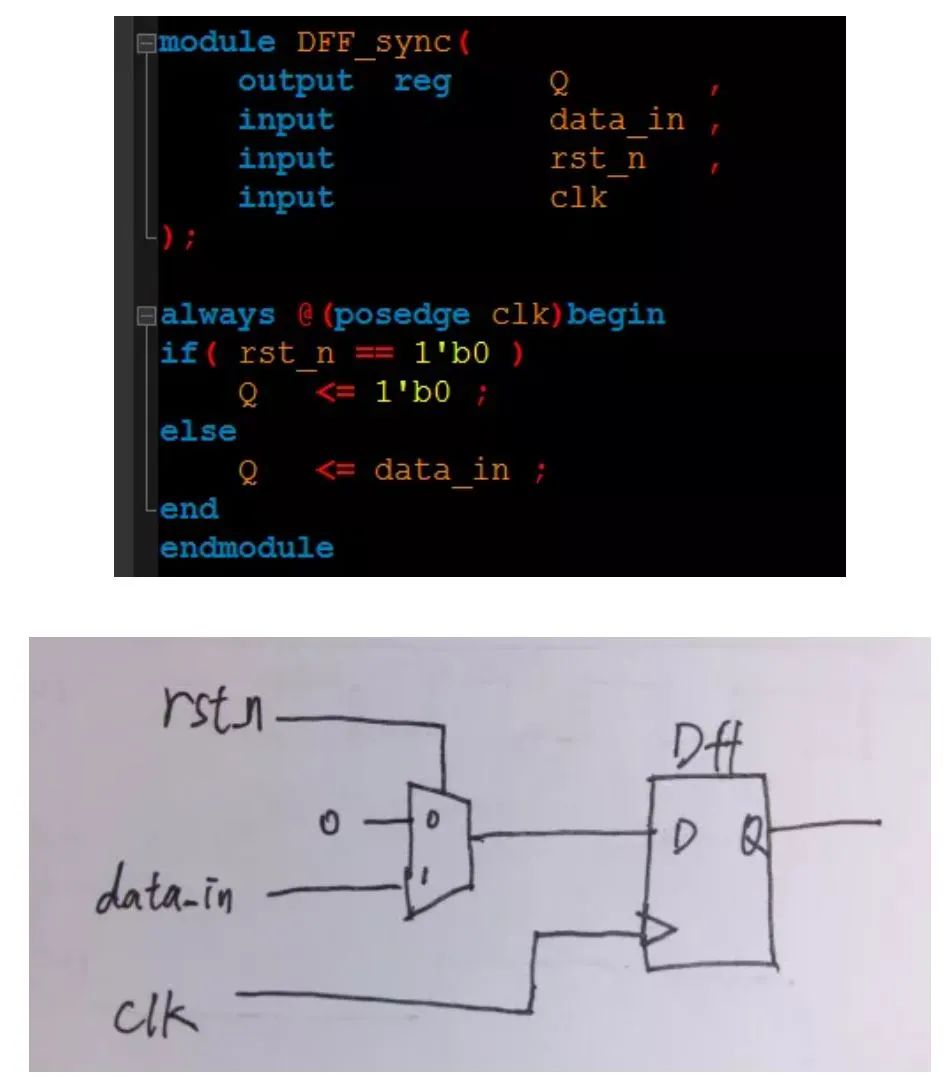

2.2.1 同步復位

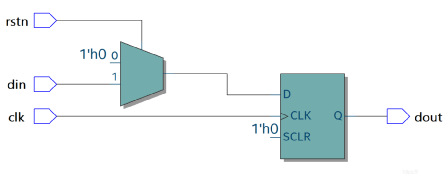

指定同步復位時,always的敏感表中僅有一個時鐘沿信號,只有當時鐘沿采集到同步復位的有效電平時,才會在時鐘沿到達時刻進行復位操作。若目標器件或可用庫中的觸發器本身包含同步復位端口,則在實現同步復位電路時可直接調用同步復位端。然而多數目標器件的觸發器本身并不包含同步復位端口,需使復位信號與輸入信號組成某種組合邏輯,然后將其輸入到寄存器的輸入端。為了提高復位電路的優先級,通常在電路描述時使用帶有優先級的if…else結構,復位電路在第一個if下描述,其他電路在else或else…if分支中描述。復位電路綜合后的RTL圖如圖1所示。

同步復位電路圖

根據同步電路的特點,其電路優點有:(1)同步復位有利于基于周期機制的仿真器進行仿真。(2)使用同步復位可設計100%的同步時序電路,有利于時序分析,其綜合結果的頻率較高。(3)同步復位僅在時鐘的有效沿生效,可有效避免因毛刺造成的亞穩態和錯誤。毛刺信號是由FPGA內部結構特征決定的,同步復位在進行復位和釋放復位信號時,僅當時鐘沿采到復位信號電平變化時進行相關操作,若復位信號樹的組合邏輯出現了某種毛刺,此時時鐘沿采到毛刺的概率較低,由此通過時鐘沿采樣,可有效過波復位電路組合邏輯產生的毛刺,增強了電路穩定性。

同步復位的缺點有:(1)多數目標器件庫的觸發器本身并不包含同步復位端口,使用同步復位會增加更多邏輯資源。(2)同步復位的最大問題在于必須保證復位信號的有效時間,需要一個脈寬延展器以確保復位信號有一定脈沖寬度,由此才能保證所有觸發器均能有效復位。由于同步復位僅當時鐘沿采到復位信號時才會進行復位操作,所以其信號的持續時間要大于設計的最長時鐘周期,以保證所有時鐘的有效沿都能采樣到同步復位信號。事實上,僅保證同步復位信號的持續時間大于最慢的時鐘周期是不夠的,設計中還需考慮到同步復位信號樹通過所有相關組合邏輯路徑時的延時,以及由于時鐘布線產生的偏斜。只有同步復位大于時鐘最大周期,加上同步信號穿過的組合邏輯路徑延時和時鐘偏斜延時,才能確保同步復位的可靠。

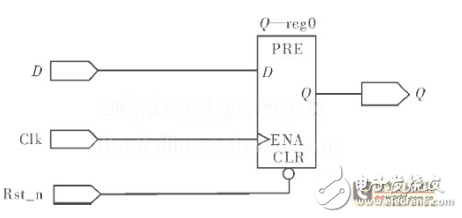

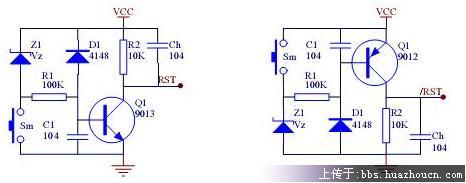

2.2.2 異步復位

指定異步復位時,只需在always的敏感表中加人復位信號的有效沿即可,當復位信號有效沿到達時,無論時鐘沿是否有效,復位均會立即發揮其功能。

大多數目標器件和ASIC庫的觸發器均包含異步復位端口,異步復位會直接接人觸發器的異步復位端口,綜合后的RTL圖如圖2所示。

異步復位電路圖

根據異步電路的特點,異步復位的優點有:(1)由于多數目標器件庫的觸發器都包含異步復位端口,異步復位會節約邏輯資源。(2)異步復位設計簡單。(3)對于多數FPGA,均有專用的全局異步復位/置位資源(GSR,Global Set Reset),還可使用GSR資源,異步復位到達所有寄存器的偏斜最小。 異步復位的缺點如下:(1)異步復位的作用和釋放與時鐘沿并無直接關系,異步復位生效時問題并不明顯;但當釋放異步復位時,若異步復位信號釋放時間和時鐘的有效沿到達時間幾乎一致,則容易造成觸發器輸出為亞穩態,形成邏輯錯誤。(2)若異步復位邏輯樹的組合邏輯產生了毛刺,則毛刺的有效沿會使觸發器誤復位,造成邏輯錯誤。

2.3 外部復位和內部復位

外部復位,復位信號主要來自外部引腳的輸人。復位信號在電路板上可能會受到來自其他線路的串擾,因此可能產生毛刺,在無需復位系統時,毛刺信號可能導致系統誤復位。

內部復位,FPGA上電配置完成后,由FPGA內部電路產生復位信號,復位信號與時鐘同步。通常內部復位的設計方法是:設計一個初始值為0X0000的SRL16,將其輸人接高電平,輸出作為復位信號。

3 復位可靠性設計方法

3.1 消除復位信號上的毛刺

在系統設計中,若采用低有效復位信號,可按照圖3所示方法對復位信號中的毛刺進行消除。延時器件對數據進行延時的長度決定復位毛刺消除電路所能避免的毛刺長度,而延時器件的延時長度也決定需要提供有效復位信號的最短時間。

如果復位信號高有效,則將圖3中的或門改為與門使用。為更好地消除毛刺,可在復位毛刺消除電路后再加上寄存器對復位信號進行時鐘同步。在通常復位電路的設計中,毛刺的長度一般情況下>1個時鐘周期,<16個時鐘周期。為節省資源,延時器件通常選用SRL16。SRL16可設置初始值,但不帶復位功能16bit移位寄存器,能夠通過A0~A3的4根地在線選擇從第幾個寄存器輸出。通常將其作為一個普通的16bit移位寄存器使用。

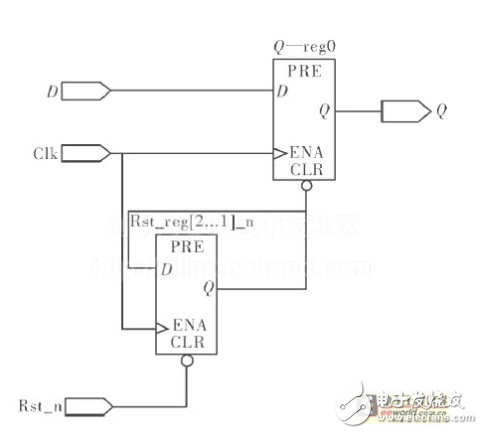

3.2 異步復位同步釋放

在有些應用中,復位信號需要在時鐘尚未給出或不穩定的情況下傳到后級,在時鐘穩定之后,再撤去復位信號。此時需使用異步復位來實現。由于異步復位時,時鐘和復位關系的不確定性,易造成觸發器輸出亞穩態,引起邏輯錯誤。為確保其復位的可靠性,通常采用異步復位,同步釋放的方式。

所謂異步復位,同步釋放就是在復位信號到達時不受時鐘信號的同步,而是在該信號釋放時受時鐘信號的同步。通過一個復位信號綜合器便可實現異步復位,同步釋放。綜合后的RTL圖如圖3所示,其仿真結果表明該電路能有效的實現復位及脫離復位。

異步復位、同步釋放電路圖

?

3.3 采用專用全局異步復位/置位資源

全局異步復位/置位資源的主要作用是對系統中存在的所有觸發器、鎖存器、查找表單元的輸出寄存器進行復位,不會占有額外的布線資源。使用GSR資源,異步復位到達所有寄存器的偏斜最小。

3.4 采用內部復位的設計方法

在無需復位信號先于時鐘信號產生的應用中,為避免外部復位毛刺的影響、異步復位電路可能引起的亞穩態以及減少資源的使用率,可通過FPGA產生內部復位,然后采用異步的方式對其的內寄存器進行復位。由于該復位信號由FPGA內部產生,不會因外部干擾而產生毛刺,同時又與時鐘同步,不存在因異步復位導致的亞穩態現象,因此可確保系統可靠復位。

結語

FPGA的可靠復位是保證系統能夠正常工作的必要條件,本文對FPGA設計中常用的復位設計方法進行了分類、分析和比較,并針對各種復位方式的特點,提出了如何提高復位設計可靠性的方法。在工程實踐中,上述方法可以有效減少或消除FPGA復位所產生的錯誤。

關于FPGA復位電路的介紹就到這里了,希望通過本文能讓你對FPGA復位電路的整體架構有更深的理解,如有不足之處歡迎指正。

電子發燒友App

電子發燒友App

評論