隨著摩爾定律放緩,Chiplet SoC近年來被視為后摩爾時代推動下一代芯片革新的關(guān)鍵技術(shù)。芯片巨頭AMD就憑借著在Chiplet上的投入,在過去幾年大大拉近了與英特爾在數(shù)據(jù)中心處理器領(lǐng)域的差距。特斯拉引領(lǐng)了智能汽車電子電器架構(gòu)由域內(nèi)集成演變?yōu)榭缬蛉诤霞爸醒胗嬎慵軜?gòu)。近期出現(xiàn)的AIGC促使汽車產(chǎn)業(yè)將智能化向更廣泛的應(yīng)用領(lǐng)域發(fā)展。智能汽車對算力需求的飆升使得行業(yè)迫切需要平臺化計算硬件來實現(xiàn)降本增效,Chiplet異構(gòu)集成技術(shù)無疑是打破后摩爾時代算力瓶頸的關(guān)鍵。全球多家車廠已經(jīng)在使用Chiplet技術(shù)進行下一代芯片產(chǎn)品的研發(fā),實現(xiàn)高性能、可拓展的芯片平臺,從而覆蓋不同車型、不同配置的算力需求。英偉達等芯片廠商最近也宣布了Chiplet在車載領(lǐng)域的一些戰(zhàn)略部署。但Chiplet在車載領(lǐng)域的實踐不是一蹴而就的,誰能拿出既滿足車載大算力需求,又滿足低成本,還滿足車規(guī)要求,更能為客戶創(chuàng)造差異化價值的芯片方案,誰才能夠站在后摩爾時代半導體行業(yè)的舞臺中心。

決定Chiplet產(chǎn)品性價比和可靠性的關(guān)鍵技術(shù)之一:Chiplet D2D片間互連技術(shù)

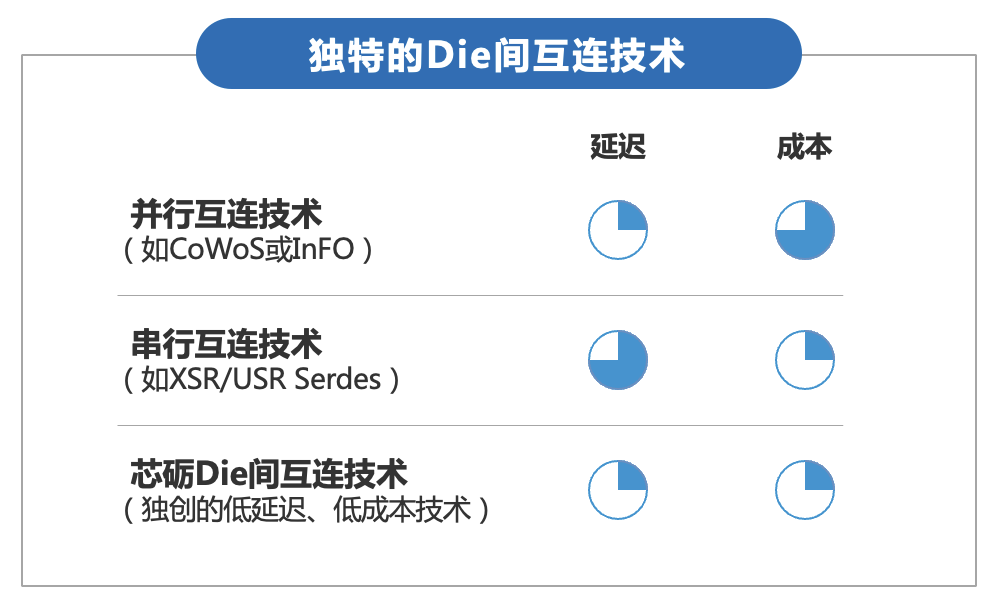

從理論上來說,Chiplet就像是搭建樂高積木,通過將單芯片拆分成若干個較小的裸片(Die),再將其互連并封裝成一個異構(gòu)集成芯片,從而達到甚至超越采用先進工藝芯片的性價比。但是具體到車載領(lǐng)域,Chiplet還面臨著諸多挑戰(zhàn),其中芯片架構(gòu)和互連方式是最需攻克的兩大難關(guān)。其中芯片架構(gòu)上的挑戰(zhàn)在于:將原來在單芯片上所實現(xiàn)的功能拆分為多顆Chiplet共同去完成時,Chiplet之間(Die-to-Die,簡稱D2D)通信效率的降低會造成整體性能下降。如何找到最佳拆分方式,將性能下降控制在最低程度,是芯片架構(gòu)設(shè)計的關(guān)鍵。而互連方式的挑戰(zhàn)也同樣在于:如何在滿足市場對于成本、可靠性要求的前提下,盡量減少Chiplet D2D通信效率的降低。Chiplet D2D互連技術(shù)根據(jù)工作方式的不同主要可分為并行互連及串行互連,以下是兩者的對比:

并行互連

先進封裝:低延遲,高成本

并行互連不僅降低了兩顆芯片之間的延遲,還可以通過增加總線寬度來提升帶寬。然而,并行互連面臨的現(xiàn)實瓶頸是制造成本偏高。究其原因,是因為并行互連的I/O連接線數(shù)量較大,需要依賴諸如CoWoS、InFO一類的先進封裝技術(shù),而這會導致成本的巨大提升,也對可靠性提出了更高的挑戰(zhàn)。

串行互連

傳統(tǒng)封裝:高延遲,低成本

串行互連技術(shù)大大減少了芯片之間通信所需的I/O連接線總數(shù),因此不需要依賴于先進封裝,可以實現(xiàn)相對較低的成本,也相對比較容易實現(xiàn)更高的可靠性。但串行互連方式通常會引起額外約50-150 ns的延遲,不能滿足實時性要求較高的應(yīng)用需求。

在智能汽車這樣一種對性能(尤其是實時性)、成本和可靠性都非常敏感的應(yīng)用場景下,如果采用常見的串行互連方式及傳統(tǒng)封裝技術(shù),雖然可以降低成本和可靠性風險,但顯然在通信延遲性能方面又遠達不到實時性要求;而如果采用所謂的先進封裝技術(shù)實現(xiàn)并行互連,其高昂的成本和未經(jīng)車規(guī)檢驗的可靠性等風險都會讓人望而卻步。在滿足可靠性前提下,做好性能與成本之間的平衡,是Chiplet D2D互連方式的制勝關(guān)鍵。

為車載中央計算而生,芯礪智能獨創(chuàng)Chiplet D2D互連IP流片

芯礪智能全自研的Chiplet D2D 互連IP兼有并行互連技術(shù)的高帶寬、低延遲和串行互連技術(shù)的高可靠性、低成本的優(yōu)勢。該互連IP的端到端延遲小于5 ns,和片內(nèi)總線延遲在一個量級,可以很好地支持不同處理器之間,以及處理器和存儲器之間的低延遲互連的要求。另一方面,當前先進封裝還未能完全符合車規(guī)要求,而芯礪智能Chiplet D2D 互連IP支持車規(guī)級傳統(tǒng)封裝,可以廣泛應(yīng)用于車載領(lǐng)域。

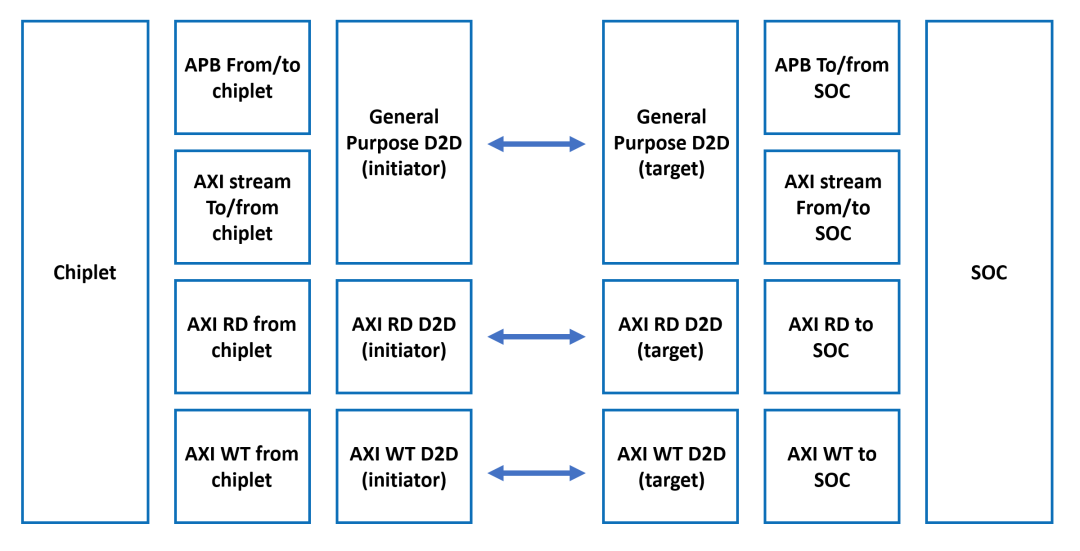

圖1 Chiplet D2D 互連IP框圖

芯礪智能的Chiplet D2D互連IP采用專利性的設(shè)計,通過一種用于片間互連的總線流水線性結(jié)構(gòu),做到了以較小的實際位寬來實現(xiàn)片間高帶寬及低延遲的互連,從而可以擺脫對先進封裝的依賴,用低成本的傳統(tǒng)封裝來實現(xiàn)片間互連。基于傳統(tǒng)封裝的Chiplet D2D互連技術(shù)更易于實現(xiàn)AEC-Q100的車規(guī)認證,從而達成高性價比、高可靠性的解決方案。

圖2 芯礪Chiplet D2D核心優(yōu)勢:

并行性能,串行成本

得益于這些領(lǐng)先的設(shè)計,芯礪智能的Chiplet D2D互連 IP可廣泛應(yīng)用于各種需要高帶寬、高可靠性、低延遲、低成本的應(yīng)用場景,包括自動駕駛、高性能邊緣計算、機器人、人工智能等領(lǐng)域。以先進的駕駛輔助系統(tǒng)和自動駕駛領(lǐng)域為例,這樣的應(yīng)用場景對系統(tǒng)的實時性和安全性有著非常高的要求。芯礪智能的Chiplet D2D互連 IP為這些系統(tǒng)提供了低延遲且高性價比的互連解決方案,可以加速信號處理流程,提高系統(tǒng)的反應(yīng)速度。

本月初,芯礪智能全球首個符合ASIL-D功能安全等級的車規(guī)級Chiplet D2D互連IP流片。值得一提的是,該 IP所采用的核心技術(shù)已經(jīng)獲得了由美國專利及商標局(United States Patent and Trademark Office, USPTO)授予的獨家專利,國內(nèi)的專利認證流程也正如火如荼地進行著。

Chiplet D2D互連技術(shù)應(yīng)用于車載領(lǐng)域的功能安全挑戰(zhàn):ASIL-D

對于汽車芯片,ISO 26262是一個不能繞過的關(guān)鍵標準。作為ISO 26262標準用于評估安全的等級,ASIL將汽車電子系統(tǒng)安全性能分為四個等級:ASIL-A、ASIL-B、ASIL-C 和 ASIL-D。其中,ASIL-D 表示最高安全等級。Chiplet D2D互連技術(shù)達到ASIL-D的級別確保能夠滿足復(fù)雜系統(tǒng)的安全性和可靠性要求。從失效影響角度,Chiplet D2D互連技術(shù)本身的失效會提升系統(tǒng)失效風險,而ASIL-D的Chiplet D2D互連技術(shù)可以完整覆蓋互連的失效,極大的降低系統(tǒng)風險。此外,ASIL-D的Chiplet D2D互連技術(shù)可以應(yīng)用到不同等級的安全域,而Chiplet D2D互連技術(shù)的糾錯、重傳機制更是可以有效提升系統(tǒng)的可用性。

達到ASIL-D級別的Chiplet D2D互連技術(shù)在設(shè)計、開發(fā)、測試和驗證等方面都有非常嚴格的要求,這需要嚴格的安全管理體系、完備的安全架構(gòu)分析和細致的安全技術(shù)實施等多方面能力的支撐。以下是達到ASIL-D安全等級的 Chiplet D2D互連技術(shù)的關(guān)鍵點:

安全分析和架構(gòu)設(shè)計: 對Chiplet D2D互連技術(shù)的具體功能,失效模式和安全機制完整的分析是ASIL-D架構(gòu)的基礎(chǔ)。這需要IP架構(gòu)師,安全架構(gòu)師通過FTA,F(xiàn)MEA等方式對IP架構(gòu)進行詳盡的失效模式分析、影響分析,據(jù)此設(shè)計高覆蓋率的安全機制,并通過FMEDA確認整體覆蓋率(芯礪智能的Chiplet D2D互連 IP的SPFM=99.072%, LFM=90.641%)。此外,在架構(gòu)設(shè)計時,不僅需要考慮高覆蓋率的安全機制,也需要考慮安全機制對延遲、面積,驗證,測試,易用性的影響,最終達成一個高效的IP架構(gòu)。

故障后處理設(shè)計:IP若發(fā)生故障,系統(tǒng)通常需要進入復(fù)雜的故障恢復(fù)流程(系統(tǒng)重啟等),從而導致系統(tǒng)在一段時間不可用,大大降低整體系統(tǒng)的可用性。為了提升整體系統(tǒng)的可用性,Chiplet D2D互連技術(shù)要具備高容錯性,故障后處理需盡量考慮快速故障修復(fù)。在整個Chiplet D2D互連技術(shù)的架構(gòu)中,需考慮多種糾錯技術(shù),包括ECC、重傳等機制,并且和原有功能架構(gòu)形成良好的耦合。

驗證:Chiplet D2D互連技術(shù)的驗證應(yīng)經(jīng)過仔細規(guī)劃和驗證。這涉及到總線、安全機制和故障后處理等多方面的協(xié)同驗證。同時,也需要在各種不同的驗證平臺進行完備的故障注入測試,比如在RTL和門級仿真時候通過工具進行故障注入測試,在FPGA平臺進行的軟件故障注入測試,在流片回片后的互連故障注入測試等。

安全管理:ASIL-D的安全管理流程對于確保Chiplet D2D互連技術(shù)的安全性至關(guān)重要,這包含了完備的安全計劃和每個安全活動的高質(zhì)量完成。其中,每個安全要求應(yīng)在安全計劃中被清晰定義和記錄,安全要求、設(shè)計和驗證活動需被文檔化,同時要確保安全活動中文檔的可追溯性。

安全檔案:完整的安全檔案可以協(xié)助客戶的產(chǎn)品順利通過功能安全認證。這包括完備、規(guī)范的安全分析交付件(FTA/FMEA/FMEDA),完整、易用的安全手冊,以及第三方權(quán)威機構(gòu)認證證書。

今年6月初,芯礪智能Chiplet D2D 互連 IP獲得了全球首個車規(guī)級ISO26262 ASIL-D Ready認證,該項認證標志著芯礪智能Die-to-Die Interconnect IP滿足最高功能安全要求,可以應(yīng)用在安全性要求最高的車載場景,是智能汽車算力平臺芯片研發(fā)的重要里程碑,也開啟了芯礪智能在智能汽車芯片市場的新階段。

圖3 ISO26262 ASIL-D Ready 認證

接棒后摩爾時代,賦能汽車“芯”生態(tài)

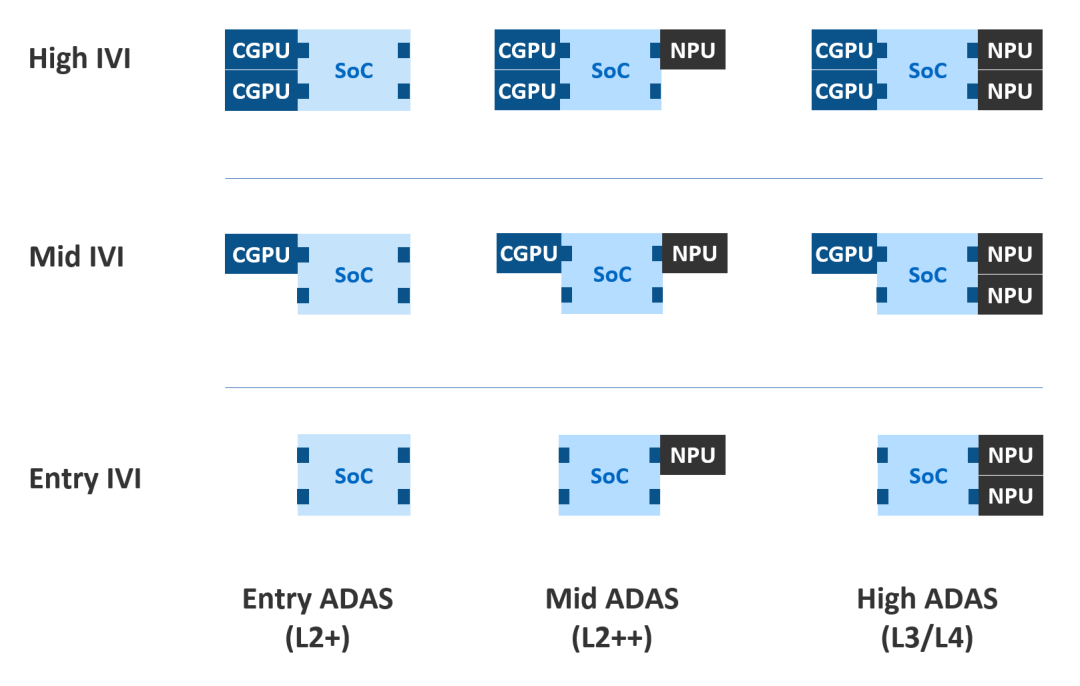

隨著摩爾定律逼近極限,芯片設(shè)計日益復(fù)雜。芯礪智能認為,公司的Chiplet D2D 互連IP不僅為系統(tǒng)設(shè)計人員提供了一種靈活可擴展的互連方案,還可以幫助客戶降低研發(fā)和系統(tǒng)成本、加速產(chǎn)品開發(fā)周期、提升敏捷迭代能力,并實現(xiàn)更強大的平臺化產(chǎn)品開發(fā)能力。

圖4 Chiplet賦能:用一個平臺覆蓋多個應(yīng)用場景

展望未來, 芯礪智能將與合作伙伴一同持續(xù)創(chuàng)新和突破,打造開放和共贏的生態(tài)圈,芯篤行遠、砥礪前行,共創(chuàng)智能汽車輝煌芯世界。

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評論